定義:信號完整性(Signal Integrity,簡稱SI)是指在信號線上的信號質量。差的信號完整性不是由某一單一因素導致的,而是板級設計中多種因素共同 引起的。當電路中信號能以要求的時序、持續時間和電壓幅度到達接收端時,該電路就有很好的信號完整性。當信號不能正常響應時,就出現了信號完整性問題。

信號完整性包含:

1、波形完整性(Waveform integrity)

2、時序完整性(Timing integrity)

3、電源完整性(Power integrity)

信號完整性分析的目的就是用最小的成本,最快的時間使產品達到波形完 整性、時序完整性、電源完整性的要求。

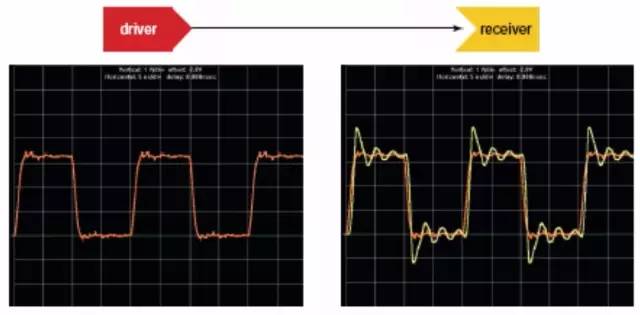

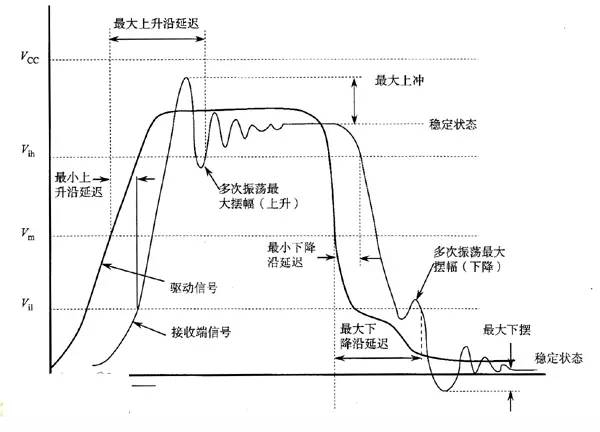

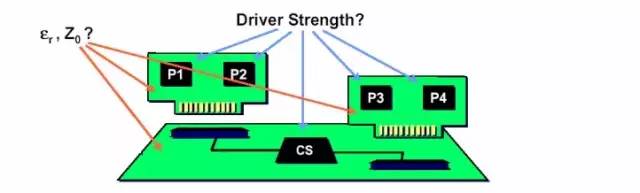

我們知道:電源不穩定、電源的干擾、信號間的串擾、信號傳輸過程中的反射,這些都會讓信號產生畸變,看下面這張圖,你就會知道理想的信號,經過:反射、串擾、抖動,最后變成什么鬼。

如果你的示波器測試上這樣的信號,你一定會問,為什么會這樣,怎么去解決。

首先我們說一下反射:

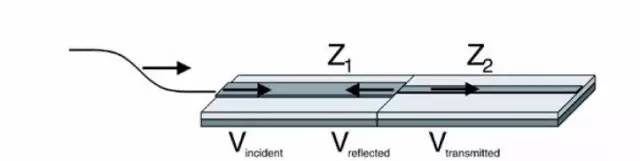

反射--初始波

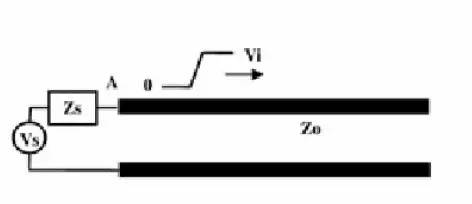

當驅動器發射一個信號進入傳輸線時,信號的幅值取決于電壓、緩沖器的內阻和傳輸線的阻抗。驅動器端看到的初始電壓決定于內阻和線阻抗的分壓。

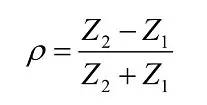

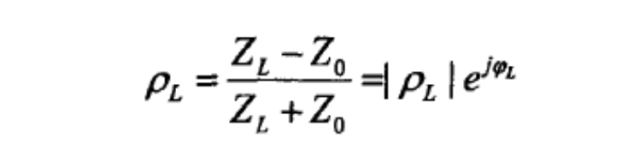

反射系數

其中-1≤ρ≤1

當ρ=0時無反射發生

當ρ=1(Z2=∞,開路)時發生全正反射

當ρ=-1(Z2=0,短路)時發生全負反射

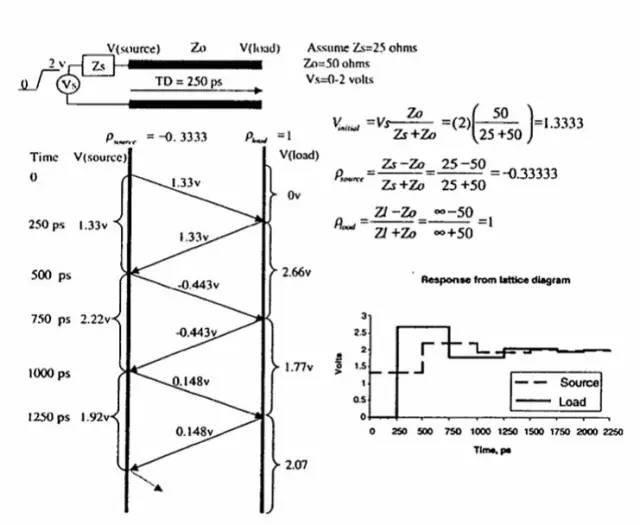

初始電壓,是源電壓Vs(2V)經過Zs(25歐姆)和傳輸線阻抗(50歐姆)分壓。

Vinitial=1.33V

后續的反射率按照反射系數公式進行計算

源端的反射率,是根據源端阻抗(25歐姆)和傳輸線阻抗(50歐姆)根據反射系數公式計算為-0.33;

終端的反射率,是根據終端阻抗(無窮大)和傳輸線阻抗(50歐姆)根據反射系數公式計算為1;

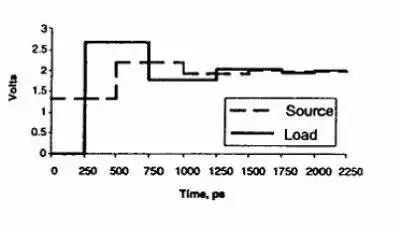

我們按照每次反射的幅度和延時,在最初的脈沖波形上進行疊加就得到了這個波形,這也就是為什么,阻抗不匹配造成信號完整性不好的原因。

由于連接的存在、器件管腳、走線寬度變化、走線拐彎、過孔會使得阻抗不得不變化。所以反射也就不可避免。

電壓后者電流有變化,自然就會往外輻射電磁波。

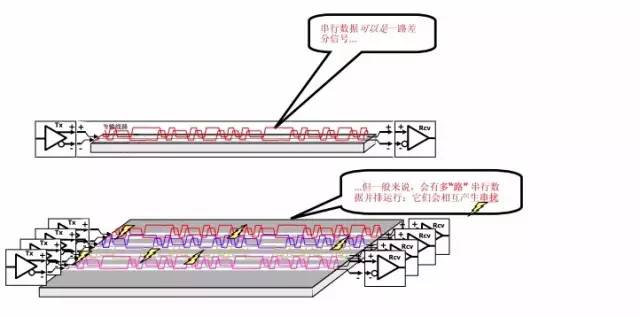

串擾是指當信號在傳輸線上傳播時,因電磁耦合對相鄰的傳輸線產生的不期望的電壓噪聲。

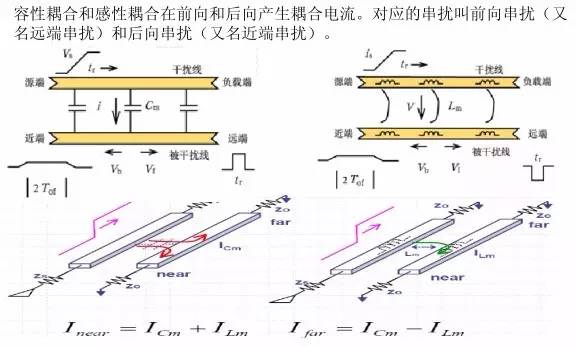

串擾是由電磁耦合引起的,耦合分為容性耦合和感性耦合兩種。

容性耦合是由于干擾源(Aggressor)上的電壓變化在被干擾對象(Victim)上引起感應電流從而導致的電磁干擾;而感性耦合則是由于干擾源上的電流變化產生的磁場在被干擾對象上引起感應電壓從而導致的電磁干擾。因此,信號通過一導體時會在相鄰的導體上引起兩類不同的噪聲信號:容性耦合信號和感性耦合信號。

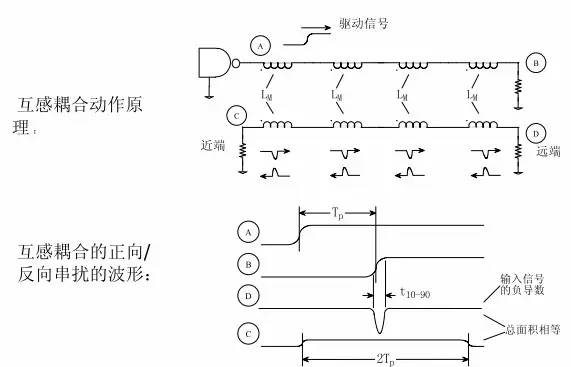

感性耦合:

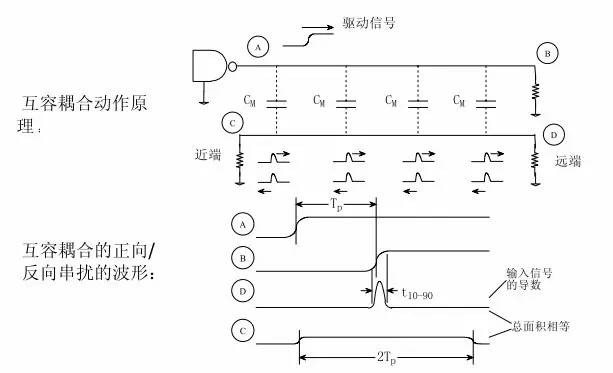

容性耦合:

審核編輯:湯梓紅

-

示波器

+關注

關注

113文章

6190瀏覽量

184521 -

阻抗

+關注

關注

17文章

940瀏覽量

45819 -

信號

+關注

關注

11文章

2780瀏覽量

76629 -

信號完整性

+關注

關注

68文章

1397瀏覽量

95383 -

串擾

+關注

關注

4文章

189瀏覽量

26932

原文標題:串擾和反射影響信號的完整性[20230301]

文章出處:【微信號:EMC_EMI,微信公眾號:電磁兼容EMC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

常見信號完整性的問題之PCB設計串擾的原因與Altium Designer中的串擾消除技術

串擾和反射影響信號的完整性

串擾和反射影響信號的完整性

評論