通信電源PSU在通訊設備中擔任著很重要的角色,PSU問題將會導致整個通訊設備無法正常運作。常見的通信電源PSU拓撲有橋式、推挽以及正在興起的非隔離IBB架構。所有這些應用場景都離不開驅動芯片。在驅動芯片的應用過程中,常見的兩類問題是異常丟波現象以及輸出通道的誤脈沖,他們會隨著芯片、系統設計上的差異而時常出現在我們的應用中,嚴重情況會導致MOS管甚至整個產品的損壞。本文主要從應用角度分析了問題的產生原因以及相應的設計解決方案,確保在設計過程中不會引入可能的風險。

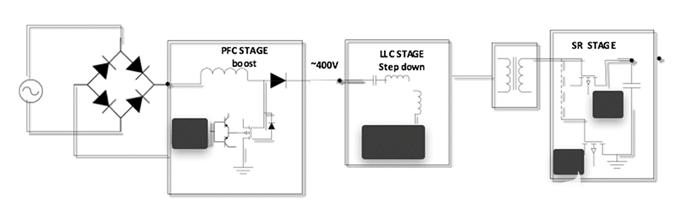

1. 驅動芯片在 PSU電源系統中的應用簡介

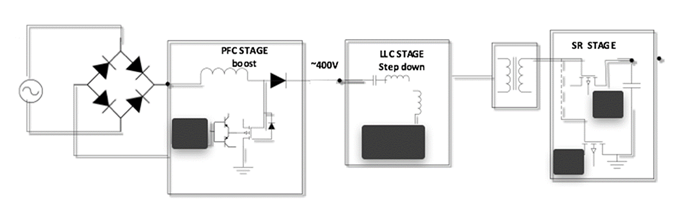

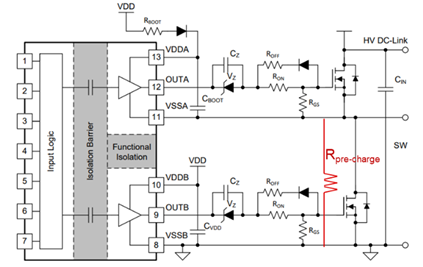

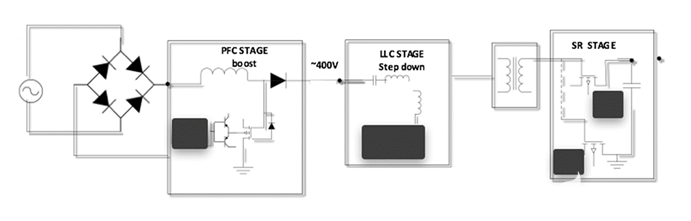

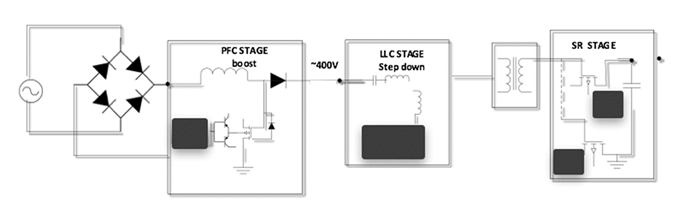

在通訊設備中,系統的供電來源是由前級的PSU供電單元提供的。常見的通信PSU輸出分為12V和48V,12V用于給板上數字部分供電,48V多用于給功放模塊供電。通信PSU常用拓撲架構有推挽、半橋、全橋,不同的拓撲架構通常根據不同的應用場景以及供電需求決定。在通信電源的PA供電部分,IBB(inverting buck-boost)拓撲憑借其不需要隔離,小體積,低成本的優勢越來越多的成為在48V PA供電場景的選擇。TI的雙通道隔離驅動器如 系列,其兩個通道的偏壓供電可以根據需求靈活配置,芯片內部抗干擾能力強,可以廣泛應用于驅動各類拓撲架構中的MOS管。

Figure 1. 通信電源PSU的常見應用

2. 驅動芯片異常丟波問題

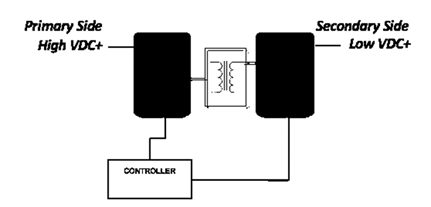

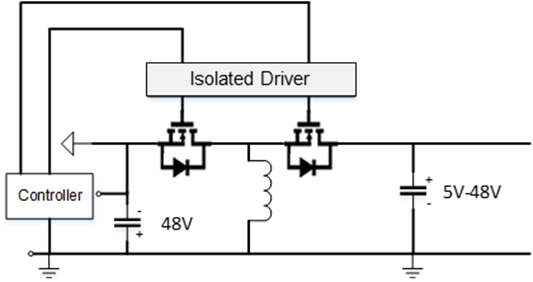

通常隔離驅動芯片用于驅動橋式拓撲中的上下橋臂,或在管。

Figure 2. IBB典型應用拓撲

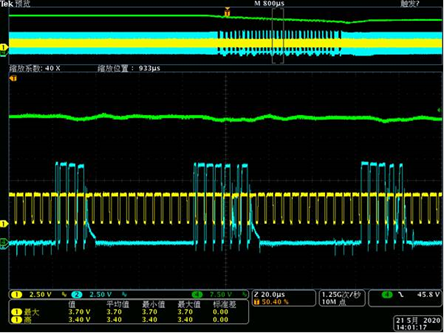

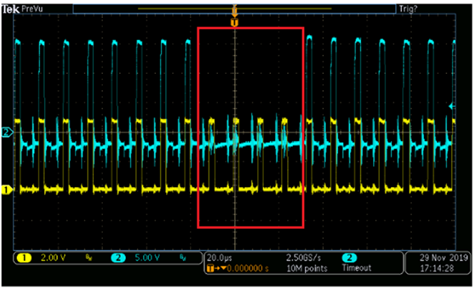

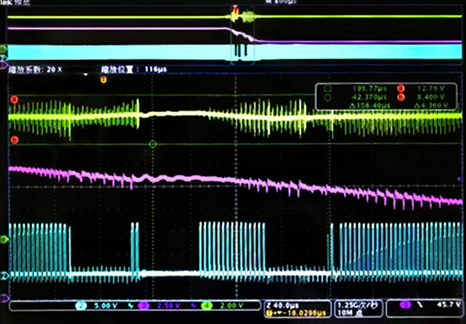

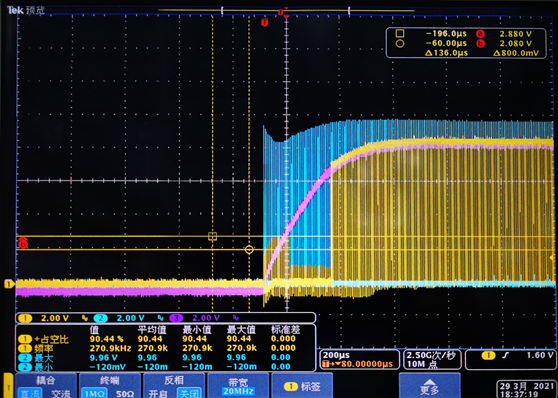

下面兩張圖分別是實際應用中遇到的以及在EVM板上復現的發波異常現象。其中CH1為輸入側的驅動波形,CH2為相應通道的驅動輸出波形(VGS)。可以看到在兩個案例中驅動的輸出都出現了異常的輸入信號存在但輸出信號異常丟失的現象。該異常發波會導致PSU不正常工作,如果不及時斷開負載,還會造成MOS管的損壞。

Figure 3. 實際應用中遇到的丟波現象

Figure 4. 在EVM板上通過特定條件復現的丟波現象

其中實際異常觸發條件:48V/1000W系統,IBB拓撲,開關頻率250kHz,驅動器每個通道驅動5個并聯MOS管,柵極串阻2.2ohm。EVM板復現條件:14V/100A負載,通過反復接入斷開負載可以復現問題。

2.1 針對異常丟波問題的原理分析

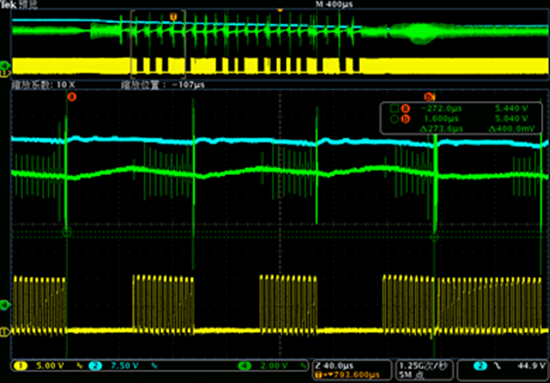

通過對信號進行分析,以上兩種情景的一個共同條件是供電軌VDD都受到了不同程度的干擾,下圖是實際問題的展開波形,可以看到CH4為VDD,在問題發生時接受到了比較大的干擾信號。

Figure 5. 異常丟波問題的展開波形

基于下面典型的驅動框圖分析干擾的來源,如果在驅動的輸出端(OUT)有較大信號波動或是噪聲(該擾動可以是負載變化導致,也可能是開關引入的噪聲),通過芯片內部上管的體二極管傳播至VDD引腳。由于擾動是通過內部電路及寄生參數產生和傳遞,無法通過外部濾波電路濾除,所以即使調整外部濾波電容值,也沒法很好的改善該異常現象。VDD引腳上的干擾信(找元器件現貨上唯樣商城)號,進一步又會通過內部供電LDO的體二極管擾亂內部供電模塊輸出電壓,或是干擾內部供電模塊的邏輯電路,最終使內部電壓跌落至芯片的UVLO,將特定通道的輸出關斷。在內部電壓迅速恢復至UVLO以上后,芯片會延時大約50us后,恢復OUT引腳的正常輸出。同理如果在VSS引腳上有大的干擾時,也會對內部電路造成類似影響。

Figure 6. 典型驅動芯片輸出部分電路結構

2.2 如何從系統設計上優化異常丟波問題

要防止丟波問題的出現,需要保證VDD信號的穩定,減小電源噪聲并減小耦合噪聲的干擾,可從以下幾個方面進行:1. 增大RG或增加串聯磁珠;3.多管并聯系統中注意系統設計。

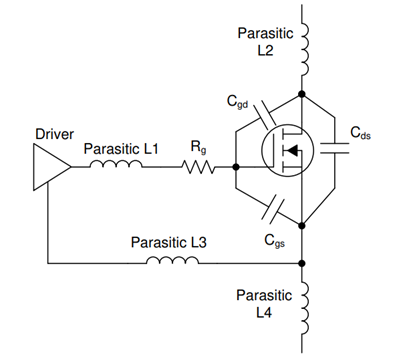

解決干擾問題一個簡單有效的方式就是增大RG,柵極串聯電阻RG會影響柵極電路上的震蕩以及耦合到芯片內部的干擾信號大小。下圖是常見應用中的輸出部分的等效模型,輸入電容(圖中Cgd+Cgs)和源級電感Ls(圖中L4)之間會產生較大的諧振,增加合適的RG則有利于抑制震蕩,同時使開關速度設定在合理的范圍,保證系統高效工作。

Figure 7. 驅動電路簡化等效模型

為了初步評估系統中存在的寄生電感Ls,我們在不接RG條件下測量震蕩波形。由LC諧振公式:

,通過觀察振鈴的震蕩頻率可以得到:

。在選擇RG上令系統處于臨界阻尼到欠阻尼狀態即可:

(另外需要再減去驅動和MOS管部分的電阻值)。實際測試過程中,可以從Q=1/2開始測試所選電阻值以及觀察MOS管的開關速度以及震蕩情況是否能夠滿足系(找元器件現貨上唯樣商城)統的設計需求,如果開關速度不夠可以適當減小RG或是選擇驅動電流能力更強的驅動器,如果震蕩情況影響系統性能,則適當增加RG。下面是在問題系統中,適當增加RG后的測試結果,可以看到RG增大后,問題得到顯著改善。

Figure 8. 實際應用電路中柵極電阻設置為2ohm的問題波形

Figure 9. 實際應用電路中柵極電阻增大為75ohm問題消失

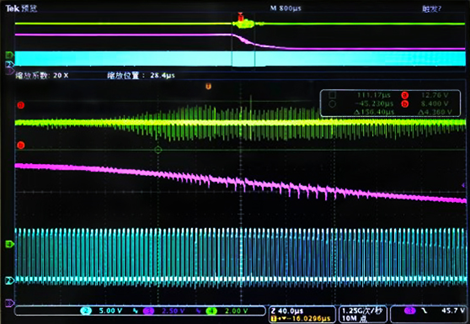

對于實際應用系統,增大RG會帶來系統的損耗以及開關速度的變慢,往往對于特定設計系統,RG期望的阻值會小于10ohm,因此該方案有很多限制。除了增大RG,另一個行之有效的方案是在柵極串入磁珠,相較于電阻的方案磁珠在低頻條件下阻值更低,在不影響驅動電流,不改變開關表現前提下又能夠很好的抑制高頻下的耦合噪聲。

Figure 10. (a) 磁珠阻抗與頻率的關系 (b) RG與磁珠在電路中的作用原理

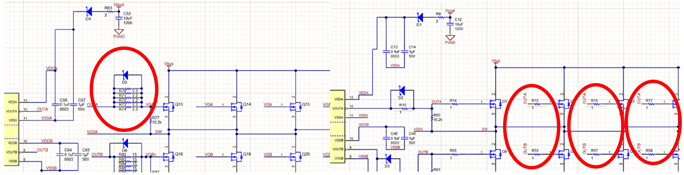

在多管并聯的布板設計中,應該盡可能保證每一個MOS管的柵極電阻都靠近各自的MOS管,而不是將各電阻集中并聯,參考下圖所示。左圖所示布板方案可能會導致并聯MOS管線路之間發生均流震蕩,進而導致系統不穩定。

Figure 11. (a) 發生丟波問題的電路設計 (b) 優化后正常發波的電路設計

3. 驅動芯片輸出引腳誤脈沖現象

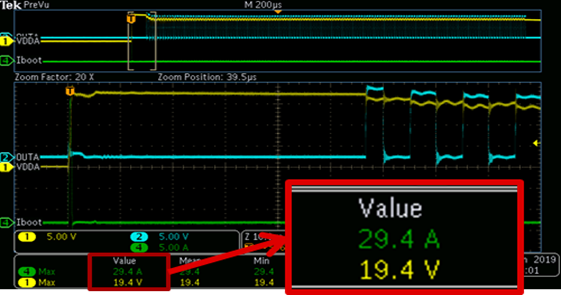

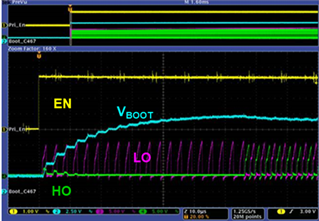

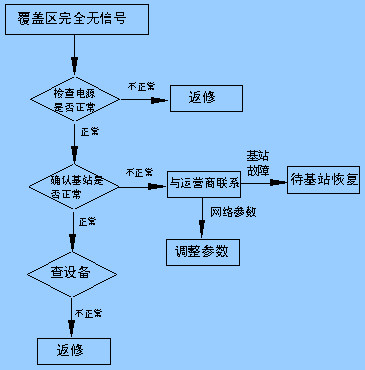

驅動芯片在應用過程中另一個常見的問題是,在沒有輸入信號的情況下,對應的輸出通道出現異常脈沖的現象。該誤脈沖可能會超過MOS管的開通閾值,造成不期望的MOS管誤開通以及很嚴重的系統直通情況。下圖是實際應用中遇到的誤脈沖現象,CH2是驅動芯片LO,CH1是HO,起機過程中,輸入信號控制LO進行開關動作,而在HO對應輸入為低電平。理論上HO應該與輸入信號一致為低,但從實驗結果可以發現,在HO引腳看到了一定幅值的脈沖信號。

Figure 12. 起機過程中出現的誤脈沖現象

起機過程中的誤脈沖信號,會給PSU系統帶來可靠性風險,嚴重情況下可能出現直通現象,損壞供電系統。

3.1 誤脈沖現象成因分析

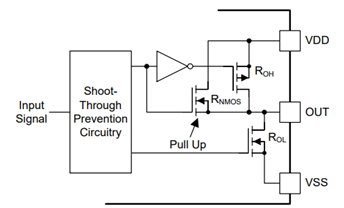

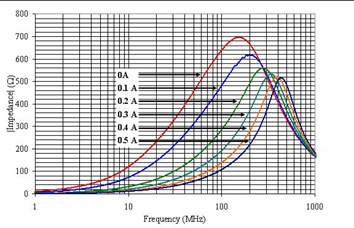

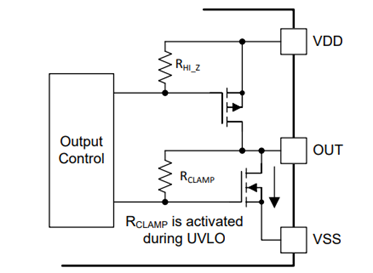

下面為驅動芯片典型的內部框圖,在VDD-VSS之間的電壓建立至內部UVLO閾值之前,芯片內部的Rclamp會起作用,將OUT下拉到地。在VDD-VSS之間電壓上升至UVLO閾值以上后,芯片的輸出完全由輸出通道內部的上下管開關來決定:輸入信號為高時輸出上拉至VDD,輸入信號為低時輸出下拉到地,以此保證輸出邏輯正確。通常誤脈沖現象出現在VDD-VSS之間電壓建立至UVLO之前。

Figure 13. 驅動芯片內部下拉電路典型框圖

在VDD-VSS低于UVLO期間,芯片內部會產生相應的驅動信號,來開通Rclamp電路(為MOS管結構,Rclamp實際為MOS管導通電阻)。該驅動信號的產生會在VDD-VSS建立電壓后,經過一定延時(大約幾十微秒,隨芯片不同而不同)產生,同時信號的產生到下拉電路的完全開通是需要一定的時間的,這兩個因素導致了,當VDD-VSS之間電壓上升過快時,內部驅動信號來不及將下拉電路打開,從而在起機期間芯片無法很好的實現下拉功能。這種情況下當輸出引腳有耦合噪聲的存在時,我們會在柵極路徑上看到誤脈沖。

3.2 誤脈沖的預防與解決方案

因為誤脈沖問題是由于內部下拉電路反應時間的差異化所導致,優化思路可以是將VDD-VSS建立過程放緩,或是在系統設計時注意給VDD-VSS提供一個預充電壓,一個可靠的方案則是在電路中增加下拉電路,確保MOS管不會因為干擾誤觸發。

3.2.1 調整BOOT電壓建立速度

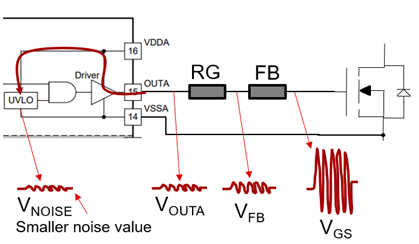

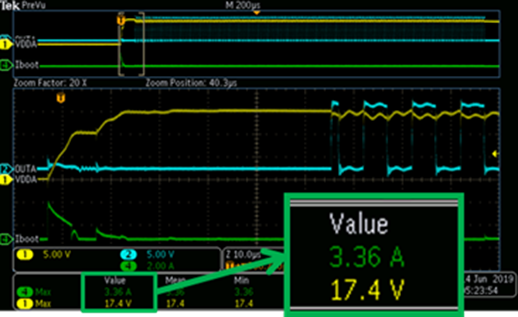

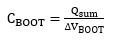

VDD-VSS的電壓建立過程是通過RBOOT,二極管,以及下管的導通狀態給CBOOT電容充電來實現的。針對RBOOT和CBOOT進行數值調整,可以將電容充電到穩定的時間進行延長或縮短。下圖分別展示了不同的RC配置下的VDD-VSS電壓建立過程。

Figure 14. RBOOT=0hom CBOOT=10uF 設置下的起機BOOT波形

Figure 15. RBOOT=5hom CBOOT=10uF 設置下的起機BOOT波形

CH1為VDD-VSS電壓建立波形,CH4為充電電流波形。可以看到,適當的RC取值,不僅能夠減小VDD-VSS間的電流尖峰,還有助于將電壓建立的斜率變緩,使內部下拉信號有充足的時間來響應。

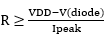

由于市面上驅動芯片設計和針對應用場景不同,有的二極管集成在芯片內部,所以需要使用者在具體應用過程中,根據需要和所用芯片來調整RC取值,下面是一些RC選擇上的建議:

● 電阻取值一般選擇在1~20ohm,且需要滿足

,其中Ipeak為所選擇二極管的最大電流,V(diode)為二極管上的壓降。

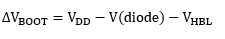

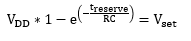

● 有時二極管部分集成在驅動芯片內部,此時可以根據具體情況調節CBOOT,CBOOT需要能夠保證VDD-VSS上的電壓能夠在UVLO之上:

-因此要求BOOT電容上能承受最大電壓為:

-開關周期內需要提供的電荷量:

-可以計算出BOOT電容的最小值為:

其中:

VDD為驅動供電電壓;

V(diode)為二極管正向導通壓降;

VHBL為VDD-VSS下降沿UVLO,即考慮回差后的UVLO值;

QG是驅動MOS管的Q值之合;

IHBS是VDD-VSS間漏電流;

IHB是VDD靜態電流

需要注意的是二極管的反向恢復應力,如上述實驗中的RC組合中開關頻率約為100kHz,占空比為40%,下管的導通時間大約為6us,則需注意的是在6us下管關閉時,二極管上的反向恢復應力能夠滿足芯片或是選擇二極管的指標要求,具體可以參考各芯片數據手冊或者向供應商咨詢。

3.2.2 為VDD-VSS建立預充電壓

另一個解決誤脈沖問題的方案是給VDD-VSS提供一個預充電壓,這樣能讓內部下拉電路的觸發信號能夠提前響應。一個簡便的方式是在上下管VSS之間直接入預充電阻,這樣在上電后,VDD會通過RBOOT,二極管,預充電阻來給CBOOT進行充電,在下管發波之前,就能讓內部下拉電路提前響應,確保VDSS-VSS超過UVLO之前,上管不會出現誤脈沖問題。

Figure 16. 為設計增加預充電壓回路

在加入預充電阻后,系統起機過程中的測試波形如下所示,通道之間不再有干擾導致的誤脈沖。需要考慮的是系統上電到發波之間的預留時間treserve決定了Rpre-charge以及CBOOT的取值。具體參考公式:

Figure 17. 加入VBOOT預建立電路后的發波波形

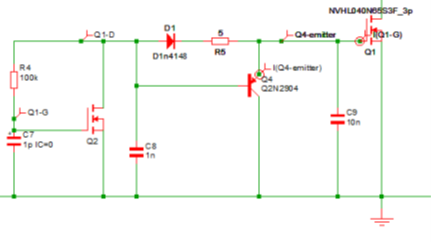

3.2.3 為柵極增加外部下拉電路

如果系統設計允許,一個保險的方式是在電路中加入下拉電路(下圖中BJT管Q4),當柵極電壓受到干擾出現較大波動時,BJT電路會接通,將柵極強行下拉到地防止MOS管的誤開通。

Figure 18. 外部增加柵極下拉電路

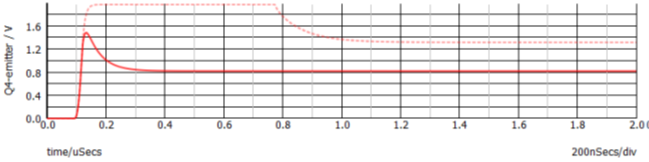

下圖為加入外部下路電路后的柵極電壓仿真波形。虛線代表之前系統可能存在的柵極干擾,實線代表加入下拉電路后柵極電壓波形,可以發現下拉電路將柵極干擾電壓幅值以及電壓回落所需時間都大大縮小,防止了可能出現的MOS管誤觸發風險。

Figure 19. 下拉電路對柵極電壓擾動改善的仿真結果

4. 總結

文章總結了在使用驅動器過程中常見的兩種應用問題:異常丟波問題與輸出通道誤脈沖問題,針對丟波問題,文章給出了柵極電阻設計與布板建議;針對輸出通道誤脈沖問題,本文提出了調整BOOT電壓建立時間、建立預充電壓、添加外部下拉電路等方案,并給出了優化后的測試結果。當然在驅動器的應用中,還有其他常見問題如誤發波或是輸出信號受到干擾等一些特殊情況,由于更多的和芯片的設計或是抗擾能力相關,這里就沒有歸納總結。在選擇驅動芯片時,使用者應該更多關注除了基本的指標參數之外應用層面的設計注意事項。TI的驅動芯片在上述問題中的表現處于業界先進地位,優秀的芯片設計以及可靠性,能夠大大降低在應用中的風險以及設計難度。

審核編輯:湯梓紅

-

MOS管

+關注

關注

108文章

2314瀏覽量

65689 -

電源系統

+關注

關注

3文章

596瀏覽量

37661 -

驅動芯片

+關注

關注

13文章

1223瀏覽量

54143 -

PSU

+關注

關注

0文章

41瀏覽量

11812

發布評論請先 登錄

相關推薦

LED驅動器常見問題解答

數碼舵機常見問題原理分析及解決

驅動芯片在應用中的常見問題分析與解決

驅動芯片在應用中的常見問題分析與解決

驅動芯片在應用中的常見問題分析與解決

驅動芯片在應用中的常見問題分析與解決

評論