眾所周知,語句塊中需要用到的變量只能在語句塊最開始定義。

task some_task();

// do some stuff

// ...

// want to do some stuff here, but need a new var

endtask

你正在編寫task,需要執行一些過程語句,然后在某個時候你發現需要添加新變量。 你第一反應可能是在最頂部定義新變量,即使你真正使用的地方離變量聲明的地方很遠,這樣的代碼可讀性并不是很好,你可能需要往前翻很多行才能找到變量的聲明以及確認初始值。

task some_task();

int some_var; // defined here, but used way farther down

// doing some stuff

// ...

// do some stuff here with 'some_var'

endtask

所以,建議當你只需要一個臨時的/一次性的變量時,你可以就在使用的地方(begin--end語句塊中)聲明就好了

task some_task();

// do some stuff

// ...

begin

int some_var;

//do some stuff here with 'some_var'

end

// carry on with other statements

// ...

endtask

????

審核編輯:湯梓紅

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

Verilog

+關注

關注

28文章

1343瀏覽量

109986 -

System

+關注

關注

0文章

165瀏覽量

36885 -

變量

+關注

關注

0文章

613瀏覽量

28329 -

Coding

+關注

關注

0文章

6瀏覽量

6433

原文標題:SystemVerilog coding過程中你在哪里聲明臨時變量

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

SystemVerilog中的類構造函數new

在systemverilog中,如果一個類沒有顯式地聲明構造函數(new()),那么編譯仿真工具會自動提供一個隱式的new()函數。這個new函數會默認地將所有屬性變量。

發表于 11-16 09:58

?3583次閱讀

程序運行過程中,有些數據被莫名修改了怎么辦?

導讀:程序運行過程中,有些數據被莫名修改了,在哪里修改的?又是怎么修改的?這個代碼我只想知道是否運行過,或者運行了多少次,但是不想讓程序停下來,或者僅打印調試信息,怎么辦?當這個變量設置成某個數據后,我想讓程序自動暫停下來進行分

變量的聲明和定義有什么區別和聯系

變量的聲明和定義是編程中的兩個重要概念,它們在語法和語義上有一些區別和聯系。在本文中,我將詳細介紹變量的聲明和定義之間的區別和聯系。 首先,

keil怎么處理中斷中的臨時變量?

,c 之間明顯沒有調用關系,那么假設a,c使用了相同的Xdata區域,先后進入中斷1,2 ,那不是會導致明顯的錯誤么?或者說keil怎么處理中斷中的臨時變量?

發表于 06-11 04:35

求助,保存的全局變量在哪里?

我有一個關于全局變量的新手問題。我們定義是否將代碼保存到 RAM 或 FLASH 中,并帶有函數屬性。但是全局變量(在函數外部定義的)存儲在哪里?也可以更改存儲它們的位置嗎?

發表于 06-12 07:31

西門子SCL邏輯塊中聲明的變量或參數類型

每類本地變量或參數,都有用各自關鍵字對標識的自己的聲明子域。每個子域包含允許的詳細的聲明子域,子域可按任何順序定位。 下表顯示能夠在各種邏輯塊中聲明

SystemVerilog中$cast的應用

SystemVerilog casting意味著將一種數據類型轉換為另一種數據類型。在將一個變量賦值給另一個變量時,SystemVerilog要求這兩個

在Linux系統中系統變量存在哪里呢?

上面講了很多系統變量,那么在Linux系統中,這些變量存在哪里呢?為什么用戶一登錄shell就自動有了這些變量呢?我們先來看看下面幾個文件。

各種邏輯塊中聲明的變量或參數類型

臨時變量在本地屬于邏輯塊,不產生靜態內存區域,他們位于CPU的堆棧里。本塊正在運行時,其值才被保留。臨時變量不能從聲明它的塊外存取。一個OB

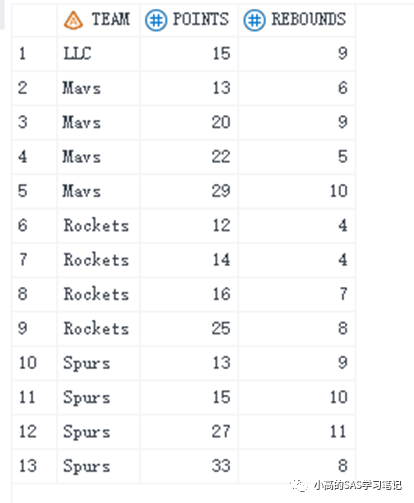

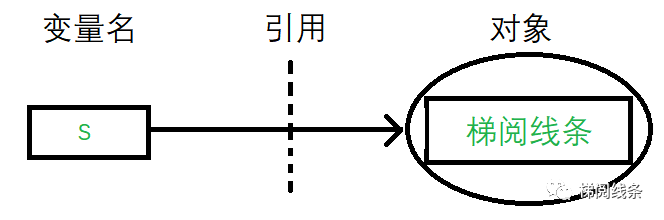

SAS:Data step中first和last變量的應用場景

在SAS的data步中,可以使用by分組,在處理過程中會產生兩個臨時變量first.variable和last.variable,這兩個臨時

Systemverilog中的Driving Strength講解

在systemverilog中,net用于對電路中連線進行建模,driving strength(驅動強度)可以讓net變量值的建模更加精確。

SystemVerilog coding過程中你在哪里聲明臨時變量

SystemVerilog coding過程中你在哪里聲明臨時變量

評論