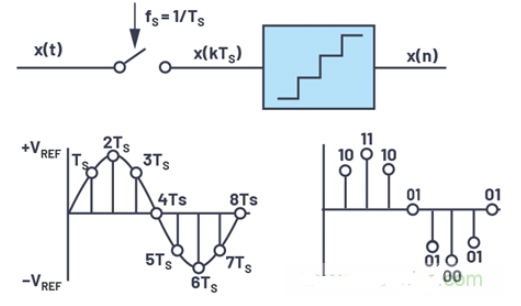

1、ADC采樣原理

根據ADC采樣,外部電路的不同。模擬信號的速度和效率的不同。

一些電路需要更長的時間傳送到ADC的采樣電容。

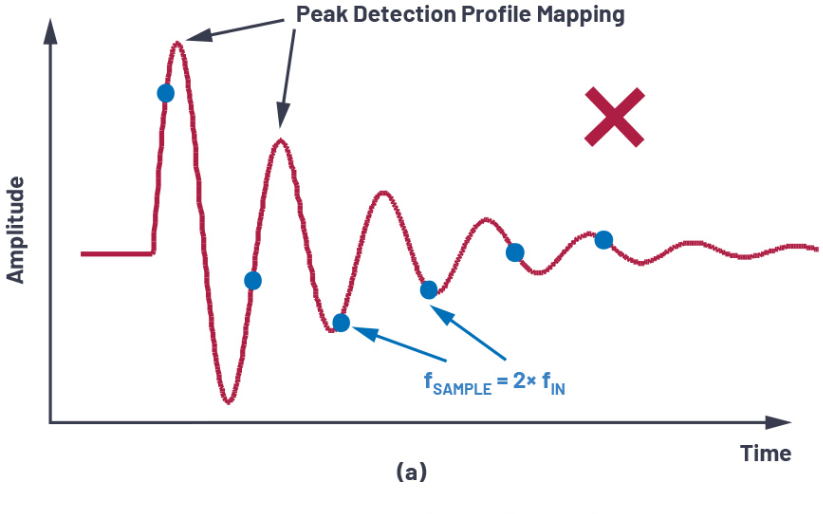

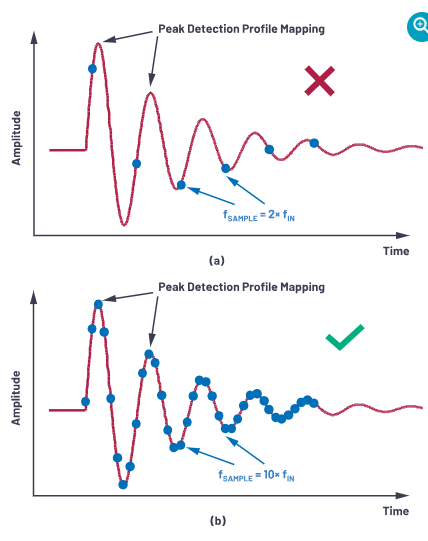

2、ADC采樣保持窗口時間長短對ADC采樣效果的影響

數字控制器采樣時間過長,導致控制環路延時很長,影響閉環控制效果和響應。

采樣時間過短,導致采樣電容的充電時間不夠,采到的電壓低于實際電壓值。

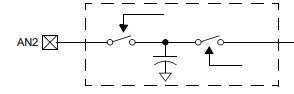

3、數字控制器的ADC模塊的等效電路

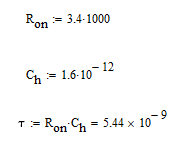

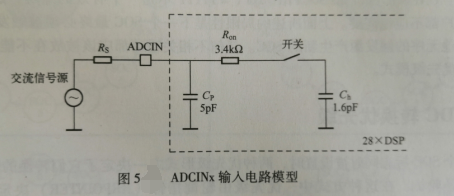

對于DSP28035來說,ADCIN引腳可以用RC電路模擬表示。

采樣電容Ch為1.6pF;

引腳寄生電容Cp為5pF;

開關電阻Ron為3.4k歐;

那么,Ron與Ch組成的電路的時間常數為5.44ns

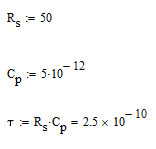

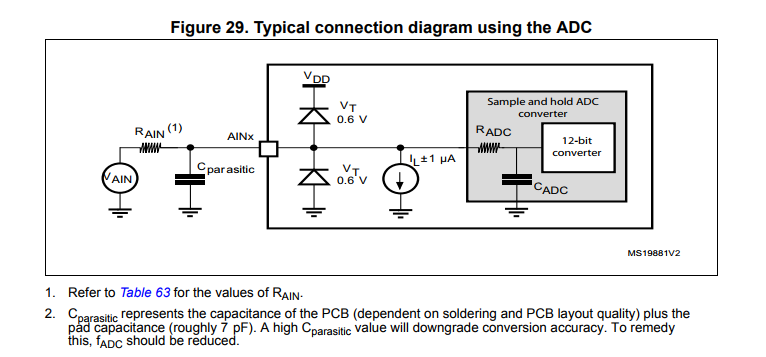

Rs為上級電路信號源的輸出電阻。如果Rs為50歐的話,那么,時間常數為0.25ns。

因此,電壓采樣電路,常常通過使用電壓跟隨器電路來降低輸出電阻。

根據數據手冊,CADC典型值為5pF。CADC比DSP的Ch還大些。該模型與dsp的ADC模型等效電路相似。

對于dsPIC33系列單片機,它的采樣電路等效模型為:

數據手冊有寫,這個電容最大50pF。

因此,外部電阻Rs的大小,直接關系到數字控制器的采樣窗口時間。后文,有詳細的推導。

4、RC時間常數與Uc電壓的關系

時間常數表示過渡反應的時間過程的常數。指該物理量從最大值衰減到最大值的1/e所需要的時間。

當t = RC時, Uc(t) = 0.63Uc_max;

當t = 2RC時,Uc(t) = 0.86Uc_max;

當t = 3RC時,Uc(t) = 0.95Uc_max;

當t = 4RC時,Uc(t) = 0.98Uc_max;

當t = 5RC時,Uc(t) = 0.99Uc_max;

可見,經過3~5個RC后,充電過程基本結束。

5、數字控制器如何設定ADC采樣窗口時間。

如果上級電路的Rs電阻足夠小的時候,那么窗口采樣時間留3~5個Ron與Ch組成的時間常數。

如果上級電路的Rs電阻很大,那么ADCIN引腳的Cp上升時間很長,那么窗口時間還得加上3~5個由Rs與Cp組成的時間常數。(一般來說:正常運行的電路,Cp上的電壓應該不會突變,那么Cp上的初始值就不是零,在這里的窗口時間就不用留3~5個時間常數,僅僅考慮Ron與Ch組成的窗口時間就可以了)

對于dsPIC的ADC輸入等效模型,窗口時間留3~5個Rs與C組成的時間常數就可以啦。

-

單片機

+關注

關注

6032文章

44516瀏覽量

633007 -

adc

+關注

關注

98文章

6438瀏覽量

544092 -

數字電源

+關注

關注

28文章

510瀏覽量

109277 -

采樣

+關注

關注

1文章

120瀏覽量

25539 -

數字控制器

+關注

關注

0文章

84瀏覽量

19497

發布評論請先 登錄

相關推薦

CTSD精密ADC—利用異步采樣速率轉換(ASRC)簡化數字數據接口

ADC需要采樣保持器的原因及采樣ADC的工作原理

ADC采樣過程中遇到的問題分析

如何使用連續時間Σ-ΔADC,簡化信號鏈來解決采樣問題

ADC的采樣時間是怎么計算的?

2812片內ADC采樣時間計算

STM32_ADC采樣時間_采樣周期_采樣頻率計算方法分析

STM32 ADC 采樣值不準確或偏小

STM32 ADC采樣時間、采樣周期、采樣頻率計算方法

中頻采樣和IQ采樣的比較分析

CTSD精密ADC:利用異步采樣速率轉換(ASRC)簡化數字數據接口

數字電源ADC采樣時間的原理分析

數字電源ADC采樣時間的原理分析

評論