今天我們來看看電源完整性分析中重要的一環,去耦電容的使用。

電容實際“長什么樣”

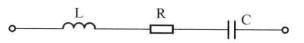

首先我們要了解一個電容的實際特性,一個真實電容可以看成下圖所示的簡化模型:

電容的簡化模型

ESL為串聯電感、ESR為串聯電阻,C為理想電容。根據計算當信號頻率為電容諧振頻率即:

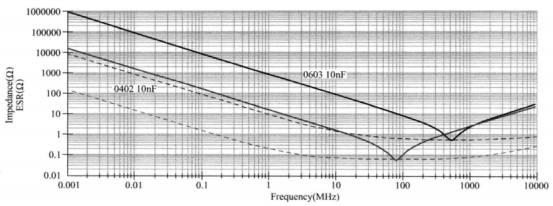

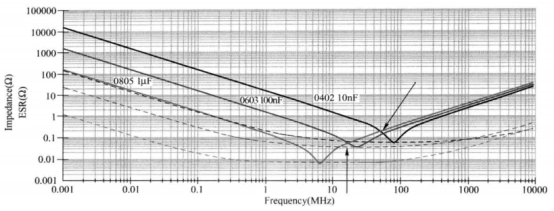

此時容抗和感抗相互抵消,電容的阻抗值最低。如下圖所示:

電容的阻抗特性

圖中阻抗最低點對應的頻率就是電容的諧振頻率22.508MHz。隨著頻率升高,ESR先逐漸降低,再緩慢上升。

可以說從起始頻率到諧振頻點之前,電容的阻抗特性以容抗為主,當頻率點過諧振頻點后,總的阻抗值會隨頻率升高而升高,電容的阻抗以感抗為主。

因此,在電容去耦設計中,當噪聲頻點在諧振點附近時,濾波效果最好,可以為噪聲提供一條低阻抗的回路。

利用去耦電容處理電源噪聲

1.相同容值相同封裝的電容組合:下圖舉例說明了其頻率阻抗特性曲線,可以看到并未展寬低阻抗的頻帶,但是減小了諧振頻點的特性阻抗。

相同容值相同封裝的電容并聯頻率阻抗特性

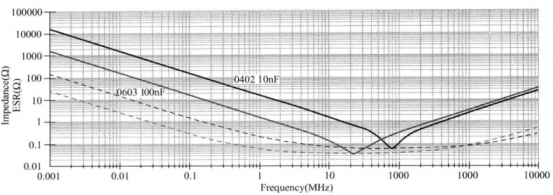

2.相同容值不同封裝的電容組合:下圖舉例說明了其頻率阻抗特性曲線,該方式會展寬低阻抗頻帶。

相同容值不同封裝的電容并聯頻率阻抗特性

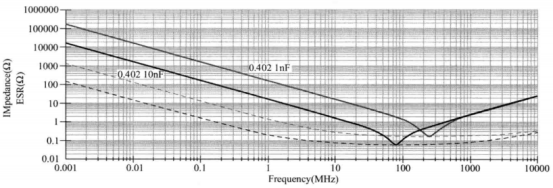

3.不同容值不同封裝的電容組合:下圖舉例說明了其頻率阻抗特性曲線,該方式可以有效地展寬低阻抗頻帶。

不同容值不同封裝的電容并聯頻率阻抗特性

4.相同封裝不同容值的電容組合:下圖舉例說明了其頻率阻抗特性曲線,該方式可以有效地展寬低阻抗頻帶。

相同封裝不同容值的電容并聯頻率阻抗特性

電容并聯作為去耦電容時,需要抑制并聯諧振峰的問題,如下圖舉例所示:

三個電容并聯的頻率阻抗特性曲線

3個不同的電容并聯時,因電容寄生電感的影響,在某個頻點處會發生并聯諧振。如圖中的箭頭所示,3個電容的自諧振點彼此間出現2個阻抗非常高的點叫做并聯諧振峰。因此,為了將電源的目標阻抗控制在一定的范圍內,必須有效地抑制并聯諧振峰。

作者給出了對于不同頻率去耦的大概經驗范圍:

1.10kHz以下用VRM電源轉換即可完成負載電流的實時響應;

2.10kHz~幾百kHz需要用到BUCK電容(電解電容、鉭電容);

3.幾百kHz~100MHz,需要用小封裝的小電容值的電容(如陶瓷電容);

4.大于100MHz就要靠IC的封裝電容了。

審核編輯:劉清

-

串聯電阻

+關注

關注

1文章

190瀏覽量

14767 -

去耦電容

+關注

關注

11文章

315瀏覽量

22311 -

電源完整性

+關注

關注

8文章

209瀏覽量

20708 -

BUCK電感

+關注

關注

0文章

5瀏覽量

1333 -

諧振電容

+關注

關注

0文章

33瀏覽量

2793

發布評論請先 登錄

相關推薦

看看電源完整性分析中去耦電容的使用

看看電源完整性分析中去耦電容的使用

評論