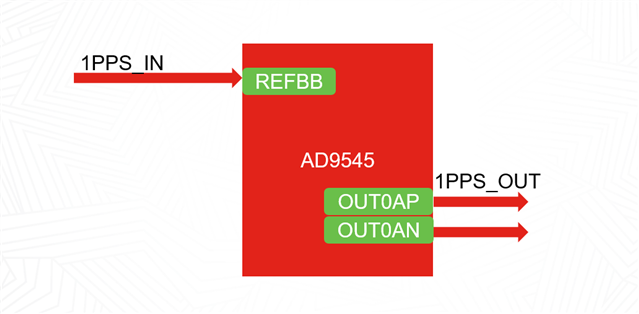

目前使用AD9545方案,備注:1PPS_IN為上升沿500ms的1HZ的時鐘信號,Rise time 160us左右,現在有以下問題請幫忙Spport一下

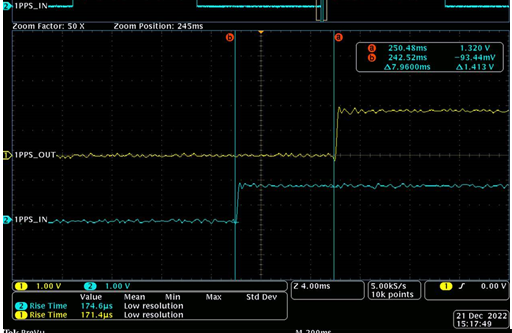

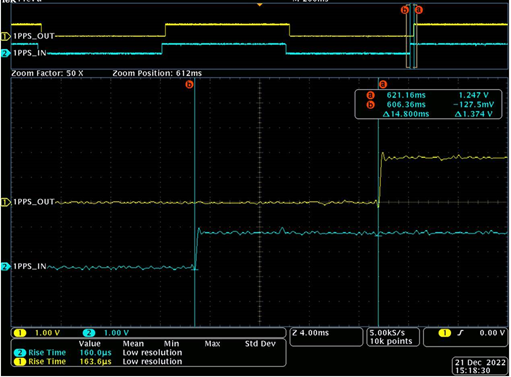

1:目前1PPS_IN與OUT有非固定的延遲,最大15ms左右,我們這邊測試0x3100和ox3200,一直是0x28, APLL鎖定了的,想咨詢一下這個延遲有哪些原因可能導致,

2:當輸入端輸入上升沿10ms的1PPS信號后,輸出還是500ms的上升沿,請問有什么原因可能導致此類問題么?

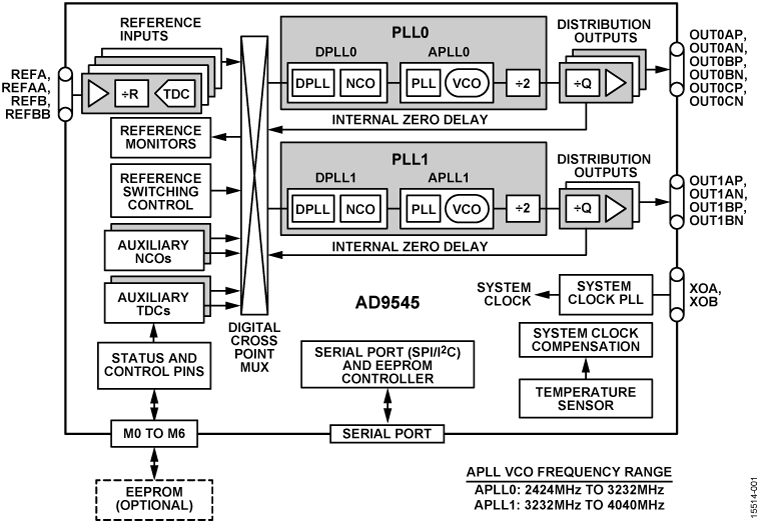

根據您的描述,您是想實現1pps的0延時功能,也就是說輸出的1pps需要和輸入的1pps有個固定的0時延。

AD9545支持DPLL的兩種配置模式,第一種是PBO,這種模式下每次上電初始化鎖定后,輸出和輸入會保持固定相位差,但這個相位差根據每次鎖定時候的初始值會是一個隨機指,也就是說PBO模式下保證輸入輸出頻率鎖定,相位固定但每次不確定。

第二種是0延時模式,該模式下輸入和輸出的1pps可以保證每次鎖定后上升沿嚴格對齊。這兩種模式的配置差異很大,有很多細節包括配置的細節和其他實現的細節需要考慮,請聯系你們的ADI的支持渠道(可以通過sales/fae來找AE支持)來獲取詳細的技術指導,在EZ上很難實現詳盡的解答。

關于您上面描述中的一些問題,我一一答復如下:

1:“1PPS_IN為上升沿500ms的1HZ的時鐘信號,Rise time 160us左右”, 上升沿500ms應該是想表達高電平脈寬500ms的時鐘,rise time160us的可能性不大,可能是測試的示波器采樣率太低帶寬太小造成的偏差。9545對1pps的上升沿時間有具體spec需求定義,詳見datasheet。但對9545的輸入而言,只有上升沿信息是有效信息,高電平脈寬信息不需要。

2:0x3100和ox3200,一直是0x28,所以APLL鎖定了,但DPLL一直沒有鎖定,此時輸入1pps和輸出1pps的相位是一直變化的狀態,而且由于沒有更多寄存器信息,所以并不能判斷此時的DPLL狀態,是否參考有效穩定(0x3005~0x3008)?DPLL是否處于跟蹤鎖定或其他狀態狀態(0x3101/3201)?

3:“當輸入端輸入上升沿10ms的1PPS信號后,輸出還是500ms的上升沿”。這里上升沿10ms應該還是想指高電平脈寬10ms,前面說過,只有上升沿信息有效,也就是說只有上升沿的沿位置是被9545采樣的信息,后面脈寬多長不做任何處理,不會影響內部電路,然后9545的任何輸出頻率都是50% duty cycle的信號,包括1pps,而且這個duty cycle不能調節。

審核編輯:劉清

-

寄存器

+關注

關注

31文章

5317瀏覽量

120001 -

PPS

+關注

關注

0文章

27瀏覽量

10535 -

時鐘信號

+關注

關注

4文章

445瀏覽量

28506 -

高電平

+關注

關注

6文章

146瀏覽量

21330

發布評論請先 登錄

相關推薦

AD9545 IEEE1588 第 2 版以及 1 pps 同步器和自適應時鐘轉換器

AD9545:快速輸入,10輸出,雙DPLL/IEEE1588 1小步同步和Jetter Clearan數據Sheet

AD9545輸入端與輸出端信號延遲問題解析

AD9545輸入端與輸出端信號延遲問題解析

評論