在電路設計尤其是振蕩電路的設計中,往往會遇到不符合設計預期的異常振蕩狀態,通常是因電路中的寄生參數而形成正反饋從而發生振蕩,我們稱為寄生振蕩。

電路中一旦發生寄生振蕩,就會影響電路的正常工作,嚴重會導致電路設計功能完全失效。下面來看看電路中常見的寄生振蕩及消除方法,供大家參考設計。

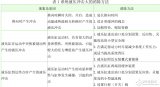

首先來看下回路共用電源的三種形式:

1.不經過穩壓的整流供電;

2.經過線性穩壓后供電;

3.整流或穩壓后經過LC、RC去耦濾波給前級電路供電。

直接由線性穩壓電路作為總供電電源時,“電源”具有很低的低頻內阻,電路出現低頻寄生耦合的機會比較少。若為去除回路間高頻耦合而采用了不合適的RC或LC濾波,那么有可能產生較大的低頻耦合。

在低頻上,電容器的阻抗增加,去耦濾波器的去耦作用減弱。后級電路的工作電流在電源內阻上產生壓降,經過去耦濾波器耦合到電路前級,同時還附加一定的相移。再加上供電電路固有的內部反饋環路,有可能使電路滿足振蕩條件發生1Hz以下的超低頻寄生振蕩。

消除這種現象的方法: 增加RCL的值或者進行參數調整破壞其相位條件 ,最終破壞振蕩條件,使電路進入穩定。

通過公用電源除了低頻寄生振蕩外,還有可能形成MHz量級的高頻寄生振蕩。產生這種振蕩的原因有如下幾種:

1.線性穩壓集成電路的內阻隨工作頻率的增加而增加,因為穩壓器內部誤差調整電路的增益隨工作頻率的升高而降低;

2.電源濾波電容器的封裝電感感抗隨工作頻率升高而升高;

3.電源供電電路的引線電感的存在。

在計算電源濾波器時,往往采用CLC“π”型濾波器加上一個或數個大容量的鉭電容或電解電容。應特別注意,π型濾波器同時是一個很好的諧振回路,它的諧振頻率不應該接近或與電路的工作頻率相等,否則就會失去濾波的作用,增加寄生振蕩的機會。

在PCB設計中,對于僅需相同電壓的回路,因公用電源而連接起來,并無信號的輸入輸出關系,那么應對其電源、地進行隔離、分割,可以消除有害的公共阻抗。對于濾波良好的回路,其電源、地的交流電位應是相同或相異極小的。

器件寄生耦合

器件之間的寄生雜散耦合有電場耦合、磁場互感耦合等。

兩個靠近的器件之間往往同時存在靜電場以及互感耦合。尤其對于包含磁性材料的器件,磁互感會更加嚴重,可以通過加大放置距離,磁場正交排布解決問題。磁屏蔽應選用 磁導率高的材料 。磁屏蔽的效果不但與材料的導磁率高低有關,還與屏蔽層的厚度、結構等有關。

電場耦合可以通過 縮短器件引線和減小器件體積來減小 。在具有弱信號以及高增益的PCB上,電路布局務必追求輸入、輸出端的最大距離處理。若因受體積限制而不能做到最遠排布,應做好各部分的屏蔽處理。電場屏蔽材料應選用高導電率的材料如銅箔或者鋁材等,靜電屏蔽應該接至電路的交流地。

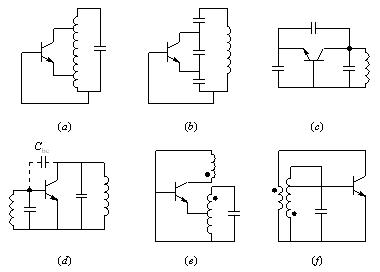

器件引線、極間電容、接地電容構成的寄生振蕩器

這些情況往往會因器件分布參數的存在而構成頻率達幾百兆的振蕩器,用低速的示波器無法觀察到振蕩的存在(因探頭影響了振蕩回路而停振),用一些間接的方法可以觀察: 如器件的接法正確、無損壞,但工作異常,電流失控、溫度出奇地偏高,用萬用表筆接觸器件引腳會改變器件的工作電流等 。這些現象都表明了器件存在寄生振蕩。

消除寄生振蕩的方法是減小分布參數:采用體積更小的器件、縮短引線、改變器件在PCB上的排布等。這樣可以使寄生振蕩回路的頻率升高,當頻率高至器件的截止頻率外時,寄生振蕩會因為無法滿足正反饋條件而消失。

當因PCB布局限制無法縮短器件之間的引線時,可以在引線中串聯消振電阻,降低引線的Q值,其最終效果是降低了振蕩電路的增益,可以有效地消除寄生振蕩。從消除寄生振蕩有效性的角度看,消振電阻的阻值越大越有利于消除寄生振蕩,但阻值過大就會對正常信號形成衰減,需根據實際情況選取折中的值。

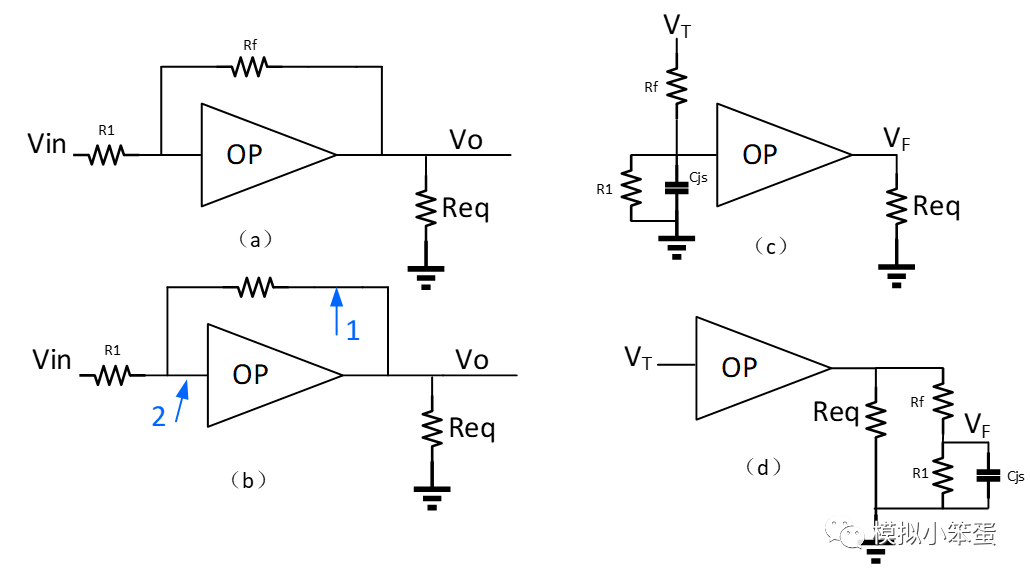

負反饋轉變為正反饋

對于針對某功能需求設計的負反饋環路,若閉環增益過高,同時環內放大器級數有三級以上,那么由于器件本身以及其他相移的積累,很容易使得環路對某些頻率變成了正反饋,若同時閉環增益也滿足條件,就會在電路中激發起振蕩,也是寄生振蕩的一種。

這種情況可以通過將頻率補償器件介入頻帶最窄的一級,可以最容易破壞自激的相位條件,對于器件內部相移無法估算的情況,可以在實際調試中更換補償器件值來實現。

審核編輯:劉清

-

電容器

+關注

關注

64文章

6205瀏覽量

99326 -

供電電路

+關注

關注

1文章

65瀏覽量

14971 -

濾波器

+關注

關注

160文章

7732瀏覽量

177704 -

線性穩壓器

+關注

關注

5文章

757瀏覽量

66594 -

振蕩電路

+關注

關注

17文章

501瀏覽量

98719

發布評論請先 登錄

相關推薦

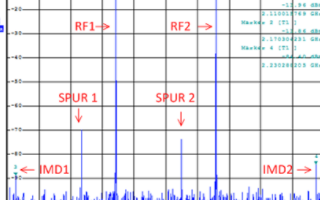

調制器輸出端的寄生信號的產生原因和如何消除

運放OP閉環電路小信號分析中常見的問題

buck電路輸出電壓波形振蕩怎么消除

負反饋放大電路自激振蕩產生原因及消除方法探討

油系統設備常見故障分析及其消除方法

防止MAX2104電路中的寄生振蕩

引起放大器振蕩的原因是什么,如何解決?

防止MAX2104電路中的寄生模式振蕩

電路中常見的寄生振蕩及消除方法

電路中常見的寄生振蕩及消除方法

評論