為CPU和其他高密度邏輯提供電力從來都不是一件容易的事,盡管一段時間以來,技術似乎最終會降低計算任務所需的功率。盡管技術進步很快,但對計算能力不斷增長的需求似乎吸收了所有改進并要求更多。這種對功率的需求在筆記本電腦中尤為明顯,盡管每瓦可用的計算能力大幅增長,但其電池壽命的延長充其量是增量的。

無論這種性能停滯不前是由于需要跟上技術的步伐,還是反之亦然,便攜式系統中對更高電源電流的需求迫使設計人員熟悉新的電源技術。本文將探討其中的一些新技術。

不斷縮小的幾何尺寸一直壓低CPU、DSP和其他大規模邏輯器件的電源電壓。目前在+1.5V至+2.5V范圍內,這些電壓應該很快就會達到1V。高效產生如此低的電壓可能是一個問題,特別是對于 10A 及以上的輸出電流。

與大多數電子設計一樣,有效的電源必須協調許多相互沖突的目標,包括成本和組件數量、效率和熱行為、電路尺寸和瞬態性能(對負載階躍的響應等)。電池壽命僅是便攜式(電池供電)系統的問題,但廢熱(以及效率)是電池和交流供電系統的主要問題。

更嚴格的負載調整率 + 更快的響應 = 一場失敗的戰斗

當今的 CPU 內核需要非常嚴格的負載調節。直到最近,主要的CPU制造商都要求這樣做。但是,電源電流和時鐘頻率會隨著電源電壓的下降而上升,這對電源提出了很高的要求,尤其是在負載階躍行為方面。滿足這些日益嚴格的性能限制的難度和成本不斷增加,促使人們重新思考電源設計。作為更高負載電流和更大負載瞬變的一個結果,在處理器周圍涌現的電容器“農場”增加了設計的尺寸和成本。

這些問題,以及即使是最快的開關模式穩壓器也無法處理由突然負載階躍引起的瞬時輸出降這一事實,迫使人們改變思維(和規格)。輸出電容必須完成所有工作,以應對當今CPU速度的階躍響應。此外,更嚴格的負載調節規格導致更高的開環增益,需要更多的輸出電容來保持穩定性。因此,很明顯,某種放寬負載調節要求的方法將在減少組件數量和其他方面獲得豐厚的回報。

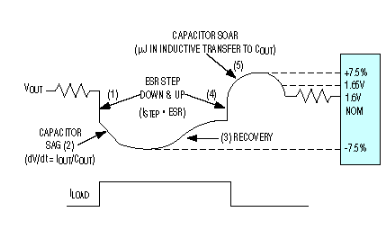

典型DC-DC轉換器對負載階躍的響應(圖1)有五個基本要素:

瞬時壓降,其幅度等于負載電流階躍的增加乘以輸出電容的等效串聯電阻(ESR)。

瞬時壓降后,在DC-DC轉換器響應之前可能會出現下降,其中電容器電壓隨著電容器提供負載電流而下降。

電壓恢復間隔,當電感接通以源出負載電流并補充輸出電容時。

當負載被移除時,“ESR升壓”(逆轉瞬時下降的影響)。

一些過沖,因為存儲在第一個電感脈沖中的能量(在負載下降之后)被傳遞到輸出電容。

元件 2、3 和 5 可以通過精心設計和明智地選擇 DC-DC 控制器來最小化。但是,瞬時電壓階躍(1和4)不能降低,除非降低輸出電容的ESR。快速穩壓器響應可以在初始步驟后更快地拉高輸出,但不能阻止初始壓降本身。即使是最快的DC-DC轉換器(例如MAX1711,響應時間不到100ns)對于600MHz及以上CPU時鐘引起的負載瞬變來說也太慢了。

圖1.該波形說明了瞬態負載階躍的主要分量。

電壓定位

很明顯,鞭打DC-DC轉換器的不切實際的瞬態行為是沒有希望的。600MHz CPU在MAX60的1711ns響應時間內產生100個時鐘周期。如果電源電壓總是下降 ESR庫特× I加載步驟并在那里停留幾個時鐘周期,輸出是否恢復到其標稱值是否重要?從CPU的角度來看,這并不重要。然而,從電源的角度來看,這很重要。

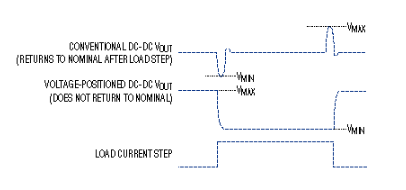

電源更希望負載下的電壓永遠不會恢復到“標稱值”。這樣,當負載被移除時,可以容納近兩倍的瞬態電壓上升。同樣,施加負載時允許兩倍的瞬態跌落。圖2顯示了電壓轉換器響應負載階躍的不同方式。

圖2.由于電壓定位穩壓器不會在每個負載階躍后嘗試將輸出電壓恢復到中心“標稱值”,因此它們允許更大的瞬態偏移。這種額外的裕量也降低了功耗和輸出電容數量。

這些考慮因素催生了一種新的CPU電源規格(參見圖1中的灰色框)。標稱電壓為1.6V,但負載相關壓降可以將其降低7.5%(按照當前的CPU標準相當草率)。當負載從滿負載降至零時,它也可以上升 7.5%(僅限短期脈沖)。穩態下的輸出電壓不得超過1.65V,包括噪聲和紋波。這些數字有助于最大限度地減少電容器數量,同時大幅延長電池壽命并減少熱量。

要充分利用 CPU 電源的更寬限制,您可以為給定電源定義電壓/負載配置文件。該特性允許您實現受控形式的負載抑制(有時稱為電壓定位),其中輸出電壓定位為負載電流的函數。電壓定位允許輸出下降,并且不會浪費能量和金錢試圖支撐它。相反,輸出設置為隨著負載電流的增加以定義的方式下降。與蠻力方法相比,這種方法對瞬態問題提供了更優雅的響應(暴力方法提供的好處有限,但需要DC-DC轉換器具有更大的電容和更快的速度)。

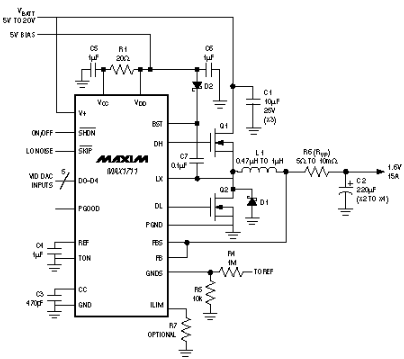

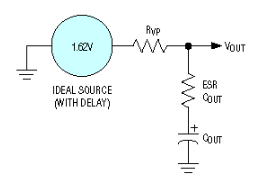

電壓定位功能可以添加到許多不超過三個電阻的 DC-DC 控制器中(圖 3)。R4和R5為設定輸出電壓增加一個小的正失調,將其從標稱1.6V(在本例中)提高到1.62V。R6 (R副總裁) 與輸出串聯,與輸出電容的最差情況 ESR 匹配。R的效果副總裁是插入一個定義的、與負載相關的壓降。

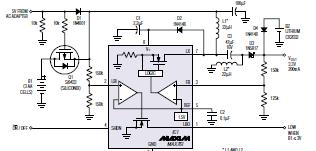

圖3.這種高效的 15A 穩壓電源可通過增加三個電阻器輕松轉換為電壓定位設計:R4、R5 和 R6 (R副總裁).

| IOUT(A) | C1(μF) | L1(μH) | R6(RVP, mohm) | R7 | C2(μF) | Q1 | Q2 |

| 7 | (2) 10 | 1 | 10 | ILIM = VCC | (2) 220 | IRF7807 | IRF7805 |

| 10 | (3) 10 | 0.68 | 8 | ILIM = VCC | (3) 220 | IRF7811 | IRF7809 |

| 12 | (3) 10 | 0.47 | 7 | 220 kΩ | (4) 220 | IRF7811 | IRF7809 |

| 15 | (4) 10 | 0.47 | 5 | 210 kΩ | (4) 220 | IRF7811 | IRF7809* |

C1 = 陶瓷電容器,C2 = 松下 SP 系列:EEFUEOE221R。

*對于連續 15A 負載,由于 IR2 的熱限制,請使用 (7811) IRF2 或 (7805) IRF7809。

如果RVP與濾波電容的ESR匹配,則輸出下降初始負載階躍降(ESR×ILOAD),只要負載保持不變,輸出就會保持在該電平。降低負載會導致電壓電平上升(ΔI×ESR)。在最后一次電感放電和控制器的100ns響應之前(但在允許的7.5%限制內)短暫的瞬態脈沖之后,直流電平再次保持在由空載電壓(在本例中為1.62V)減去ILOAD×RZ定義的水平。參見圖 4。

圖4.圖3電路的階躍響應說明了電壓定位輸出的優勢。

與輸出串聯增加5mΩ會降低效率。但是,它也會降低CPU在重負載下的工作電壓,從而降低功耗并延長電池壽命。與傳統(非定位)穩壓器相比,電壓定位設計可將 CPU 耗散降低 1.38W,總功耗降低 0.4W(圖 5、6)。

圖5.這個簡化的模型說明了電壓定位的基礎知識。對負載階躍(圖2)的理想“方波”電壓響應發生在R副總裁等于 ESR(C 的有效串聯電阻外).

圖6.盡管增加了輸出電阻會降低轉換效率,但電壓定位設計可降低電源和CPU內部的功耗。

有效效率

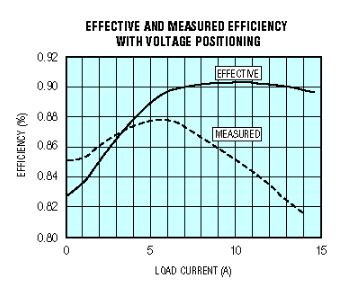

由于這種改進是以犧牲轉換效率為代價的,因此提出一個新術語來比較電壓定位電路與傳統(非定位)電路可能會有所幫助。該術語“有效效率”是非電壓定位設計中與電壓定位設計的性能相等的效率。

要確定電壓定位穩壓器的有效效率,首先以常規方式[(VOUT × IOUT)/(VIN × IIN)]測量其效率,然后將負載建模為每個效率數據點的電阻(RLOAD = VOUT/IOUT)。接下來,使用非定位輸出電壓(INP = VNP/RLOAD,在本例中為 VNP = 1.6V)計算每個 RLOAD 數據點的輸出電流。然后計算每個INP數據點的有效效率,即非定位功率輸出(VNP×INP)除以測量的電壓定位功率輸入(VOUT×IOUT)。請注意,超過100%的有效效率在數學上是可能的,但尚未實現。

圖 7 顯示了典型 CPU 電源的這種改進有多顯著。為了匹配電壓定位帶來的好處,滿載時的傳統設計需要將效率提高近8%。

圖7.這些圖顯示,在滿負載時,電壓定位的CPU電源具有8%的優勢。傳統設計需要 90% 的轉換效率才能與提供 82A 電流的電壓定位設計的 14% 效率相匹配。

-

dsp

+關注

關注

552文章

7962瀏覽量

348308 -

cpu

+關注

關注

68文章

10829瀏覽量

211194 -

電池

+關注

關注

84文章

10476瀏覽量

129064

發布評論請先 登錄

相關推薦

便攜式電池供電醫療設備中鉭電容的使用

便攜式示波器的技術原理和應用場景

便攜式UPS儲能電源的簡介和應用

怎么利用嵌入式CPU卡設計醫用便攜式監護儀?

基于嵌入式CPU卡的醫用便攜式監護儀怎么實現?

便攜式UPS電源的相關資料推薦

便攜式白噪聲發生器的資料分享

嵌入式CPU卡在醫用便攜式監護儀中的應用

便攜式產品的供電設計

便攜式電池系統

為便攜式CPU內核供電

為便攜式CPU內核供電

評論