用于產生 DDR 存儲器終止電壓的電源,即使在極端負載瞬變期間,從最大額定灌電流到最大額定拉電流,也只能承受 40mV 的變化。通常使用昂貴的大型電容器來確保不超過容差帶。但是,通過增加DDR存儲器終端電壓的下降,電源輸出電容可以大大降低。本應用筆記說明了使用MAX1917的技術。

DDR 內存的終止電壓電源需要跟蹤 DDR 內存電源電壓 VDDQ,并且需要源出和吸收負載電流。在極端負載瞬變期間,從最大額定灌電流到最大額定拉電流,其最大電壓偏差不應超過40mV。

MAX1917采用快速PWM控制架構,在一個開關周期內響應階躍負載變化,從而減少對輸出電容的要求。通過在設計中增加有意的電壓下降,可以進一步降低輸出電容,而不會損失瞬態性能。

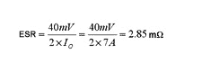

例如,在 1.25V/7A 終端 VTT 電源中,輸出電容的選擇應使 ESR 小于:

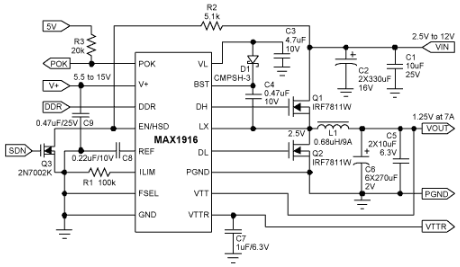

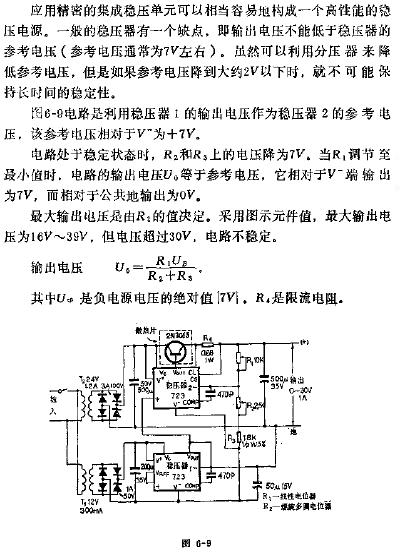

輸出端的 560 個 4μF/270V OSCAN 電容器、2 個 5μF/150.4V SPCAP 或 270 個 2μF/2V POSCAP 可滿足此 ESR 要求。出于空間考慮,選擇了5個35μF/7V SPCAP,總ESR為7.7mΩ。這在 -1A 至 <>A 至 -<>A 的階躍負載變化期間產生 <>mV 的最大電壓偏差,不包括輸出紋波電壓。圖 <> 顯示了 VTT 終端電壓電源的原理圖。

圖1.1.25V/7A VTT 電源原理圖

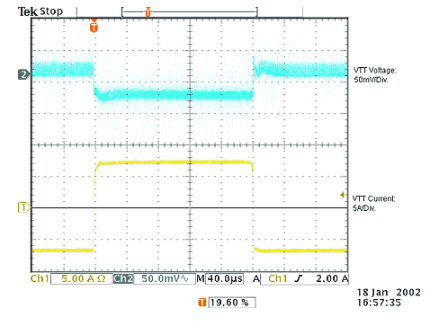

圖2顯示了階躍負載瞬變期間VTT和輸出電流的波形。從該圖中可以明顯看出,最大電壓偏差小于40mV。從圖2中還可以清楚地看出,峰值電壓過沖或下沖在負載瞬態結束后立即結束,表明環路響應非常快。

圖2.階躍負載瞬變期間的VTT和負載電流波形。

當使用下垂方法時,所需的ESR可以加倍,即先前計算的5mΩ。最大抗下垂電阻由下式給出

其中 V負荷是負載調整率,約為1mV/A,包括走線電阻,V。脈動是輸出紋波電壓。考慮到一定的設計裕量,選擇2mΩ電阻R3,如圖3所示。此外,使用四個SPCAP而不是三個設計裕量,但與圖2相比,需要的電容減少了1個。圖4顯示了相同負載瞬態響應下的VTT電壓和負載電流波形。最大電壓偏差完全在80mV電壓范圍內。總之,增加輸出壓降會進一步降低所需的輸出電容,從而降低系統總成本。

圖3.帶輸出下垂的VTT電源原理圖。

圖4.負載瞬態期間的VTT和負載電流波形,輸出下降。

審核編輯:郭婷

-

電源

+關注

關注

184文章

17594瀏覽量

249521 -

存儲器

+關注

關注

38文章

7453瀏覽量

163608 -

DDR

+關注

關注

11文章

711瀏覽量

65230

發布評論請先 登錄

相關推薦

LM2576輸入端電池電壓下降!【已解決】

電源技巧:不要讓USB電壓下降減慢充電器的速度

LTC3718:適用于DDR/QDR存儲器終端的低輸入電壓DC/DC控制器產品手冊

在DDR存儲器終端電壓電源中增加電壓下降可降低輸出電容

在DDR存儲器終端電壓電源中增加電壓下降可降低輸出電容

評論