Versal

Versal 架構(gòu)將“Scalar Engine”(標(biāo)量引擎)、“Adaptable Engine”(自適應(yīng)引擎)和“Intelligent Engine”(智能引擎)這三種不同類型的引擎與豐富的連接和通信功能以及片上網(wǎng)絡(luò) (NoC) 有機(jī)結(jié)合,從而支持實(shí)現(xiàn)覆蓋整個(gè)器件的無縫式存儲器映射訪問。

智能引擎包括:

SIMD VLIW AI 引擎,適用于自適應(yīng)推斷和高級信號處理計(jì)算

DSP 引擎,適用于定點(diǎn)運(yùn)算、浮點(diǎn)運(yùn)算和復(fù)雜的 MAC 運(yùn)算。

自適應(yīng)引擎將可編程邏輯塊與存儲器有機(jī)結(jié)合,它具備專為應(yīng)對高計(jì)算密度需求而設(shè)計(jì)的架構(gòu)。

標(biāo)量引擎包括 Arm Cortex-A72 和 Cortex-R5 處理器,支持計(jì)算密集型任務(wù)。

片上網(wǎng)絡(luò) (NoC)

片上網(wǎng)絡(luò) (NoC) 是一個(gè) AXI 互連網(wǎng)絡(luò),用于在可編程邏輯 (PL)、處理器系統(tǒng) (PS) 和其它硬核塊中的 IP 端點(diǎn)之間共享數(shù)據(jù)。

此基礎(chǔ)架構(gòu)覆蓋整個(gè)器件,基于專有的切換開關(guān)形成高速集成的數(shù)據(jù)路徑。

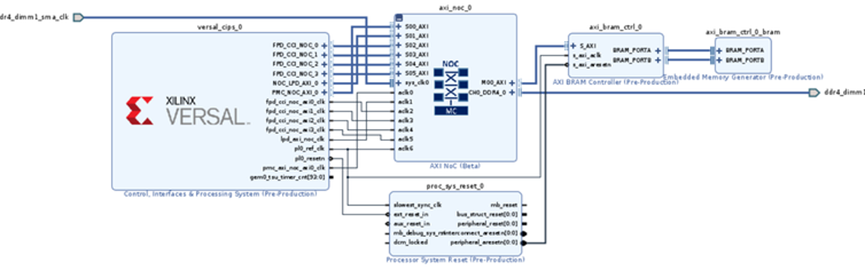

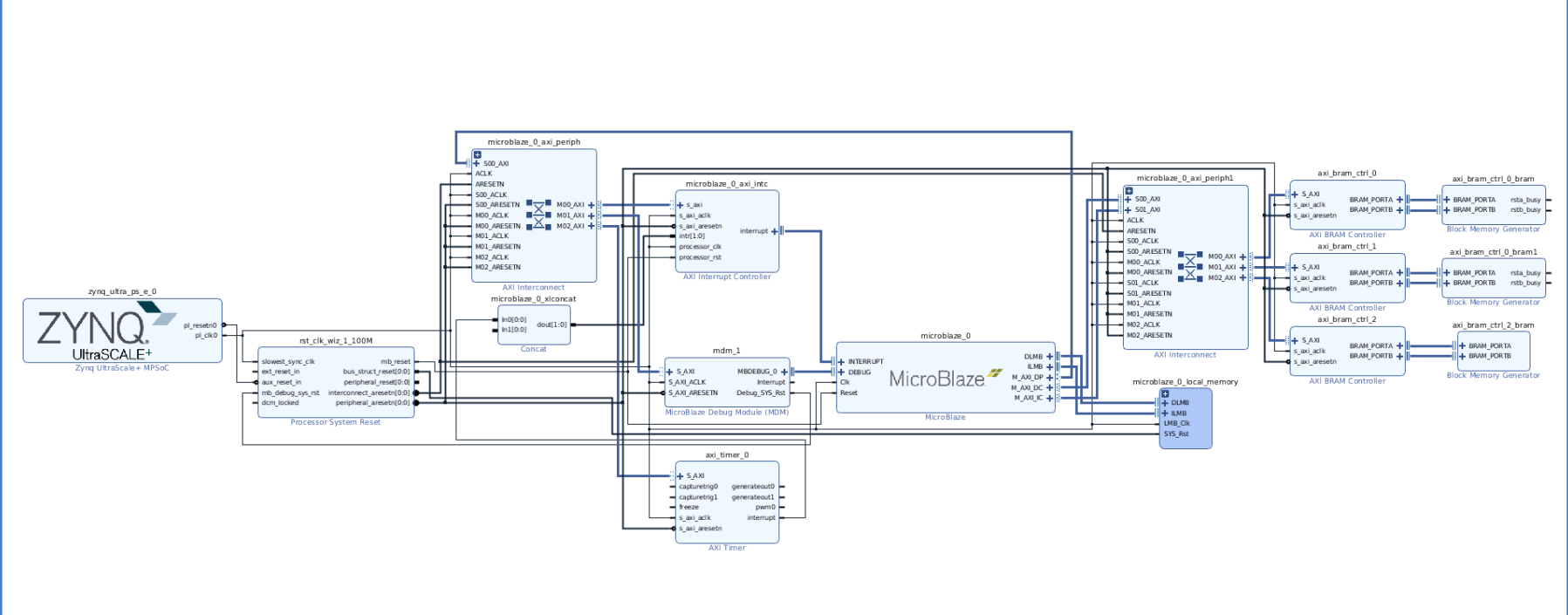

模塊框圖

Vivado 步驟

步驟 1:

以 VCK190 評估板為目標(biāo)創(chuàng)建工程,并在 IP integrator 內(nèi)創(chuàng)建塊設(shè)計(jì)。

步驟 2:

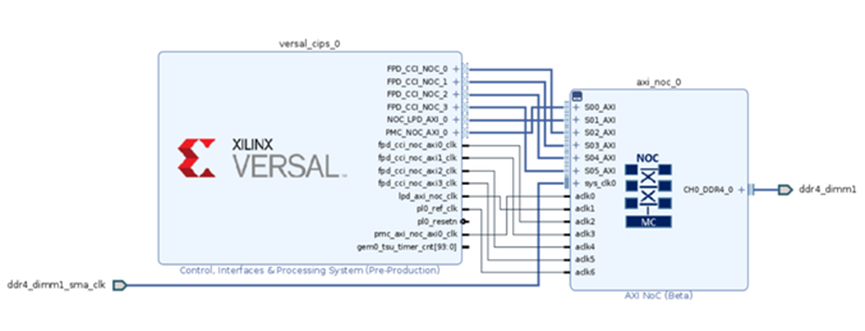

添加 versal_cips IP (Control, Interfaces and Processing System),并運(yùn)行塊自動化設(shè)置。在設(shè)置中配置 NoC 的存儲器控制器 (DDR4),并將 PL 時(shí)鐘和 PL 復(fù)位的數(shù)量配置為 1。

步驟 3:

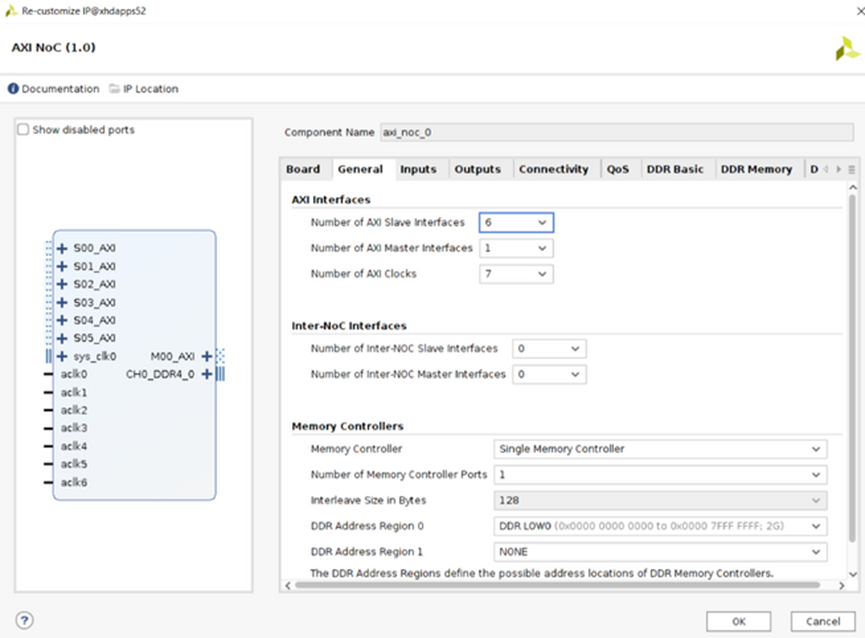

雙擊打開 NoC IP,在“General”(常規(guī))選項(xiàng)卡中進(jìn)行以下設(shè)置:

Number of AXI Master Interfaces(AXI 主接口數(shù))= 1

Number of AXI Clocks(AXI 時(shí)鐘數(shù))= 7

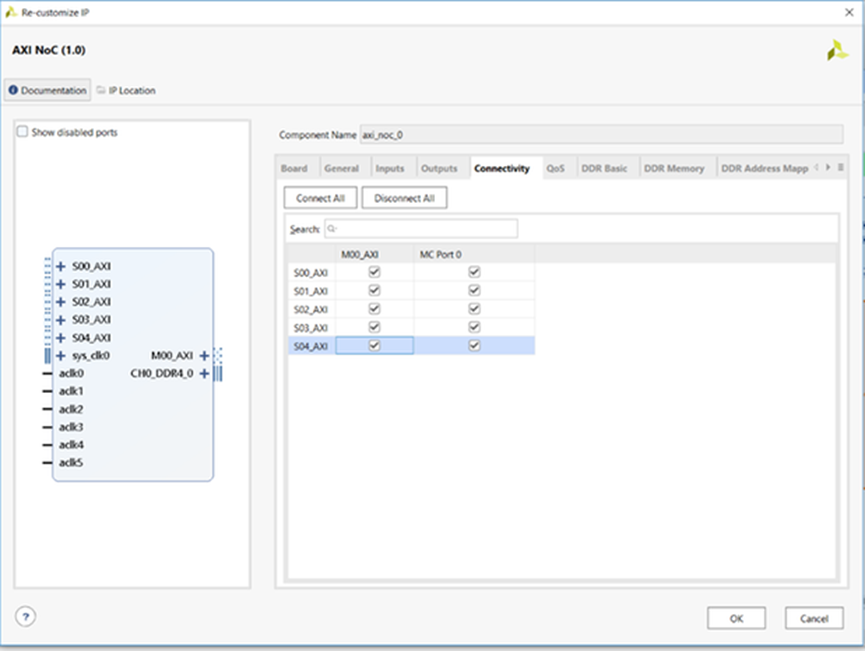

步驟 4:

轉(zhuǎn)至“Connectivity”(連接)選項(xiàng)卡,檢查 S0xAXI 與 M00_AXI 之間的連接,然后單擊“OK”(確定)。

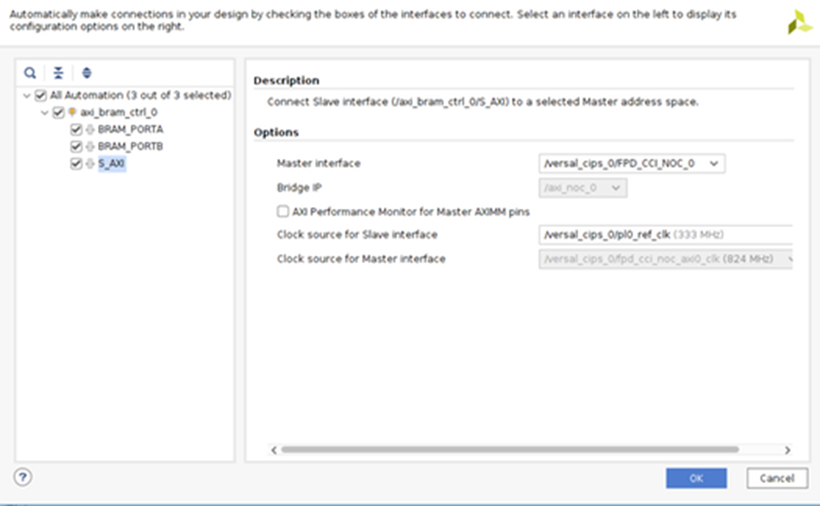

步驟 5:

將 AXI BRAM 添加到塊設(shè)計(jì)中,單擊“Run Connection Automation”(運(yùn)行自動連接),然后選中 pl_clk0 作為從接口的時(shí)鐘源。

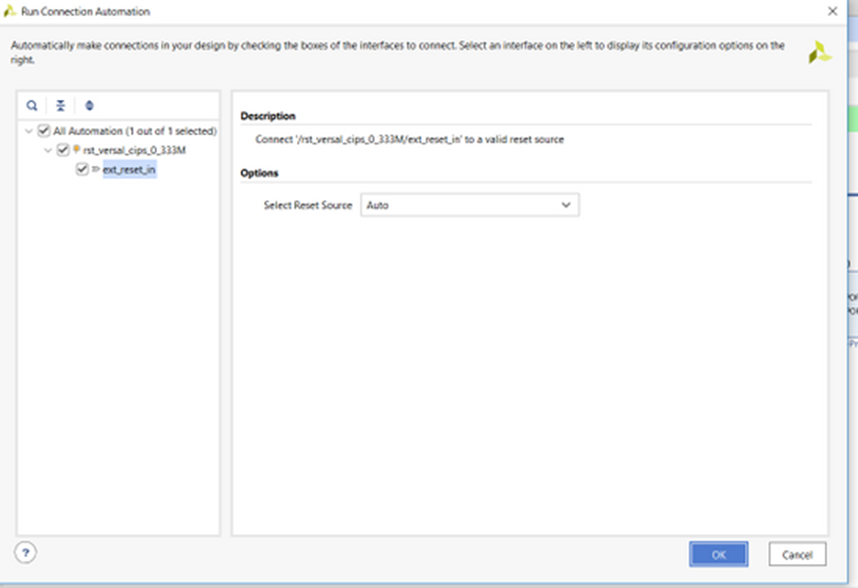

步驟 6:

再次運(yùn)行“Run Connection Automation”,配置 ext_reset_in接口。

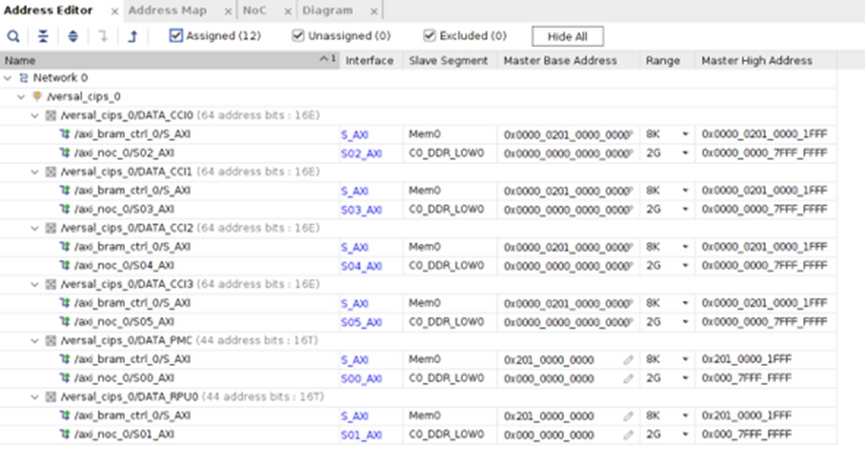

步驟 7:

運(yùn)行“validation”(確認(rèn))步驟,確認(rèn)成功后,檢查“Address Editor”(地址編輯器)選項(xiàng)卡。

步驟 8:

為 BD 創(chuàng)建頂層文件,運(yùn)行綜合與實(shí)現(xiàn),然后生成器件鏡像。

步驟 9:

導(dǎo)出硬件設(shè)計(jì)以獲取 XSA 文件。

Vitis 步驟

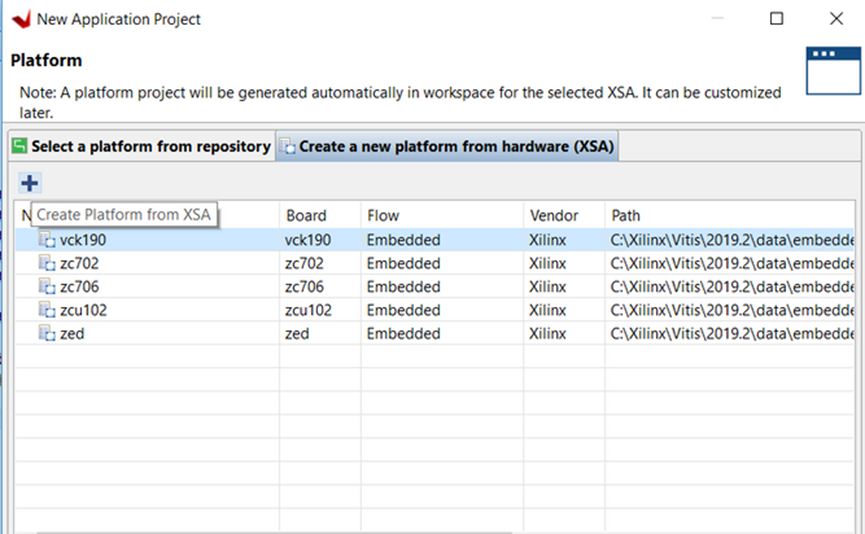

步驟 1:

在 Vitis 中創(chuàng)建新的應(yīng)用工程,然后切換至“Create a new platform from hardware”(基于硬件創(chuàng)建新平臺)選項(xiàng)卡。

單擊“+”,選擇從 Vivado 導(dǎo)出的 XSA 文件。

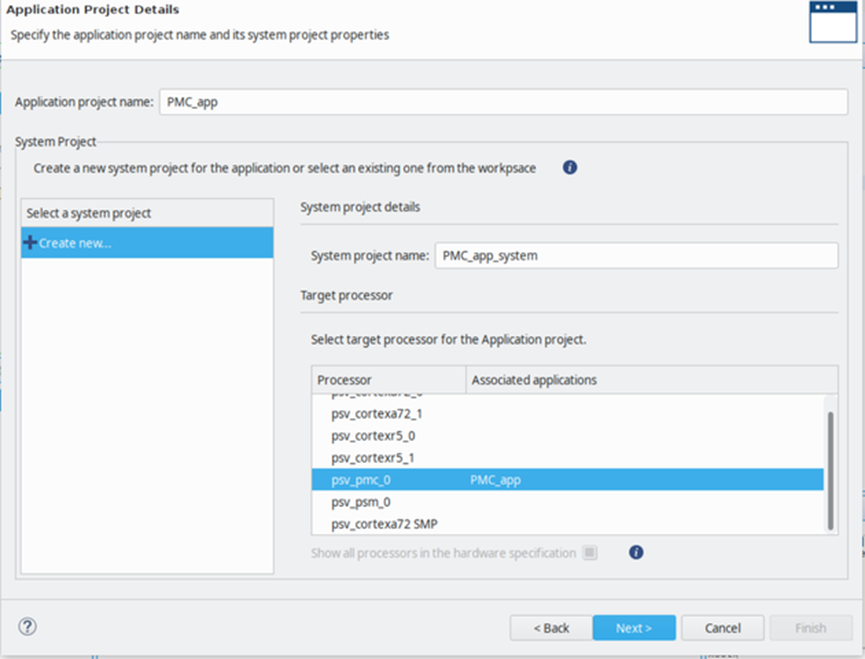

步驟 2:

提供工程名稱,并選擇處理器。

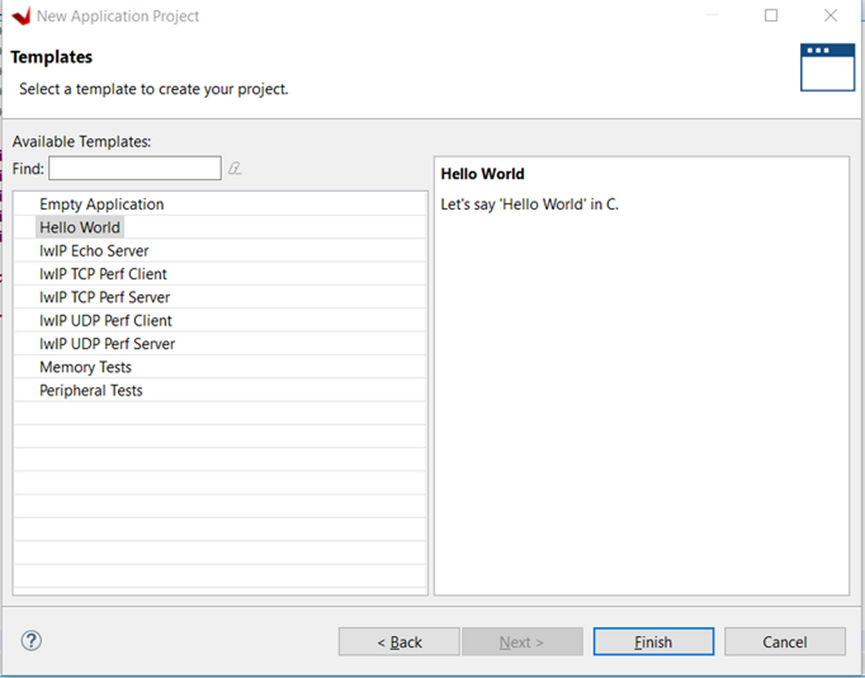

步驟 3:

選擇 Hello World 模板,然后單擊“Finish”(完成)。

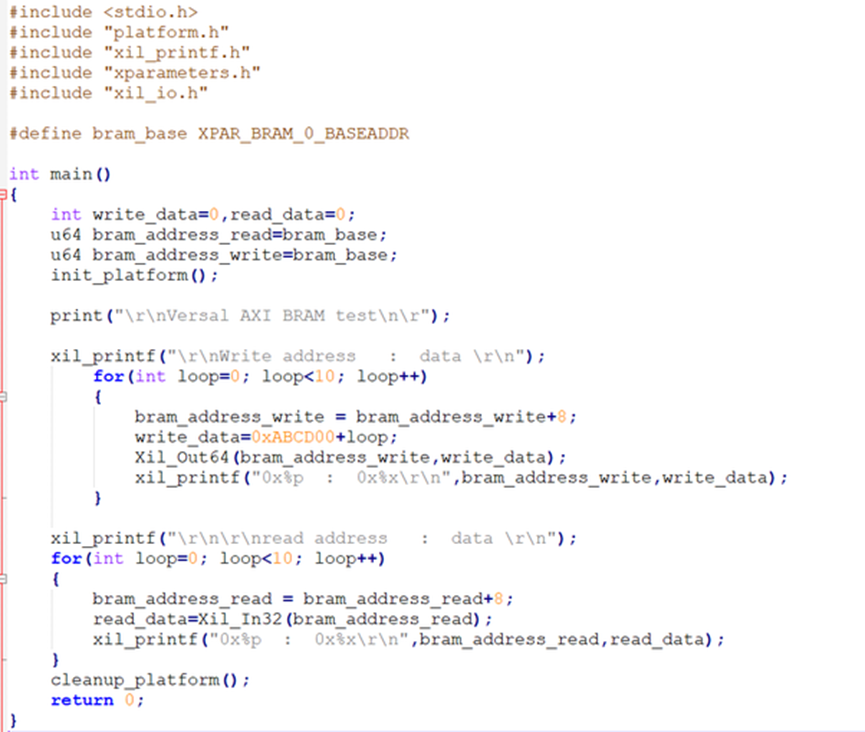

代碼修改

創(chuàng)建完應(yīng)用工程后,在 main.c 中修改代碼對 AXI BRAM進(jìn)行讀寫。

Xil_Out64 函數(shù)用于將數(shù)據(jù)寫入 64 位地址,而Xil_In32 函數(shù)則用于地址中讀取 32 位數(shù)據(jù)。

示例:

寫入數(shù)據(jù) API

Xil_Out64(bram_address_write,write_data);

讀取數(shù)據(jù) API

read_data=Xil_In32(bram_address_read);

代碼快照:

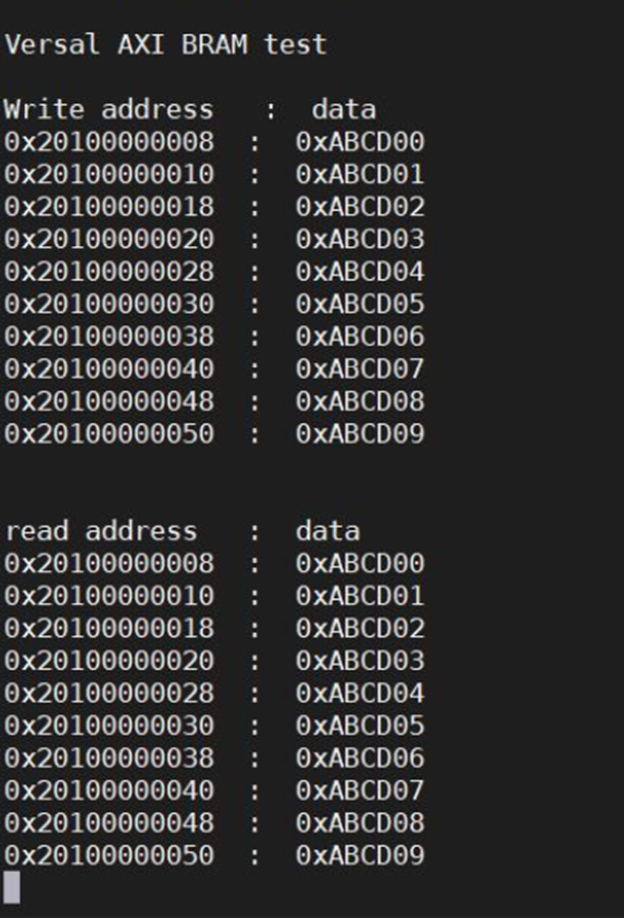

運(yùn)行設(shè)計(jì)

連接到VCK190 評估板,并設(shè)置啟動模式為 JTAG 啟動模式,然后運(yùn)行應(yīng)用。

控制臺輸出示例:

審核編輯:劉清

-

dsp

+關(guān)注

關(guān)注

552文章

7962瀏覽量

348262 -

存儲器

+關(guān)注

關(guān)注

38文章

7452瀏覽量

163605 -

APU

+關(guān)注

關(guān)注

0文章

141瀏覽量

23696 -

NoC

+關(guān)注

關(guān)注

0文章

38瀏覽量

11720 -

BRAM

+關(guān)注

關(guān)注

0文章

41瀏覽量

10942

原文標(biāo)題:在 Versal 中通過 NoC 從 PS-APU 對 AXI BRAM 執(zhí)行基本讀寫操作

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

AMD Versal AI Edge自適應(yīng)計(jì)算加速平臺之PL通過NoC讀寫DDR4實(shí)驗(yàn)(4)

如何在不使用DDR內(nèi)存控制器的情況下設(shè)計(jì)FPGA BRAM大容量存儲單元?

怎么使用AXI CDMA從OCM/DDR寫入BRAM

如何使用pcie鏈接從外部處理器訪問bram?

請問如何通過MicroBlaze訪問BRAM?

利用NoC資源解決FPGA內(nèi)部數(shù)據(jù)交換的瓶頸

如何利用NoC資源去支撐FPGA中的創(chuàng)新設(shè)計(jì)

從應(yīng)用角度詳解什么是AXI

應(yīng)用處理器芯片行業(yè)科普

加速處理單元 (APU) 革命

MicroBlaze大內(nèi)部存儲器(AXI BRAM)設(shè)計(jì)

在Versal中通過NoC從PS-APU對AXI BRAM執(zhí)行基本讀寫操作

如何通過NoC 從 Versal應(yīng)用處理單元訪問AXI BRAM

如何通過NoC從Versal應(yīng)用處理單元(APU)訪問AXI BRAM

Versal CPM AXI Bridge模式的地址轉(zhuǎn)換

如何通過NoC從Versal?應(yīng)用處理單元(APU)訪問AXI BRAM呢?

如何通過NoC從Versal?應(yīng)用處理單元(APU)訪問AXI BRAM呢?

評論