3.抖動(dòng)和信號(hào)集成( Jitter, SI )

抖動(dòng)是指信號(hào)的跳邊時(shí)刻偏離其理想(ideal)或者預(yù)定(expected)時(shí)刻的現(xiàn)象。噪聲,非理想的信道,非理想的電路都是產(chǎn)生抖動(dòng)的原因。

3.1 時(shí)鐘的抖動(dòng)(clock jitter)

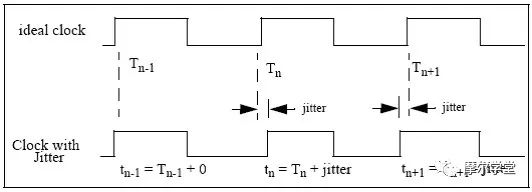

Figure 3.1 Clock Jitter

對(duì)于時(shí)鐘信號(hào),根據(jù)應(yīng)用場(chǎng)景的不同,對(duì)抖動(dòng)的定義也不一樣。比如數(shù)字邏輯計(jì)算時(shí)序余量的時(shí)候,關(guān)心的是周期抖動(dòng)。而時(shí)鐘設(shè)計(jì)人員更喜歡相位抖動(dòng),因?yàn)榭梢岳妙l譜評(píng)估相位抖動(dòng),并可以用頻譜來評(píng)估具體的干擾對(duì)總相位抖動(dòng)的貢獻(xiàn)。

參考圖3.1,介紹一下幾種抖動(dòng)的定義。

l 相位抖動(dòng)(phase jitter)

J phase (n)= tn – n*T。理想時(shí)鐘的每個(gè)周期T都是相等的,沒有抖動(dòng)。真實(shí)時(shí)鐘的跳邊沿相對(duì)于理想時(shí)鐘的偏離稱作相位抖動(dòng)。

l 周期抖動(dòng)(period jitter)

J period (n)= (t n - t n-1 )– T。周期抖動(dòng)是實(shí)際時(shí)鐘的周期相對(duì)于理想周期的偏離(deviation)。顯然J period (n) = J phase (n) - J phase (n-1)。

l Cycle-to-Cycle jitter

J cycle (n) = (t n - t n-1 ) - (t n-1 - t n-2 )。前后相鄰的兩個(gè)周期的偏差是Cycle-Cycle抖動(dòng)。顯然J cycle (n)= J period (n) – J period (n-1)。

假設(shè)相位抖動(dòng)的最大值為 +/-Jp, 而且抖動(dòng)的頻率fjitter = 0.5fclock = 0.5/T,也就是,

tn-2時(shí)刻的相位抖動(dòng)為最大值+Jp ,tn-1時(shí)刻的相位抖動(dòng)為最小值-Jp

tn時(shí)刻的相位抖動(dòng)為最大值+Jp , tn+1時(shí)刻的相位抖動(dòng)為最小值-Jp

那么,周期抖動(dòng)最大值 J period =+/- 2* Jp

那么,Cycle-Cycle抖動(dòng)最大值 Jcycle ~ =+/- 4* Jp~

3.2. 數(shù)據(jù)的抖動(dòng)(data jitter)

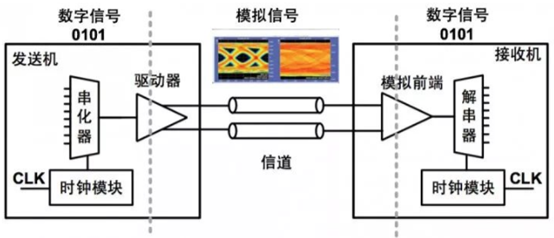

在高速SerDes領(lǐng)域每個(gè)人都在說抖動(dòng),因?yàn)槎秳?dòng)直接和誤碼率(BER)相關(guān)。

SerDes發(fā)送端的一個(gè)重要要求是抖動(dòng)(jitter generation)----針對(duì)特定的碼型(pattern),速率和負(fù)載情況下,發(fā)送端所生成的抖動(dòng)。

信號(hào)經(jīng)過信道(channel)到達(dá)接收端時(shí),又會(huì)進(jìn)一步放大抖動(dòng),不同的碼型(pattern)包含的頻率成分也不一樣,信道對(duì)不同頻率成分的傳輸延時(shí)也不一樣(非線性相位), 產(chǎn)生和數(shù)據(jù)pattern相關(guān)的確定性抖動(dòng)。阻抗不連續(xù)產(chǎn)生的反射,相鄰信號(hào)的串?dāng)_和噪聲都會(huì)引起數(shù)據(jù)抖動(dòng)。

SerDes接收端的一個(gè)重要指標(biāo)是抖動(dòng)容忍能力(Jitter Tolerance)----針對(duì)特定的碼型和誤碼率要求(BER<10 ^-12^ ),SerDes接收端能夠容忍的抖動(dòng)大小。對(duì)抖動(dòng)評(píng)估時(shí),會(huì)使用眼圖(eye-diagram),浴缸曲線(bath curve),抖動(dòng)分布柱狀圖(PDF),抖動(dòng)頻譜(jitter spectrum)等圖形手段。

有一點(diǎn)需要說明,在談?wù)摳咚賁erDes的數(shù)據(jù)抖動(dòng)時(shí)(Tj,Rj,Dj etc.),是不包括低頻率抖動(dòng)的。這是因?yàn)榈皖l率的抖動(dòng)被認(rèn)為是一種wander,可以被CDR跟蹤,不會(huì)引起誤碼。在用示波器(SDA)測(cè)量數(shù)據(jù)抖動(dòng)的時(shí)候,可以設(shè)置示波器內(nèi)嵌的CDR環(huán)路帶寬,示波器測(cè)量的抖動(dòng)數(shù)據(jù)已經(jīng)濾掉了低頻抖動(dòng)。

根據(jù)抖動(dòng)產(chǎn)生的原因和概率密度函數(shù),常常將抖動(dòng)分為幾類。對(duì)抖動(dòng)進(jìn)行分類的意義在于某些類型的抖動(dòng)可以被校正,而其他類型的不能被校正。經(jīng)典的,總抖動(dòng)Tj(Total Jitter)被分類為確定性抖動(dòng)Dj ( deterministic jitter )和隨機(jī)抖動(dòng)Rj ( random jitter )。抖動(dòng)以UI或者ps為單位,可以是均方根值,或者峰峰值。

3.2.1 Dj

Dj被進(jìn)一步細(xì)分,

l DCD( Duty cycle distortion )

占空比失真抖動(dòng)。差分信號(hào)的正端負(fù)端的偏置電壓不一致,或者上升沿和下降沿時(shí)間不一致會(huì)導(dǎo)致占空比失真。因?yàn)镈CD和數(shù)據(jù)pattern相關(guān),是可以被校正的抖動(dòng)。

l DDJ( Data dependent jitter )

數(shù)據(jù)碼型相關(guān)的抖動(dòng),也稱 碼間干擾ISI( intersymbol interference )。DDJ是由于不理想的信道導(dǎo)致。是可以被均衡器校正的抖動(dòng)。

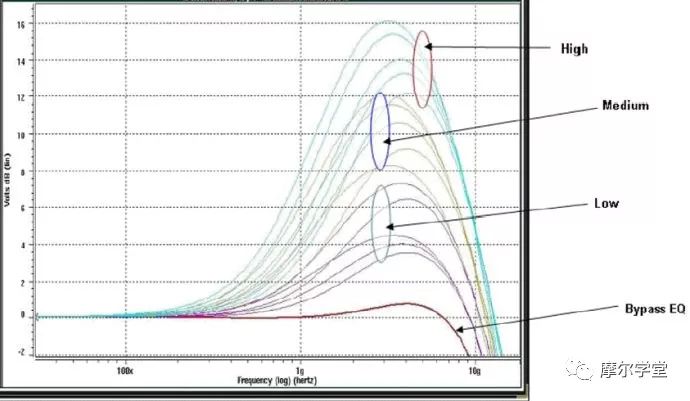

l Pj( Periodic jitter )

周期性抖動(dòng)。Pj由電路上周期性干擾源導(dǎo)致。比如開關(guān)電源的開關(guān)頻率,時(shí)鐘信號(hào)的串?dāng)_等。雖然電源的開關(guān)頻率一般在CDR的跟蹤范圍內(nèi),但是低次諧波成分可能會(huì)落在環(huán)路帶寬外,或者jitter peaking區(qū)域, 更重要的是電源諧波對(duì)CDR內(nèi)VCO的干擾是不能被抑制和跟蹤的,所以對(duì)于基于Ring VCO的CDR一定要盡可能的使用LDO供電。Pj不能被均衡器校正.

l BUJ( Bounded uncorrelated jitter )

BUJ由非時(shí)鐘的干擾源引起。如果干擾源aggressor和victim是異步的,抖動(dòng)的概率分布為有界的高斯分布,此時(shí)也稱作CBGJ( Correlated Bounded Gaussian Jitter )。BUJ/CBGJ不能被校正。

3.2.2 Rj

Rj有半導(dǎo)體本身的噪聲引起,一個(gè)重要特征就是Rj的概率密度函數(shù)是高斯分布的,沒有邊界,且和數(shù)據(jù)pattern無關(guān)。只有在一定誤碼率約束下,才可以被認(rèn)為是有界的。

3.2.3 Tj

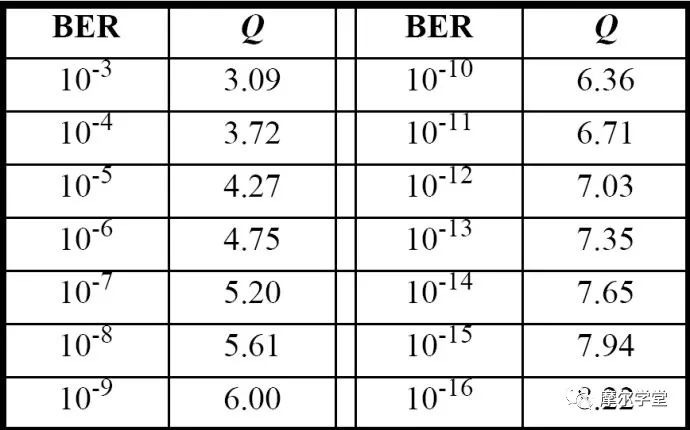

數(shù)學(xué)意義上,抖動(dòng)的概率分布函數(shù)可以近視為高斯分布和雙底拉克分布的卷積。

對(duì)高斯分布有貢獻(xiàn)的抖動(dòng)為:

n Rj為高斯分布

n 大量Pj疊加的效果也為高斯分布

n 部分BUJ也為高斯分布

對(duì)雙底拉克分布有貢獻(xiàn)的抖動(dòng)為:

n DCD被近視為雙底拉克概率分布

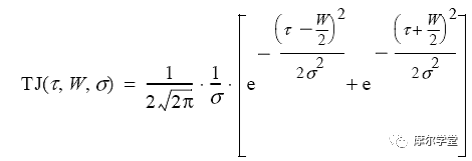

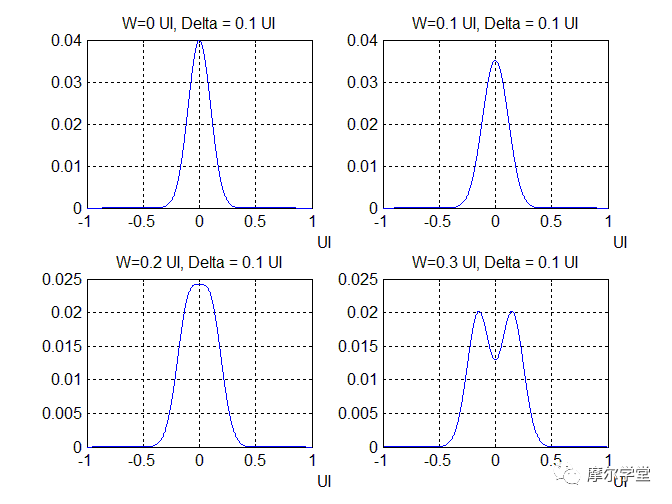

高斯分布和雙底拉克分布的卷積:

其中,W被認(rèn)為是確定性抖動(dòng)的峰峰值,δ是高斯分布的均方差。見圖3.2, 可以看到,隨著確定性抖動(dòng)W的增加,概率密度分布曲線的頂部出現(xiàn)了雙峰。一般來講頂部曲線反映了確定性抖動(dòng)的大小程度。

Figure 3.2 PDF of Tj with different Dj and Rj

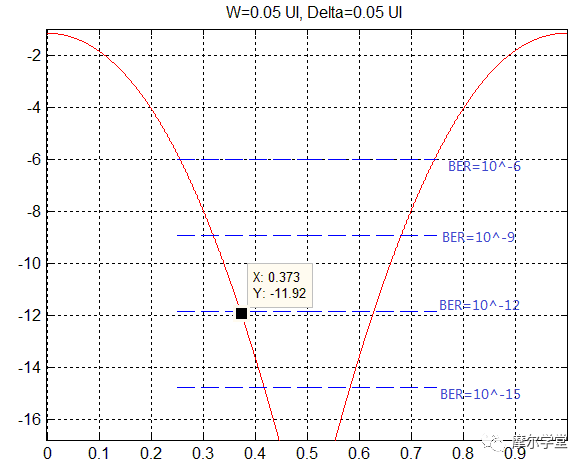

把一個(gè)UI內(nèi)的兩個(gè)跳變沿處(0 UI處和1UI處)的概率分布函數(shù)放在一張圖中,就是抖動(dòng)的浴缸曲線( bathtub curve )。因?yàn)閷?duì)數(shù)的寬動(dòng)態(tài)范圍,Y坐標(biāo)以對(duì)數(shù)顯示。圖3.3為確定性抖動(dòng)W=0.05UI, 高斯抖動(dòng)方差0.05UI的浴缸曲線。

Figure 3.3 Bathtub Curve of Tj with 0.05 Dj peak and 0.05 Rj RMS

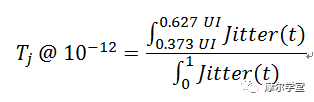

浴缸曲線還會(huì)標(biāo)出對(duì)應(yīng)的誤碼率BER坐標(biāo),比如圖中BER=10^-12的峰峰值抖動(dòng)為Tj(p-p)=0.373*2 = 0.746 UI。曲線下面的面積占總面積的比率就是誤碼率。比如圖中,

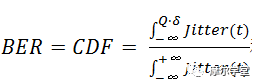

浴缸曲線的頂部主要為確定性抖動(dòng)Dj的貢獻(xiàn),越靠近底部,高斯抖動(dòng)的貢獻(xiàn)越大,并以高斯曲線的斜率衰減,也因此常利用高斯分布的特性進(jìn)行估算。下表為高斯分布

和均方差關(guān)系。

在規(guī)定的BER內(nèi),利用該表可以快速估算均方差值和峰峰值之間的關(guān)系。比如高斯抖動(dòng)的均方根0.05UI,誤碼率要求為10^-12 BER,查表可知Q=7,那么高斯抖動(dòng)的峰峰值要求是0.05UI72 = 0.7UI。

如前所述,W=0.05UI,Rj=0.05UI計(jì)算出的總抖動(dòng)Tj=0.746UI;

利用高斯特性估算的高斯抖動(dòng)為0.7UI。

如果按Tj = Rj(0.7UI)+Dj(0.05UI)計(jì)算得到0.75U,基本是一致的,差異是因?yàn)楫媹D程序有量化誤差。

4.信號(hào)集成(SI)及仿真

4.1信道channel

SerDes信道關(guān)注的頻率范圍是0Hz到奈奎斯特頻率,也就是2倍的信號(hào)基頻。信號(hào)的基頻是信號(hào)線速率的一半,也就是說信號(hào)的奈奎斯特頻率就是線速率。信道對(duì)信號(hào)的損傷包括插入損失(insertion loss),反射 (reflection),串?dāng)_(crosstalk)等。這些損傷可以用S-parameter信道模型來表達(dá)。S-parameter可以有矢量網(wǎng)絡(luò)分析儀測(cè)量(Vector Network Analyzer)得到。信道不是一個(gè)純阻性網(wǎng)絡(luò),還包括容性和感性。這樣對(duì)不同頻率里成分的時(shí)延也不一樣,從而產(chǎn)生和data pattern相關(guān)的抖動(dòng)。

信道上的每一個(gè)不連續(xù)阻抗點(diǎn)都會(huì)產(chǎn)生反射,根據(jù)反位置的不同,反射信號(hào)會(huì)以不同的相位疊加在原始信號(hào)上,增加或者減小信號(hào)的幅度。

SerDes信號(hào)為差分形式,對(duì)共模干擾有較強(qiáng)的抑制。如果在+/-端上的干擾有差異,就會(huì)引入串?dāng)_。通常外部PCB可以保證SerDes數(shù)據(jù)和干擾源保持足夠的距離,但是芯片內(nèi)部由于考慮到經(jīng)濟(jì)性,很難保證SerDes信號(hào)和干擾源足夠的隔離距離,尤其是一個(gè)通道自己的發(fā)送信號(hào)干擾自己的接收信號(hào)。

4.2 芯片封裝Package

封裝package也是信道的一部分。芯片外部的信道可以通過VNA測(cè)量的到,而封裝的S-parameter通常有芯片制造商提供,仿真時(shí)可以把兩者級(jí)聯(lián)起來。封裝package由于距離較短,insertion loss通常不是主要問題,主要考慮的是阻抗匹配問題。

4.3 SI仿真

信號(hào)集成性(SI)仿真可以通過把SerDes發(fā)送端SPICE模型,封裝和信道的S-parameter模型,接收端SPICE模型級(jí)聯(lián)起來搭建仿真平臺(tái),利用仿真工具對(duì)不同的激勵(lì)在不同的測(cè)試條件作電路仿真。通過測(cè)量SerDes接收端的眼圖來評(píng)估是否滿足設(shè)計(jì)需求。也可以通過實(shí)測(cè)接收端眼圖,檢驗(yàn)是否滿足接收端的眼圖模板,或者協(xié)議規(guī)定的眼圖模板。圖4.1為一個(gè)實(shí)測(cè)的3.125Gbps信號(hào)的眼圖及模板,同時(shí)也包含了浴缸曲線和統(tǒng)計(jì)圖。

Figure 4.1 Rx-end Eye-diagram of A 3.125Gbps SerDes

對(duì)于高速SerDes(>5Gbps),這種傳統(tǒng)的電路仿真方法已經(jīng)不能滿足設(shè)計(jì)的需求。首先,過量的碼間干擾ISI導(dǎo)致接收端眼圖完全閉合,但是通過芯片內(nèi)的DFE均衡后,眼圖可能是很好的。其次,電路仿真(SPICE)的速度非常慢,即使是有辦法把DFE均衡加入仿真,由于DFE仿真需要足夠長時(shí)間的bits來訓(xùn)練,此時(shí),電路仿真的仿真時(shí)間是不可接受的。

對(duì)于高速SerDes的仿真需要借助統(tǒng)計(jì)分析 (statistical analysis) 的方法。統(tǒng)計(jì)分析的方法把發(fā)送端-信道-接收端的連接近視為線性系統(tǒng),計(jì)算系統(tǒng)脈沖響應(yīng)h(t),加入噪聲源來模擬抖動(dòng),然后用激勵(lì)對(duì)脈沖響應(yīng)進(jìn)行卷積,得到接收端的信號(hào),這種方法可以把廠家私有的FFE,DFE自適應(yīng)算法加入仿真。

統(tǒng)計(jì)分析 (statistical analysis)方法不能仿真電路的非線性和時(shí)變特性,所以高速SerDes往往要兩者結(jié)合起來仿真SI。更多關(guān)于統(tǒng)計(jì)分析 (statistical analysis)方法可以參考。

-

仿真

+關(guān)注

關(guān)注

50文章

4048瀏覽量

133431 -

SerDes

+關(guān)注

關(guān)注

6文章

197瀏覽量

34861 -

FFE

+關(guān)注

關(guān)注

0文章

8瀏覽量

1143 -

dfet

+關(guān)注

關(guān)注

0文章

2瀏覽量

2118

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

SerDes的技術(shù)原理 SerDes的重要概念和技術(shù)概述

SerDes是怎么工作的

SN65LVDS95,pdf(LVDS Serdes Tra

Evaluate Serializer-Deserializ

符合EMIEMC標(biāo)準(zhǔn)的SerDes—基本測(cè)試策略和指南

An Introduction to Preemphasis and Equalization in Maxim GMSL SerDes Devices

SerDes的基本結(jié)構(gòu)

什么是差分信號(hào),差分信號(hào)的優(yōu)缺點(diǎn)分析

深度解讀SerDes(Serializer-Deserializer)1

SerDes的基礎(chǔ)知識(shí)

SerDes是怎么設(shè)計(jì)的?(一)

什么是SerDes呢?為什么我們需要此項(xiàng)技術(shù)呢?有哪些設(shè)計(jì)要求和技巧?

汽車以太網(wǎng)發(fā)明人押寶SerDes!一文詳解車載SerDes技術(shù)

深度解讀SerDes(Serializer-Deserializer)3

深度解讀SerDes(Serializer-Deserializer)3

評(píng)論