什么是數(shù)字 IC 設(shè)計(jì)?

數(shù)字 IC 設(shè)計(jì)是一個(gè)程序過(guò)程,涉及將規(guī)格和功能轉(zhuǎn)換為數(shù)字塊,然后進(jìn)一步轉(zhuǎn)換為邏輯電路。許多與數(shù)字 IC 設(shè)計(jì)相關(guān)的限制來(lái)自代工工藝和技術(shù)限制。

設(shè)計(jì)技能和獨(dú)創(chuàng)性是數(shù)字 IC 設(shè)計(jì)的更高級(jí)別階段以及確保設(shè)計(jì)盡可能高效地滿足規(guī)范的系統(tǒng)和流程開(kāi)發(fā)的關(guān)鍵。

1、綜合與驗(yàn)證:硬件描述語(yǔ)言與功能驗(yàn)證

在數(shù)字設(shè)計(jì)的早期階段開(kāi)發(fā)的具有行為描述的數(shù)字模塊需要轉(zhuǎn)換為硬件描述語(yǔ)言 (HDL),例如 Verilog 或 VHDL。這個(gè)階段通常被稱(chēng)為寄存器傳輸級(jí) (RTL) 階段,它通常包括功能驗(yàn)證,以確保邏輯實(shí)現(xiàn)符合高層規(guī)范。

(a) HDL 代碼示例和 (b) 它描述的電路

在這一步之后,硬件描述然后被轉(zhuǎn)換成門(mén)級(jí)網(wǎng)表,在此期間可以嘗試各種實(shí)現(xiàn)和優(yōu)化例程以更好地滿足設(shè)計(jì)目標(biāo)。此階段的重要考慮因素包括功率預(yù)算、速度、占地面積和可靠性。

2、物理 IC 布局:布局規(guī)劃和 IP 核

經(jīng)過(guò)綜合驗(yàn)證后,門(mén)級(jí)網(wǎng)表轉(zhuǎn)化為物理版圖,即IC的層級(jí)和物理結(jié)構(gòu)的幾何表示。布局規(guī)劃方法用于確保整個(gè) IC 中的塊和焊盤(pán)布局符合設(shè)計(jì)目標(biāo)。

由于某些數(shù)字模塊(例如存儲(chǔ)器和寄存器)的結(jié)構(gòu)化和重復(fù)性,部分?jǐn)?shù)字 IC 布局通常使用腳本和自動(dòng)化軟件流程完成。外部 IP 核也在此階段放置,其中軟件僅顯示 IP 的必要接口部分。在放置所有塊和門(mén)之后——以及手動(dòng)布線,如有必要——布線自動(dòng)化腳本和軟件用于連接每個(gè)元素。

3、驗(yàn)證和模擬:流片和測(cè)試

然后執(zhí)行驗(yàn)證和模擬,兩者都必須考慮布局的布局和物理特征。如果成功,結(jié)果是一個(gè)輸出文件,例如 GDSII (GDS2),代工廠使用內(nèi)部軟件和流程來(lái)制造 IC,即流片階段。在某些情況下,代工廠會(huì)發(fā)現(xiàn)設(shè)計(jì)問(wèn)題,然后需要設(shè)計(jì)團(tuán)隊(duì)糾正/確認(rèn)。

M00/81/D4/wKgZomQSf8WAMkDRABZ936qOS4A939.jpg) 布局和布線后的芯片布局。圖片由 Cadence Design Systems 提供。

流片后,會(huì)生產(chǎn)小批量的首次運(yùn)行或原型 IC,以便進(jìn)行測(cè)試。根據(jù)生產(chǎn) IC 的性能和經(jīng)濟(jì)性,此測(cè)試可能會(huì)導(dǎo)致重新設(shè)計(jì)或工藝更改。

數(shù)字集成電路抽象級(jí)別

- 行為的

- 寄存器傳輸級(jí) (RTL)

- 功能性

- 門(mén)

- 晶體管

- 物理布局

數(shù)字 IC 設(shè)計(jì)流程

- 以下列表概述了數(shù)字 IC 設(shè)計(jì)流程中的步驟,包括子步驟:

- 設(shè)計(jì)規(guī)范

- 規(guī)格

- 約束

- 測(cè)試臺(tái)開(kāi)發(fā)

- 高級(jí)系統(tǒng)設(shè)計(jì)

- 設(shè)計(jì)分區(qū)

- 入門(mén) Verilog 行為建模

- 模擬/功能驗(yàn)證

- 集成與驗(yàn)證

- 邏輯綜合

- 寄存器傳輸級(jí) (RTL) 轉(zhuǎn)換為網(wǎng)表

- 設(shè)計(jì)劃分為物理塊

- 時(shí)序裕量和時(shí)序約束

- RTL和門(mén)級(jí)網(wǎng)表驗(yàn)證

- 靜態(tài)時(shí)序分析

- 平面規(guī)劃

- 合成

- 時(shí)序約束和優(yōu)化

- 靜態(tài)時(shí)序分析

- 更新展示位置

- 更新電源和時(shí)鐘規(guī)劃

- 塊級(jí)布局

- 完整的塊布局和布線

- IC 級(jí)布局

- 所有模塊的IC集成

- 單元格放置

- 掃描鏈/時(shí)鐘樹(shù)插入

- 信元路由

- 物理和電氣設(shè)計(jì)規(guī)則檢查 (DRC)

- 布局與原理圖 (LVS)

- 寄生提取

- 布局后時(shí)序驗(yàn)證

- GDSII 創(chuàng)建

- 流片

-

邏輯電路

+關(guān)注

關(guān)注

13文章

494瀏覽量

42580 -

HDL

+關(guān)注

關(guān)注

8文章

327瀏覽量

47339 -

數(shù)字IC

+關(guān)注

關(guān)注

1文章

37瀏覽量

12512

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

一文讀懂DS18B20溫度傳感器及編程

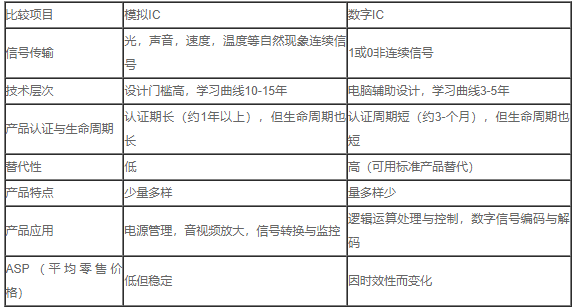

一文讀懂模擬IC與數(shù)字IC差異

一文讀懂模擬IC與數(shù)字IC的區(qū)別

一文讀懂什么是數(shù)字 IC 設(shè)計(jì)

一文讀懂什么是數(shù)字 IC 設(shè)計(jì)

評(píng)論