算術運算電路

算術運算電路的核心為加法器.

基本加法器

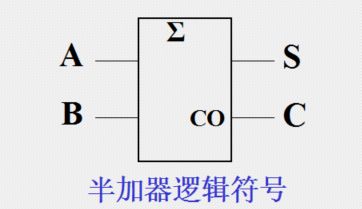

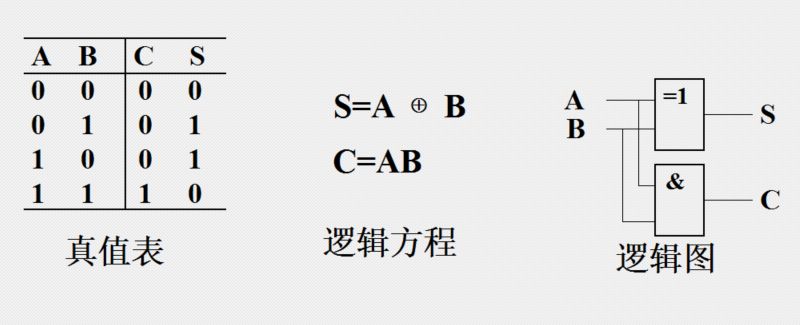

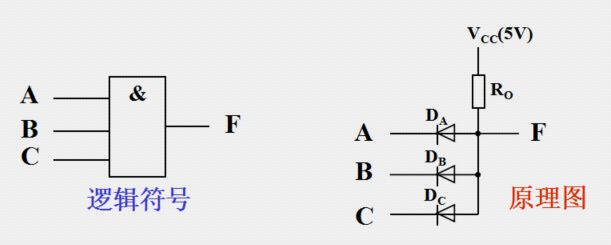

1. 半加器(HA)

僅考慮兩個一位二進制數(shù)相加,而不考慮低位的進位,稱為半加。

設: A、B為兩個加數(shù),S 為本位的和,C 為本位向高位的進位。則半加器的真值表、方程式、邏輯圖如下所示

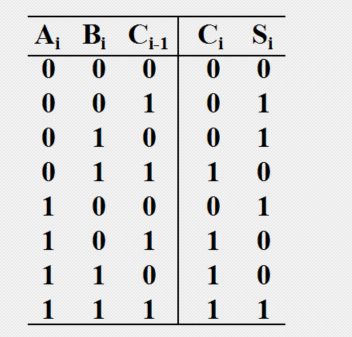

2. 全加器

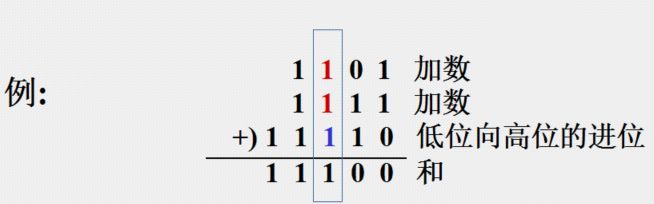

在多位數(shù)相加時,除考慮本位的兩個加數(shù)外,還須考慮低位向本位的進位.

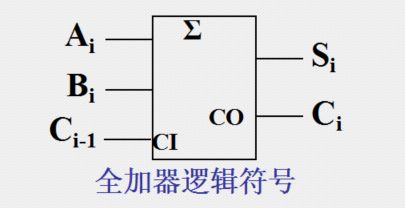

實際參加一位數(shù)相加,必須有三個量,它們是:

本位加數(shù) Ai 、Bi ;

低位向本位的進位 Ci-1

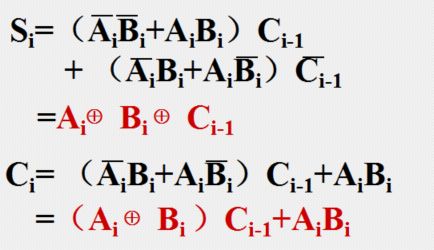

一位全加器的輸出結(jié)果為:

本位和 Si ;

本位向高位的進位 Ci

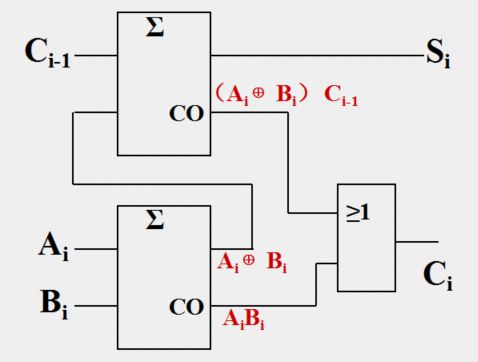

全加器電路設計:

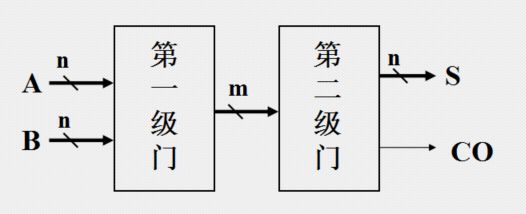

由兩個半加器實現(xiàn)一個全加器

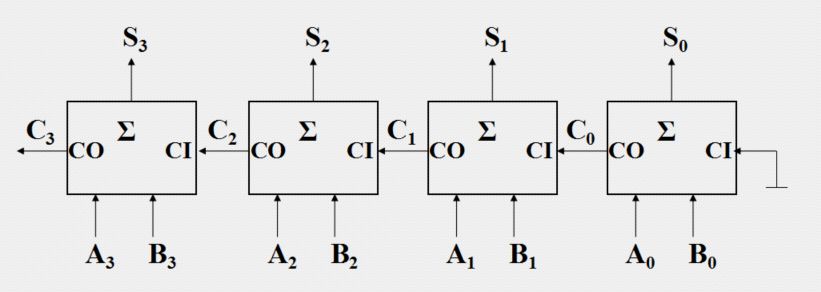

3. 串行進位加法器

當有多位數(shù)相加時,可模仿筆算,用全加器構成串行進位加法器.

四位串行進位加法器

串行進位加法器特點: 結(jié)構簡單; 運算速度慢.

高速加法器

(1) 全并行加法器

特點: 速度最快,電路復雜。

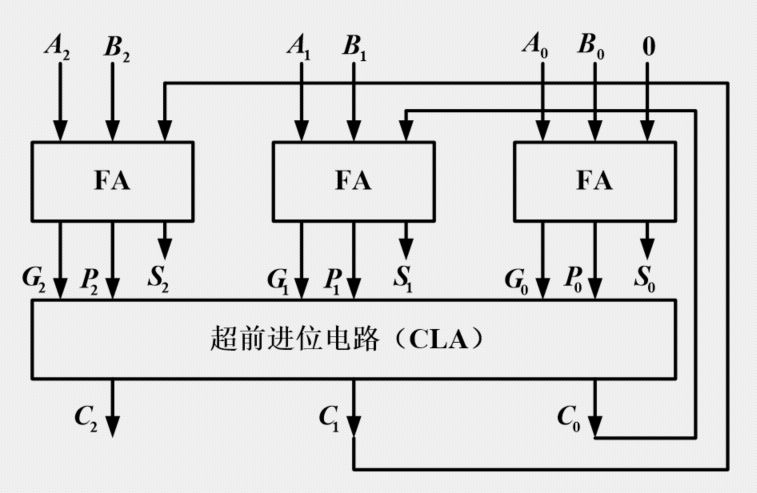

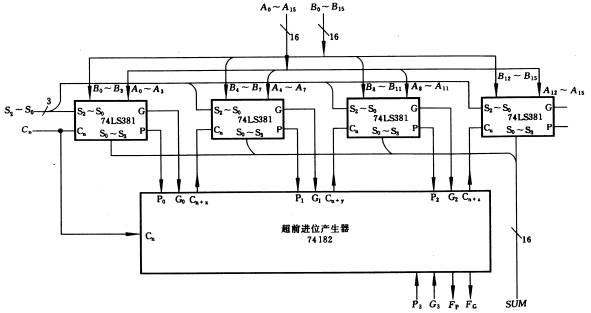

(2) 超前進位加法器

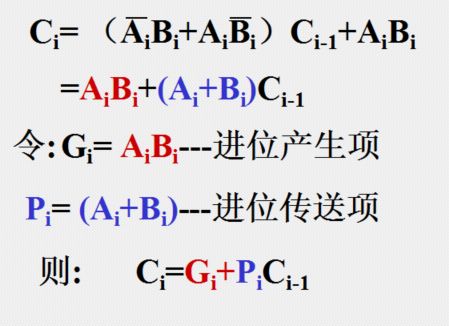

設計思想: 由兩個加數(shù),首先求得各位的進位,然后再經(jīng)全加器算出結(jié)果.

全加器的進位表達式:

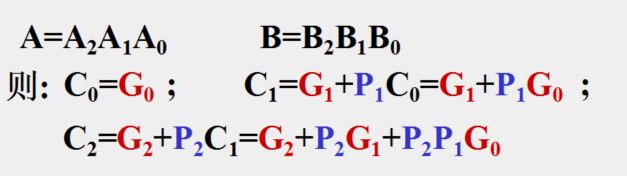

若兩個三位二進制數(shù)相加

由Pi 、Gi 并經(jīng)過兩級門電路就可求得進位信號C.實際實現(xiàn)中,是將求Gi和Pi的電路放進全加器中,而將全加器中求進位信號的電路去除.

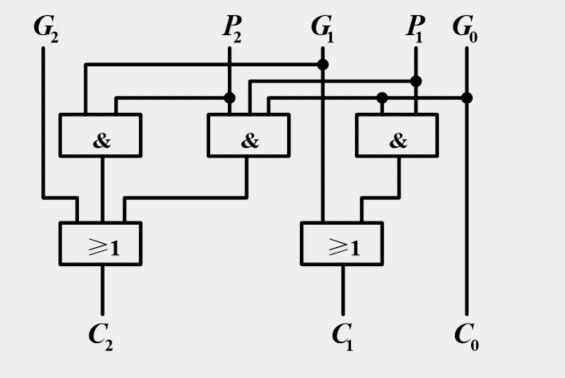

根據(jù)Gi 、Pi 來求進位信號C 的電路稱為超前進位電路(CLA)

CLA邏輯圖:

3位超前進位加法器

-

電路設計

+關注

關注

6637文章

2398瀏覽量

201148 -

運算電路

+關注

關注

8文章

114瀏覽量

26645 -

二進制

+關注

關注

2文章

761瀏覽量

41476 -

加法器

+關注

關注

6文章

183瀏覽量

29970 -

全加器

+關注

關注

10文章

59瀏覽量

28343

發(fā)布評論請先 登錄

相關推薦

可變精度算術運算

LabVIEW對8-bit圖像進行濾波或算術運算

MCS-51算術運算指令

算術運算指令

多功能算術/邏輯運算單元(ALU) ,什么是多功能算術/邏輯

一文讀懂如何驗證74ls181運算和邏輯功能

一文詳解算術運算電路

一文詳解算術運算電路

評論