SRAM也是易失性存儲器,但是,與DRAM相比,只要設備連接到電源,信息就被存儲,一旦設備斷開電源,就會失去信息。

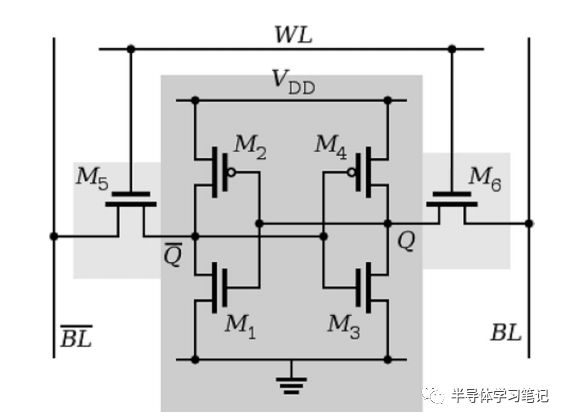

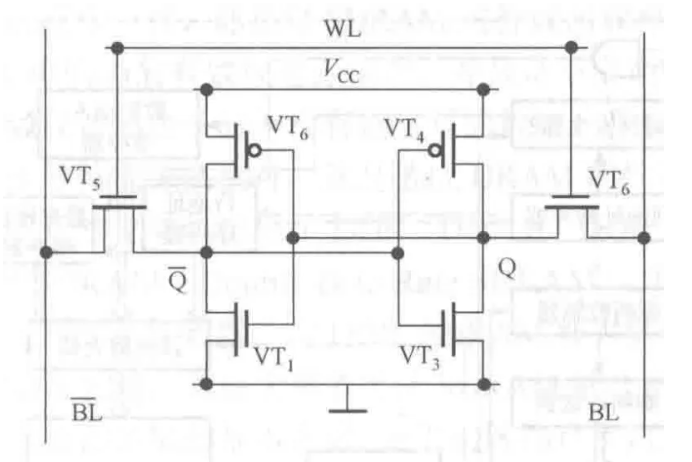

這個設備比DRAM要復雜得多,它一般由6個晶體管組成,因此被稱為6T存儲器(如圖1)。

SRAM的每一bit存儲在由4個場效應管M1,M2,M3,M4構成的兩個交叉耦合的反相器(如圖1中深灰色的部分)中。另外兩個場效應管(M5,M6)是存儲基本單元到用于讀寫的位線(Bit Line)的控制開關。這種設置,是典型的CMOS工藝,相當于一個“RS鎖存器”電路(如圖2),只要系統是穩定的供電狀態,可以存儲信息‘0’或‘1’(即:邏輯等效的低或高電壓)。

圖1 6晶體管SRAM存儲器的功能圖

圖2 SRAM存儲器的等效電路圖

根據上圖可以看出,一個6晶體管SRAM存儲器包括由交叉逆變器M1-M2和M3-M4構成的鎖存器和兩個存取晶體管M5和M6。M1-M2逆變器的輸入信號Q與M3-M4逆變器的輸出相連接,M3-M4逆變器的輸入信號Q_與M1-M2逆變器的輸出反向連接。M5和M6晶體管類似于由字線WL驅動的兩個開關,該開關同時使這些晶體管的柵極極化,并允許兩位線BL讀取存儲的信息。

存儲在鎖存器中的兩個二進制信號Q和Q_(‘0’和‘1’或‘1’和‘0’)通過兩個存取晶體管M5和M6(淺灰色區域)傳輸到兩個位線(B_L_和BL),M5和M6(淺灰色區域)由連接到M5和M6的每個柵極的字線WL打開或關閉。

存儲器的操作可以概括為三個功能:備用、讀、寫或擦。

備用功能對應于鎖存器中信息‘0’或‘1’的保持,是通過字線(WL)在兩個N型MOSFET M5和M6的柵極處施加負電壓或低電壓,使它們不導電的狀態,相當于將鎖存器與兩個位線(BL)隔離。這就實現了鎖存器里面的信號不變的狀態。

而另一方面,讀取操作則是通過將鎖存器與兩個位線(BL)通信來獲得的。連接到兩個位線BL的感測放大器(不在這里進行闡述)識別哪一行具有更強的信號,從而讀取由位線BL攜帶的初始信息。感測放大器是連接到兩個互補的位線(‘0’和‘1’)兩端的電子器件,其功能是在放大兩個位線之間的電壓差后,識別其中哪個具有‘0’或‘1’的邏輯狀態。

寫入和擦除操作則是通過打開晶體管M5和M6的通道和在兩個位線BL上施加‘0’和‘1’來實現的。

從實際角度來看,SRAM存儲器速度非常快,換相時間只有數十納秒,這使得它們比DRAM快10倍。對于DRAM來說,循環次數(寫——擦除)幾乎是無限的(>10 ^16^ )。雖然SRAM在切斷電源時是易失信息的,但它不需要定期更新,使它在能耗方面比DRAM更有利。但不幸的是,SRAM的復雜性使得它們的制造成本很高,而且它們的大尺寸(面積>140 F ^2^ )不允許高的集成密度。因此,它們在計算機中的使用僅限于低容量的高速緩存內存,用于高速執行重復操作,從而大大縮短了復雜操作的執行時間。

附加介紹:

CMOS反相器是一種電路器件,其輸出是輸入的邏輯非,即:它給出與輸入信號IN相反的輸出信號OUT。對于邏輯數據,是通過輸入和輸出電壓轉換成邏輯數據‘0’和‘1’來實現的。因此,輸入低的“IN”電壓信號(編碼‘0’),我們將得到一個強的“輸出”電壓信號(編碼‘1’),并且,如果“IN”是強的(‘1’),則“OUT”是低的(‘0’)。

如圖所示,CMOS靜態反相器,采用倒置CMOS工藝,由兩個互補的MOSFET組成,將N型和P型MOSFET的串聯組合,即將P-MOSFET的源與N-MOSFET的漏極連接起來。P-MOSFET的漏極被引入一個電壓V DD (邏輯信號‘1’),而N-MOSFET的源被接地(邏輯信號‘0’)。這兩個柵極互相連接,輸入信號“IN”被應用到它們身上。輸出信號‘OUT’分別在P和N-MOSFET的源和漏點測量(如上圖)。則當輸入低電平,則P溝道場效應管開通,N溝道場效應管關閉,輸出高電平;當輸入高電平,N溝道場效應管開通,P溝道場效應管關閉,輸出低電平。這就實現了“反相”輸出。

從象征意義上說,逆變器由(b)表示,其中A是輸入信號,A_是輸出信號。

CMOS逆變特性

當柵極電壓較低(IN=‘0’)時,N和P晶體管的通道分別關閉和打開,這意味著輸出信號處于電壓V DD ,因此OUT=‘1’(c)。

相反,當柵極電壓較高(IN=‘1’)時,P和N晶體管分別為非導電(開)和導電(閉合),從而導致輸出直接接地,從而使輸出。

-

DRAM

+關注

關注

40文章

2304瀏覽量

183326 -

存儲器

+關注

關注

38文章

7455瀏覽量

163623 -

sram

+關注

關注

6文章

764瀏覽量

114638

發布評論請先 登錄

相關推薦

SRAM的工作原理及其使用方法了解

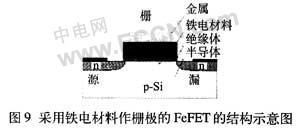

鐵電存儲器工作原理和器件結構

如何選擇最適用的sram存儲器

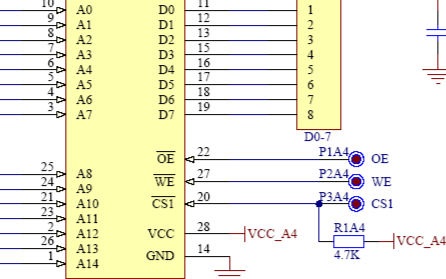

淺談異步SRAM存儲器接口電路圖

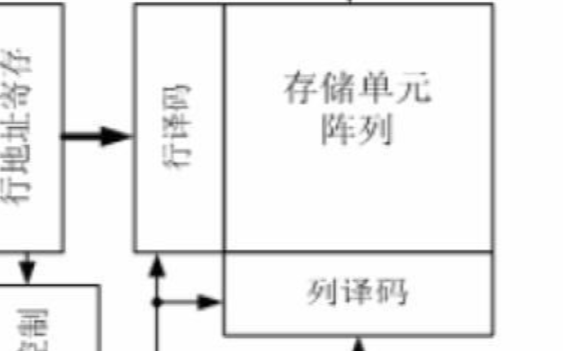

SRAM隨機存儲器的特點及結構

SRAM隨機存儲器的特點及結構

SRAM存儲器的工作原理

SRAM存儲器的工作原理

評論