由于擁有較高的分辨率和采樣率,SAR型ADC一直被眾多工業和汽車客戶所親睞。但是SAR型ADC由于其特殊的特性,所以對外圍電路也相應的提出很多“特殊需求”。

首先就是抗混疊電路的需求。例如當電路中的SAR型ADC采樣率為fs時,根據香濃采樣定律,輸入信號的頻率需要小于fs/2,頻率超過fs/2的信號將會通過混疊效應“混入”有用信號頻帶中,并且無法區分。因此,為了避免混疊的問題,絕大部分SAR型ADC電路需要在前端設計專用的多階有源濾波器,濾掉頻率超過fs/2的信號。(注:Σ-Δ型ADC理論上也需要抗混疊濾波器,但是由于其過采樣特性及內部數字濾波器的帶外衰減特性,其對抗混疊濾波器的設計要求要低很多,多數情況下一階RC電路能夠滿足抗混疊需求。)

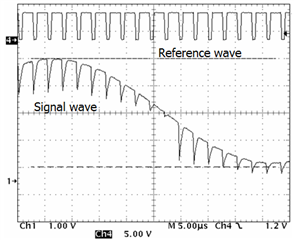

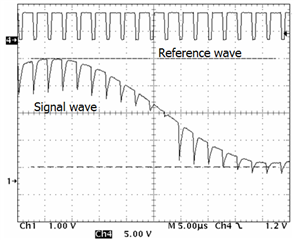

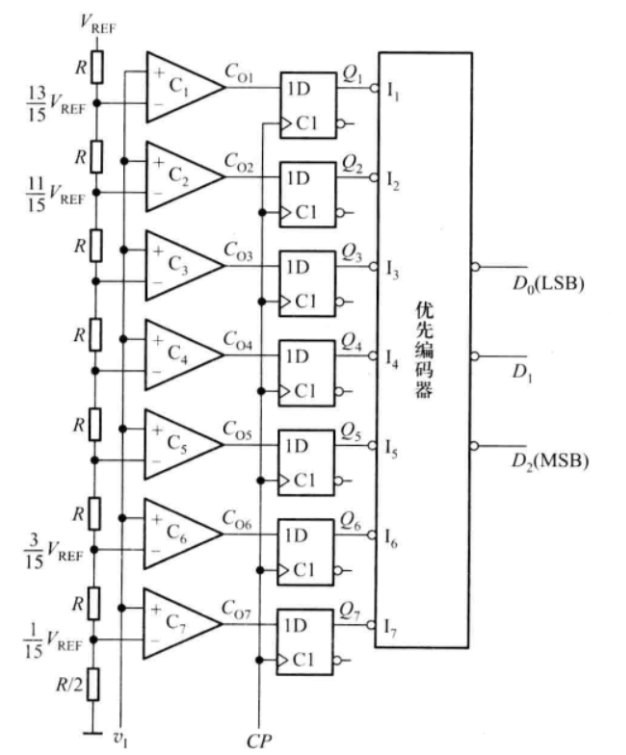

其次是模擬輸入與基準輸入的驅動問題。不同于大學課本上講到的,現在市面上流行的大部分SAR型ADC不再是通過分壓電阻網絡來實現電壓的逐次逼近,由于CMOS工藝的普及,取而代之的是通過內部電容網絡實現電荷的逐次逼近,這樣無論是ADC的信號輸入端還是基準輸入端,都是通過一個電容采樣,這個電容一般為幾個皮法到幾十個皮法。這樣帶來的兩個新的問題就是:1,我們能否在采樣的短暫時間內將這個電容完全充滿;2,這個電容在采樣瞬間是否會把我們信號瞬態拉低。(具體的SAR ADC驅動設計請參考SLAA571A:Design Challenges and Improvement Techniques for SAR ADC Driver Circuit)。糟糕的驅動設計會導致無論是輸入信號,還是基準信號都會被瞬態拉低,并且造成采樣誤差,如下圖所示:

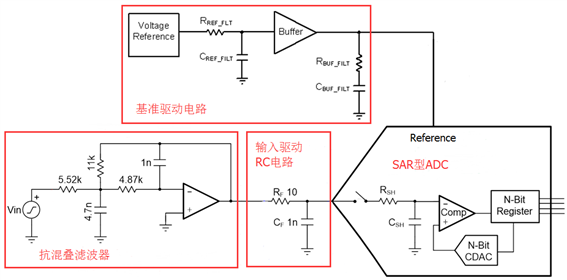

所以標準的SAR型ADC驅動電路需要基準及驅動電路,抗混疊濾波器,輸入驅動電路等三個部分,其電路結構如下:

除了上述的兩個關鍵問題以外,SAR型ADC采樣電路往往還需要配備電壓基準,模擬開關,輸入放大及直流偏置電路(交流信號無法直接被單電源ADC采樣)等,復雜的系統設計往往會另工程師們望而卻步。

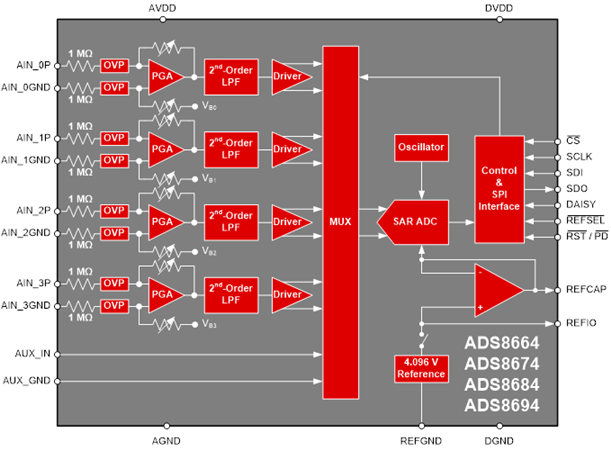

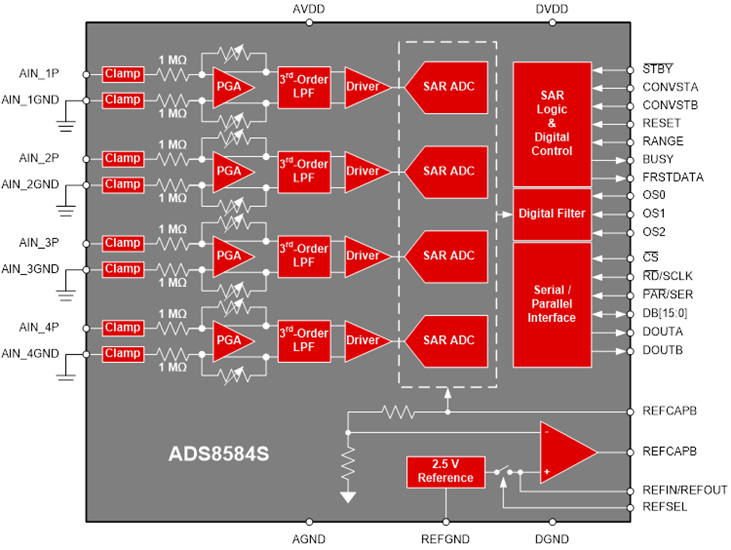

針對于這一問題,現TI開發出一系列全集成式SAR型ADC, 其集成了高阻抗輸入可編程放大器,抗混疊濾波器,ADC驅動電路,模擬開關以及高精密電壓基準等,并且能在單電源供電環境下提供±10V/ ±5V/ ±2.5V等可編程輸入范圍。高集成度的設計使得這種ADC更像一塊電壓采集器,大大簡化采樣電路的設計,同時TI提供極具競爭力的價格,以便眾多工業客戶選用。其結構框圖如下:

非同步型全集成ADC

同步型全集成ADC

這種全集成型的ADC大大簡化了電路設計,同時優化了成本。針對于這一類全集成型ADC,TI提供多種型號,涵蓋不同分辨率,不同通道,同步/非同步等多種器件。下面表格中羅列了全系列高集成度SAR型ADC,以及相應的資料及參考設計TI-Design,歡迎各位工程師點擊查看。

審核編輯:郭婷

-

CMOS

+關注

關注

58文章

5680瀏覽量

235136 -

濾波器

+關注

關注

160文章

7727瀏覽量

177670 -

SAR

+關注

關注

3文章

412瀏覽量

45893 -

adc

+關注

關注

98文章

6430瀏覽量

544077 -

模數轉換器

+關注

關注

26文章

3129瀏覽量

126740

發布評論請先 登錄

相關推薦

貿澤電子開售Analog AD7386逐次逼近寄存器模數轉換器

14位逐次逼近型模數轉換器ADCMAX1033資料推薦

高性能全集成逐次逼近寄存器型模數轉換器介紹

逐次逼近寄存器型模數轉換器輸入的注意事項

簡述高性能全集成逐次逼近寄存器型模數轉換器

模數轉換器:并行比較型和逐次逼近型

逼近型模數轉換器特點和應用

ADS9120逐次逼近寄存器(SAR)模數轉換器(ADC)數據表

ADS9110逐次逼近寄存器(SAR)模數轉換器(ADC)數據表

高性能全集成逐次逼近寄存器型模數轉換器

高性能全集成逐次逼近寄存器型模數轉換器

評論