今天主要給大家簡單介紹一下:PCB 上晶體振蕩電路的設計。

在大部分電路中,設計晶體振蕩電路是經(jīng)常會遇到的。 網(wǎng)絡上也有很多關于晶體振蕩器設計的筆記,不過都是針對大規(guī)模生產(chǎn),這種方法也需要投入大量的測試和不斷地進行優(yōu)化。

這篇文章更加適合小型的電路項目,可以幫助你設計晶體振蕩器和選擇合適的負載電容。

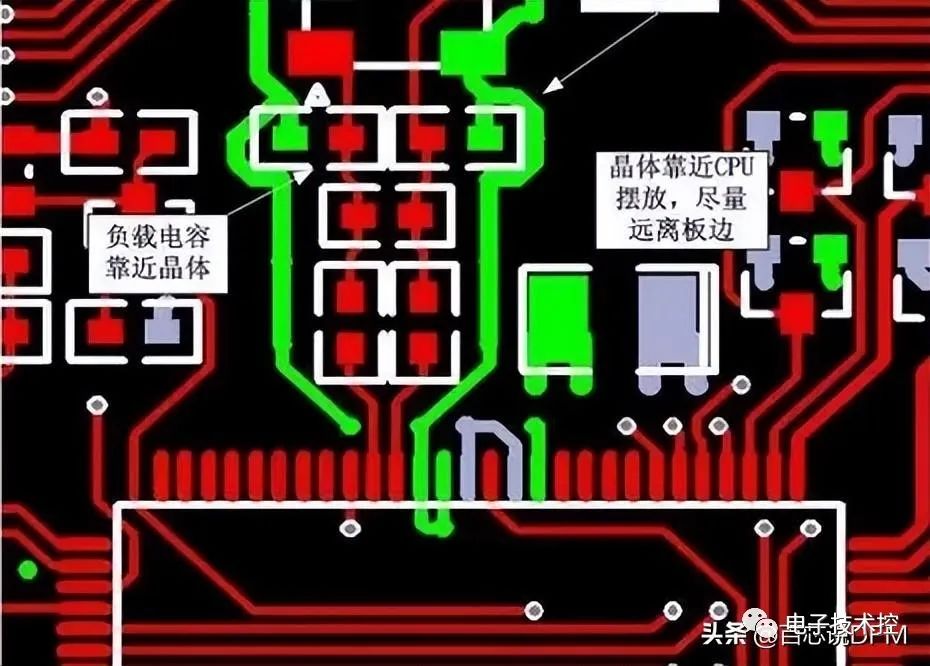

PCB 圖

一、PCB上 晶體振蕩電路設計步驟

這里主要有 4個簡單的步驟:

1、選擇晶體振蕩器

選擇晶體振蕩器需要考慮到以下3 個因素:

可拉性與功耗

振蕩器對頻率變化的功耗啟動時間與封裝尺寸

上電后達到穩(wěn)定振蕩所需要的時間成本

1) 可拉性與功耗

一般來說,拉力低的晶體振蕩器需要較大的負載。 每個振蕩周期都必須要釋放電容的能力,因此更大的負載電容意味著更高的功耗損耗。

很多微控制器的 datasheet 中都會有推薦負載電容的最大值,這樣的話可以減低驅動電路中的功耗。

2) 振蕩器對頻率變化的功耗啟動時間與封裝尺寸

較小的晶體振蕩器封裝具有較大的 ESR ,較大的 ESR 會提供較大的臨界增益(gm_crit),從而降低增益寬=裕度。

增益裕度降低意味著晶體需要更長的時間才能啟動。

3) 上電后達到穩(wěn)定振蕩所需要的時間成本

其實很多時候性能和成本并不是強關聯(lián),如果在滿足性能下,可以選擇成本相對較低的晶體振蕩器。

2、檢查微控制器是否可以驅動晶體振蕩器

通常來微控制器的 datasheet 中會提供一些關于怎么選擇晶體振蕩器。 這些參數(shù)與臨界增益由關,臨界增益是微控制器電路啟動晶體振蕩器所需的最小增益。

有的 datasheet 還會提供一組給定頻率和負載電容的晶體振蕩器允許的最大的 ESR。

如果微控制器數(shù)據(jù)表提供 振蕩器跨導 (通常以uA/V為單位)或最大臨界增益,那么我們需要計算晶體的臨界增益并檢查微控制器是否可以驅動它。

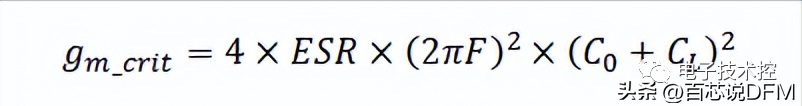

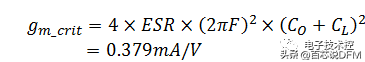

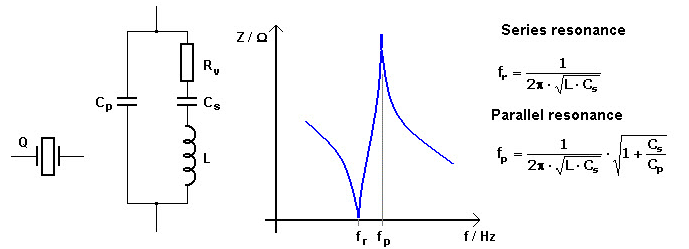

下面為臨界增益計算公式:

臨界增益公式

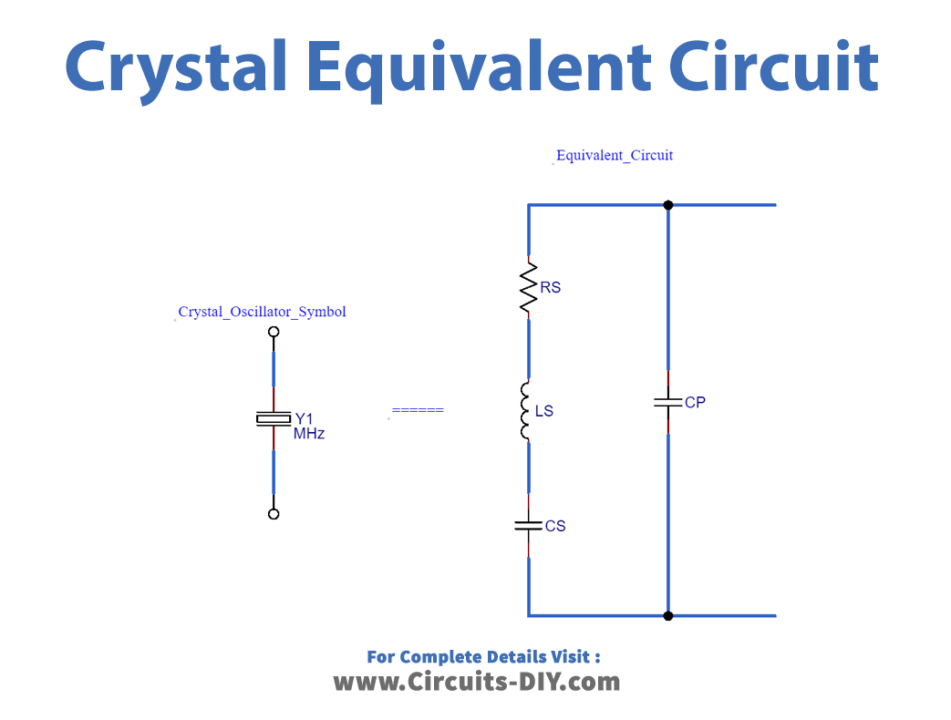

在這個公式中:

F 是晶體振蕩器的標稱頻率

ESR 是晶體的等效串聯(lián)電阻

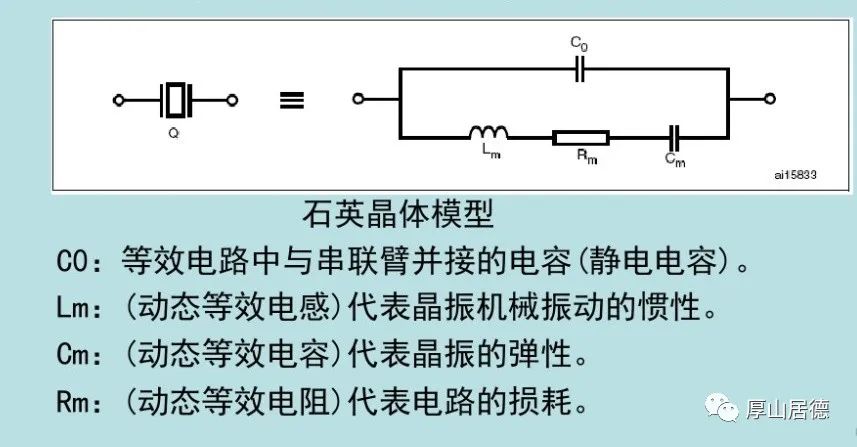

CO 是晶振并聯(lián)電容

CL 是晶體的標稱負載電容

臨界增益是晶體的一個屬性,這些參數(shù)在晶體的數(shù)據(jù)手冊中。

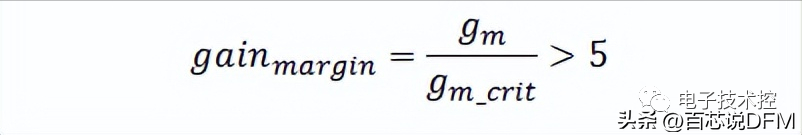

接下來計算增益裕度。 如果增益余量大于5,則振蕩器將可靠啟動。 更大的增益余量意味著更快的振蕩器啟動。

晶體振蕩器的啟動條件:增益余量大于5,如下公式所示:

晶體振蕩器的啟動條件

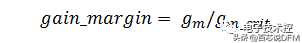

下面為增益裕度計算公式:

增益裕度

或者,一些微控制器數(shù)據(jù)表提供了最大臨界增益gm_crit_max。 在這種情況下,gm_crit必須小于gm_crit_max。

如果微控制器不滿足驅動晶振的要求,就需要重新選擇晶體振蕩器。

3、晶體振蕩器的功耗

datasheet 中會指定了晶體的驅動電平 (DL),驅動電平基本上是晶振正常工作時的最大額定功率。

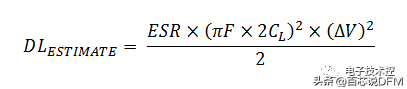

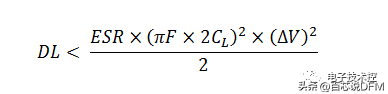

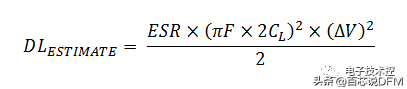

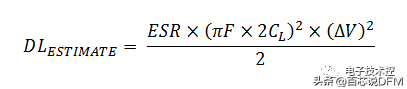

驅動電平的粗略估計可以用下面這個公式計算:

驅動電平驅動電平計算公式

在上面這個公式中:

△V 是 峰峰值振蕩器電壓 ——最壞的情況:△V=Vcc

如果估計值低于晶體振蕩器的額定驅動電平,則直接進行下一步。

符合要求的驅動電平

如果估計值高于晶體振蕩器的額定驅動電平,你可以改進估計值或者重新另外的晶體振蕩器。

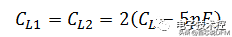

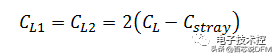

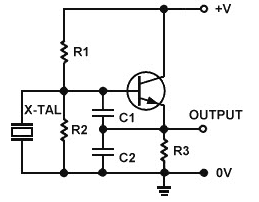

4、選擇負載電容 CL1和 CL2

第一次設計晶體振蕩電路的時候,先假設兩個負責電容是并聯(lián)的。 選擇了CL1=CL2=0.5*CL,但經(jīng)過驗證過后,這是錯誤的。

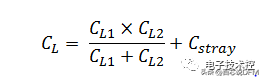

負載電容是晶體兩端所需的電容,因此 CL1 和CL2 串聯(lián)。 負載電容的計算公式如下所示:

負載電容的計算公式

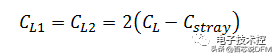

將負載電容的計算公式簡化一下,簡化后的公式如下所示:

簡化后的負載電容計算公式

Cstray 是來自微控制器引腳和走線電容的雜散電容的累積,很多有經(jīng)驗的工程師建議,將這個值估計為 5pF 左右。

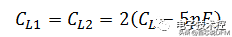

則公式為以下:

負載電容公式

一些微控制器數(shù)據(jù)手冊提供了更準確數(shù)據(jù)一一例如,msp430f22x2系列指定了 1pF 的雜散電容,非常適合其低功耗模型。

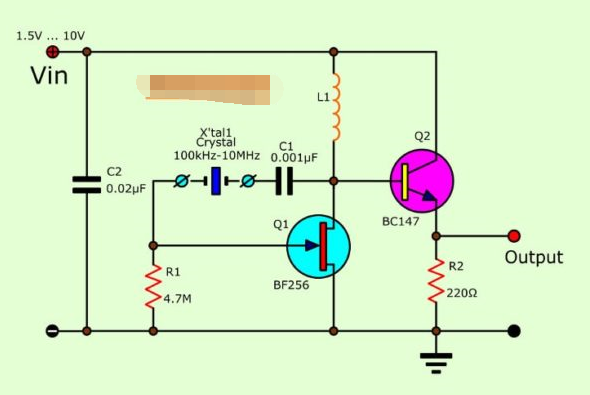

二、PCB 中晶體振蕩電路設計

這里希望通過 PCB 布局來最小化振蕩器和外部信號之間的耦合,因為高頻耦合會激發(fā)晶體振蕩器的高次諧波,晶振是干擾外部電路的噪聲源。

具體有以下幾點需要注意:

1、晶體振蕩器靠近微控制器

短走線具有低互感和電容,長走線具有高互感和電容。 使晶體靠近微控制器可以縮短走線,從而減少耦合。 所以 走線的長度盡可能短,但不能與其他信號線交叉 。

2、振蕩器電路與高頻電路隔離開

路由非振蕩器信號時, 高頻電路要遠離振蕩器電路 。 也可以考慮使用帶有通孔的銅跡線,圍繞著振蕩器電路,這將減少外部信號線和振蕩器之間的互感。

振蕩器電路與高頻電路隔離開

通常的做法是 將振蕩器電路下方的接地層分開,僅在一點點連接分離的接地層,就在微控制器接地旁邊。 這可以防止來自其他信號源的返回電流通過振蕩器使用的接地層。 上圖的示例就是按照這種方法,只是沒有很明顯。

因為內部石英晶體的存在,由于外部沖擊或跌落容易損壞石英晶體,從而造成晶體不振蕩,在設計可靠的安裝電路時要考慮晶體,靠近 CPU 芯片的位置優(yōu)先放置遠離板塊的一面。

晶振放置圖

(圓柱晶振)外殼接地后,加一個與晶振形狀相似的長方形焊盤,讓晶振“平放”在這個焊盤上,并在焊盤的兩個長邊附近開一個孔(孔要落在焊盤上,最好用多層焊盤代替孔,兩個多層焊盤要接矩形焊盤),然后用銅線或其他裸線將晶振“箍”起來,銅線的兩端焊接在你開的兩個孔或焊盤上。 這樣可以避免高溫焊接對晶振的損壞,保證良好的接地。

4、手工或機器焊接時,要注意焊接溫度

晶振對溫度敏感,焊接時溫度不宜過高,加熱時間盡量短。

5、耦合電容應盡量靠近晶振的電源管腳放置

放置順序: 根據(jù)功率流向,按電容值從小到大排列 ,電容最小的電容值最接近電源引腳。

6、晶振外殼接地

晶振外殼接地(如果接地影響負載電容的話,就不能接地) ,既可以從晶振向外輻射,也可以屏蔽外界信號對晶振的干擾。

7、不要在晶振下方布線,確保完全鋪設好地線

在晶振 300mil 范圍內不要布線 ,以免晶振干擾其他布線、器件和層的性能。

8、時鐘信號的走線盡量短,線寬要大一些

時鐘信號的走線盡量短,線寬要大一些 。 在布線長度與熱源的距離之間找到平衡點。

三、示例1∶為 STM32 設計 8MHZ 晶體振蕩器

1、選擇晶振

STM32F427 數(shù)據(jù)手冊中要求:

對于 4-26MHz 晶體,Gm_crit_max=1mA/V

頻率容差必須為 +/-500ppm 或更好

CL1 和 CL2 建議在 5pF 到 25pF 之間

這里我們選擇 7A-8.000MAAJ-T,雖然 STM32 的引腳間距為0.5mm,但晶振的尺寸小,可以放置在靠近在 STM32的位置。

7A-8.000MAAJ-T 晶振的特性:

CL= 18 pF

紅電燈= 60 Ω

頻率穩(wěn)定性= 50 ppm

頻率容差= 30 ppm

CO= 7pF最大值

驅動電平(DL)= 500uW max

2、檢查微控制器是否可以驅動晶振,計算 gm_crit(增益裕度)∶

gm_crit計算公式

所以gm_crit低于Gm_critmax,振蕩器電路將可靠啟動。

3、晶振可以處理功率損耗嗎?

這里粗略估計電路的驅動電平∶

驅動電平計算公式

計算得 DL =267uW,低于晶體允許的最大驅動電平500uW。

4、選擇 負載電容 CL1 和 CL2

假設 Cstray=5pF,則∶

負載電容公式

CL1=26pF

STM32 建議將 CL1和CL2保持在 25pF 以下,所以可以選 24 pF 的電容。

四、示例2∶為 ATMEGA328 選擇 16MHZ 晶體振蕩器

1、選擇晶振

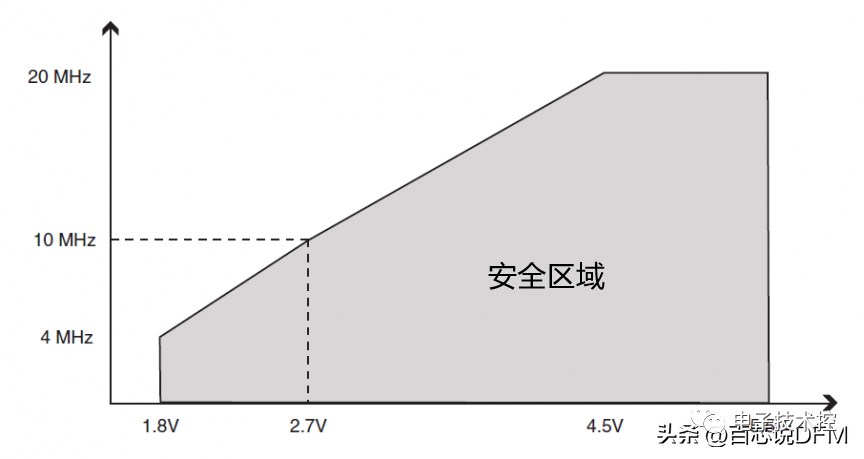

ATMega328 數(shù)據(jù)手冊的要求:

16MHz 的最小電壓為 3.78V,以適應安全操作,如圖下所示。 要驅動 16MHz 時鐘,我們必須在 3.78V 或以上,對于本設計,我們在 5V 下工作。

CL1 和 CL2 建議在 12pF 到 22pF 之間

ATMega328 數(shù)據(jù)手冊

這里選擇 9B-16.000MAAE-B 晶振。 9B-16.000MAAE-B 晶振 的特性參數(shù)如下所示:

CL= 12pF

紅氧化 = 30Ω

頻率穩(wěn)定性= 30ppm

頻率容差= 30ppm

C0= 7pF最大值

驅動電平( DL)=500uWmax

2、檢查微控制器是否可以驅動晶振

ATMega328 的數(shù)據(jù)表中 沒有跨導規(guī)范,這里就必須讓開發(fā)人員設置好保險絲 ,以便在填充 PCB 后啟用振蕩器。

3、晶振可以處理功率損耗嗎?

粗略估計電路的驅動電平(DL)∶

驅動電平計算

驅動電平( DL )=545uW。

驅動電平估計值太高。 但是,如果選擇 CL1并且表明設計的功耗是可以承受的,就可以改進這個估計值。

4、選擇 負載電容 CL1 和 CL2

假設Cstray=5pF,則∶

負載電容 計算

CL1= 14PF。

-

pcb

+關注

關注

4292文章

22768瀏覽量

393174 -

電路設計

+關注

關注

6636文章

2398瀏覽量

201098 -

晶體

+關注

關注

2文章

1320瀏覽量

35127 -

振蕩電路

+關注

關注

17文章

499瀏覽量

98546 -

晶體振蕩器

+關注

關注

9文章

603瀏覽量

28826 -

晶體振蕩電路

+關注

關注

0文章

29瀏覽量

6180

原文標題:四、示例2∶為 ATMEGA328 選擇 16MHZ 晶體振蕩器

文章出處:【微信號:電子技術控,微信公眾號:電子技術控】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

振蕩電路評估方法(2)為評估振蕩電路而進行的工作(振蕩裕度與激勵功率篇)

振蕩電路評價方法(1)為評估振蕩電路而進行的工作(頻率匹配篇)

低頻振蕩電路新常識

為評估振蕩電路而進行的工作振蕩裕度與激勵功率篇(振蕩電路評估方法2)

為評估振蕩電路而進行的工作頻率匹配篇(振蕩電路評價方法1)

在PIC單片機振蕩電路中如何選擇晶體?

什么是晶體振蕩器老化?老化的原因 如何測量晶體振蕩器的老化?

晶體振蕩器與LC振蕩器的區(qū)別

晶振振蕩電路的設計方法和步驟

PCB上晶體振蕩電路的設計

PCB上晶體振蕩電路的設計

評論