0****1

二進制加法器

01

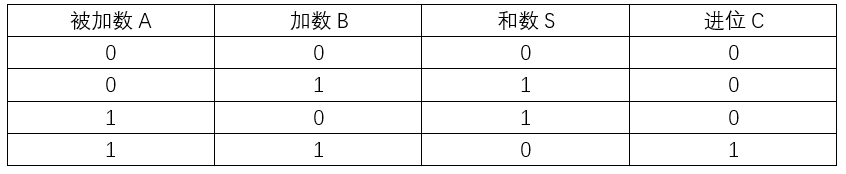

半加器

半加器不考慮低位進位來的進位值,只有兩個輸入,兩個輸出。由一個與門和異或門構成,

真值表如下:

邏輯表達式 :

02

全加器

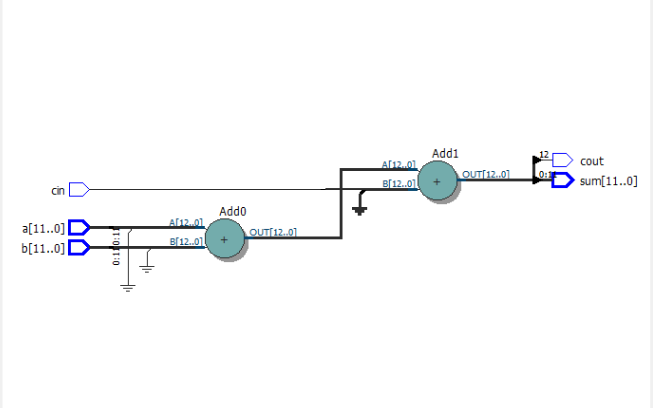

當多位數相加時,半加器可用于最低位求和,并給出進位數。第二位的相加有兩個待加數和,還有一個來自前面低位送來的進位數。這三個數相加,得出本位和數(全加和數)和進位數。這種就是“全加"。

**真值表如下: **

| 被加數A | 加數B | 進位輸入Ci | 和數S | 進位輸出Co |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

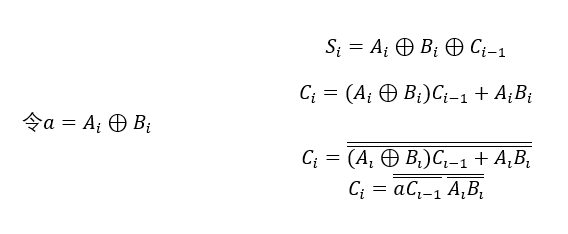

邏輯表達式 :

經過上面的介紹我相信大家對加法器已經有了一定了解,接下來我們為大家介紹如何用與非門等設計一個全加法器。首先我們需要對 公式化簡 ,這里就用到了前面介紹的邏輯轉換律。

02

減法器

減法器可以由基礎的半減器和全減器模塊組成,或者基于加法器和控制信號搭建。

定義Nbit被減數x,減數Y,差為D(difference);來自低bit的借位Bi,想高bit借位Bi+1,i為bit序號。

01

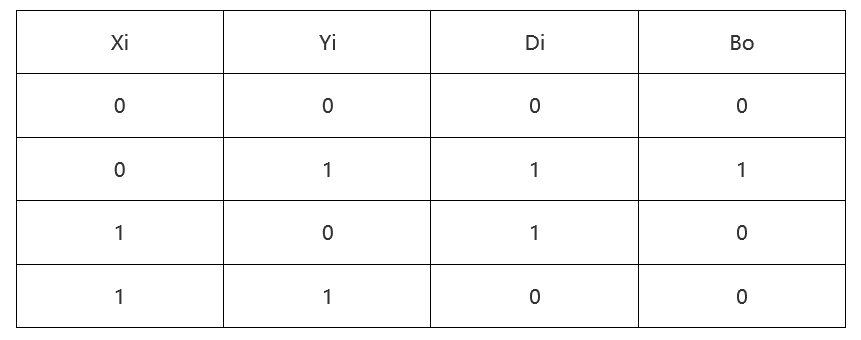

半減器

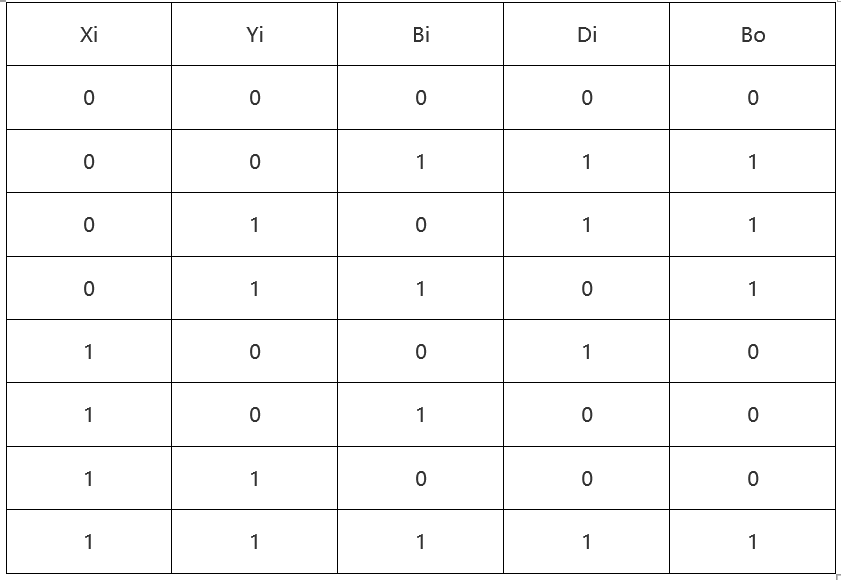

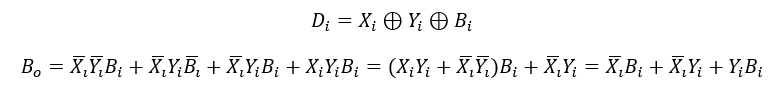

半減器用于計算兩bit Xi和Yi的減法,輸出結果Di和向高位的借位Bo(Borrow output)。其真值表、邏輯表達式如下:

02

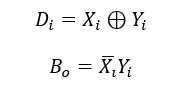

全減法器

全減器不同于半減器在于,全減器輸入來自低位的借位Bi(Borrow input),另外兩個輸入xi、yi,輸出為Di和向高位借位Bo。

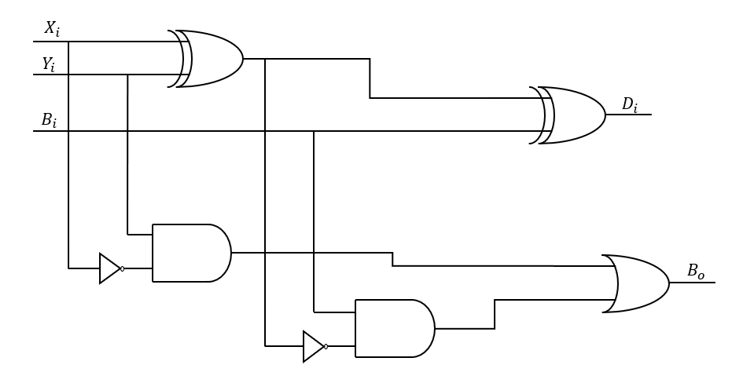

其真值表、邏輯表達式如下:

接下來我們為大家介紹如何用與非門等設計一個全減法器:

03

乘法器(陣列乘法器)

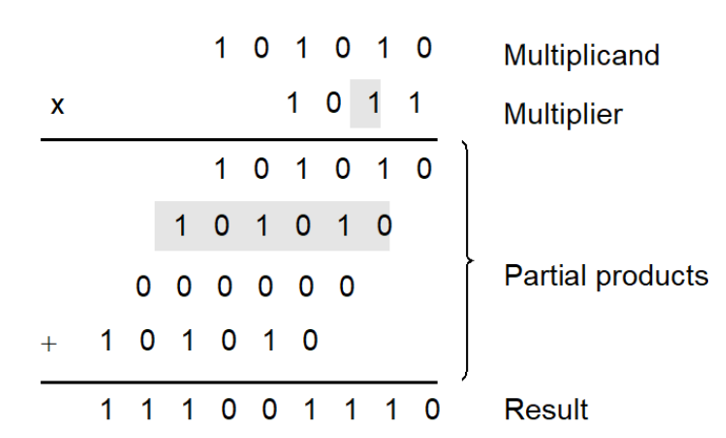

實現乘法的比較常用的方法是類似與手工計算乘法的方式:

對應的硬件結構就是陣列乘法器(array multiplier)它有三個功能: 產生部分積,累加部分積和最終相加 ,其中HA為半加器,FA為全加器。

-

數字電路

+關注

關注

193文章

1600瀏覽量

80506 -

半加器

+關注

關注

1文章

29瀏覽量

8783 -

與門

+關注

關注

0文章

19瀏覽量

3502

發布評論請先 登錄

相關推薦

本的二進制加法/減法器,本的二進制加法/減法器原理

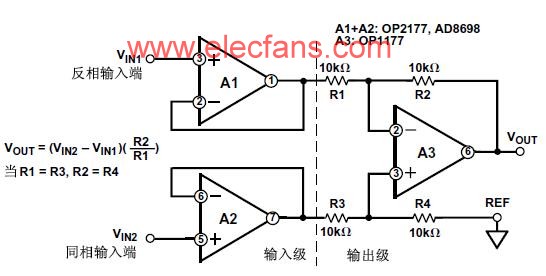

加法器與減法器_反相加法器與同相加法器

數字電路基礎知識之加法器、減法器

數字電路基礎知識之加法器、減法器

評論