摘要

本文以高速系統的信號/電源完整性分析和EMC分析的為基本出發點,著重介紹了高速PCB的信號和電源完整性分析的基本要領和設計準則,通過EDA分析工具實現PCB的建模與參數提取;通過電磁場分析工具完成網絡參數定量分析,從最基本的設計方法入手,提出了高速PCB的信號/電源系統設計參數優化方案,指出了信號/電源完整性仿真設計和EMC設計的內在聯系,最后介紹了利用EDA仿真工具和EMC測試驗證相結合解決單板PCB設計的EMI問題的成功范例,希望本文總結的經驗能給予正在從事高速系統仿真的設計開發人員和EDA設計人員解決此類問題的基本思路與方法。

引言

當今的高速PCB設計領域,由于芯片的高集成度使PCB的布局布線密度變大,同時信號的工作頻率不斷提高,信號邊沿(Tr)的不斷變陡,由此而引發的信號完整性和電源完整性問題給EDA設計人員和硬件開發人員帶來前所未有的挑戰,信號/電源完整性問題處理不當同時會帶來一系列的EMC問題,給產品的可靠性造成危害。目前,基于Cadence公司SQ的板級與系統級互連仿真已經在廣泛應用,在硬件設計流程中引入了SI/PI/EMI的仿真分析環節。信號完整性與電源完整性分析做的較成功的PCB,電磁兼容性(EMC)也明顯改善。

信號/電源完整性分析通過對PCB的信號互連與電源分配系統(PDS)分析,使用EDA與電磁場分析軟件找出PCB的噪聲點并加以抑制,通過PCB的優化設計改善層間噪聲與電源層和地線層之間的阻抗。降低信號的反射和串擾;改進信號的回流路徑,降低電源分配系統阻抗,同步開關噪聲,消除PCB上關鍵點和關鍵頻率的諧振,合理放置去耦電容改善電源地的阻抗與諧振,使用屏蔽過孔等措施減小PCB的邊緣輻射。

隨著信號的Tr變快,產品的EMC問題成為EDA設計的最大難點。EMC問題由來已久,涉及面較廣,隨著信號速率的提高和芯片尺寸的減少,傳統的EMI設計方法顯得力不從心。解決EMC問題和解決其它SI問題顯著的不同點在于EMC更依賴于測試,或者是仿真與測試過程兩者的融合,不同類型的EMI包括來自于信號互連的連接器,電纜,PCB的連線以及邊緣輻射等。

電源和信號完整性對EMI的性能有著直接的影響,從PCB設計階段控制EMI,能起到事半功倍的作用。我們通常采用下列幾種方法來分析并改進信號和電源完整性,從而減小EMI輻射。

1. 減少電源地平面間噪聲-電源完整性分析

2. 優化電源地系統阻抗-電源完整性分析

3. 降低串擾和反射-信號完整性分析

4. 改善同步開關噪聲-信號完整性分析

5. 減少邊緣輻射-信號完整性/電源完整性分析

一、 關于電源完整性仿真的電容建模

1、非理想旁路電容的定義:

在電源系統的設計中,我們經常用到以下的三類電容:

1)旁路電容:主要作用是給交流信號提供低阻抗的回流路徑;

2)去耦電容:增加電源和地的交流耦合,減少交流信號對電源的影響;

3)濾波電容:用于電源濾波電路中,消除電源紋波;

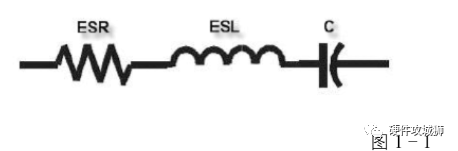

在電源完整性仿真中,我們主要研究對象是非理想化的旁路電容。對于理想的電容來說,不考慮寄生電感和等效串聯電阻的影響,那么我們在電容設計上就沒有任何顧慮,電容的值越大越好。但實際情況卻與理論分析相差很遠,并不是電容越大對高速電路越有利,反而在高頻段往往采用小電容,電容的材料和制造工藝也有要求。要理解這個問題,我們首先必須了解實際電容器本身的特性,在頻率很高時,電容不再被當作理想的電容看待。電容的寄生參數的影響不能忽略。考慮到電容具有一定的物理尺寸,以及起連接作用的安裝焊盤和過孔,其寄生參數包括一個串聯電感和串聯電阻,由此得到如圖1-1的電容模型。

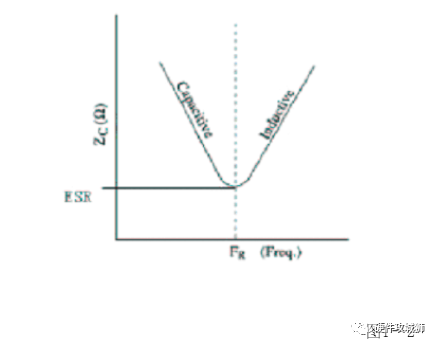

對電容的高頻特性影響最大的則是ESR和ESL,我們通常采用圖1-1中簡化的電容模型。電容也可以看成是一個串聯的諧振電路,當它在低頻的情況(諧振頻率以下),表現為電容性的器件,而當頻率增加(超過諧振頻率)的時候,它漸漸的表現為電感性的器件。也就是說它的阻抗隨著頻率的增加先增大后減小,等效阻抗的最小值發生在串聯諧振頻率處,這時候,電容的容抗和感抗正好抵消,表現為阻抗大小恰好等于寄生串聯電阻ESR,變化曲線如圖1-2所示:

從諧振頻率的公式可以看出,電容大小和ESL值的變化都會影響電容器的諧振頻率。由于電容在諧振點附近的阻抗最低,所以設計時盡量選用FR和實際工作頻率相近的電容。如果工作的頻率變化范圍很大,則可以混合使用不同容值和FR電容,即同時選擇一些FR較小的大電容和FR較大的小電容。

2、PI仿真電容及分布參數的建模:

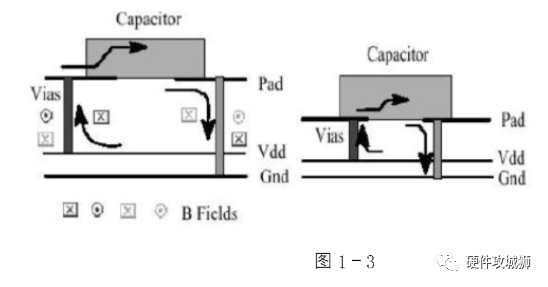

非理想旁路電容由ESR、C、ESL、引線和過孔等幾部分組成,見圖1-3所示。

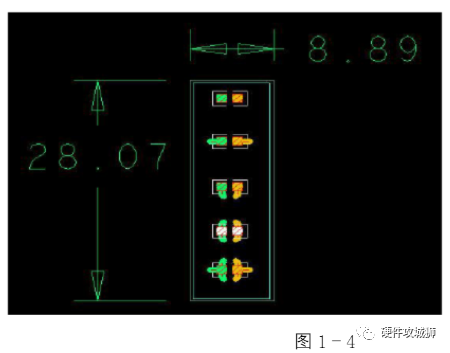

在高速PCB設計中,我們常用的電容引線方式有以下幾種,為定量分析各種引線方式的影響和建模的需要,我們從正在設計中的單板中提取了用于分析的樣板,見圖1-4所示。

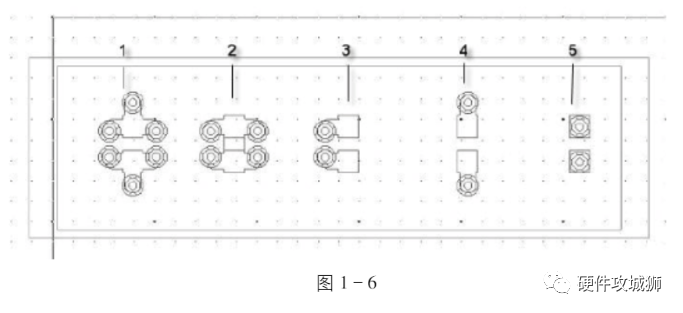

常見的電容的引線方式有以下5種,如圖1-6所示,其中第5種在焊盤上開孔目前工藝不推薦,在此只作分析,首先,我們分別計算了VCC_3.3V到電容管腳的引線和過孔的電感,

得到以下5組數據(單位:亨利):

L001 2.82101E-010

L0022.70197E-010

L0038.36196E-010

L0049.23669E-010

L0053.65286E-010

為了盡量減小引線電感,在設計中我們可以優先采用第2種引線方式,其中第4種引線方式在傳統的PCB設計中廣泛采用,由于這種引線方式會帶來較大的引線電感,建議在高速PCB設計中盡量不要采用。

接下來,我們對電源/地的回路作進一步分析,提取了第二種引線方式的SPICE子電路,得到的結果如下:

VCC3.3V到電容PIN1的子電路為:

.subcktcap_2_via_vcc 1 2 3

C0014 3 1.27114E-010

V0011 5 DC 0

L0015 6 1.39697E-010

R0016 4 0.00663062

V0024 7 DC 0

L0027 8 1.39697E-010

R0028 2 0.00663062

.ENDScap_2_via_vcc

電容PIN2到GND的子電路為:

.subckt cap_2_via_gnd 1 2 3

C0014 3 1.28742E-010

V0011 5 DC 0

L0015 6 2.75467E-010

R0016 4 0.00513052

V0024 7 DC 0

L0027 8 2.75467E-010

R0028 2 0.00513052

.ENDScap_2_via_gnd

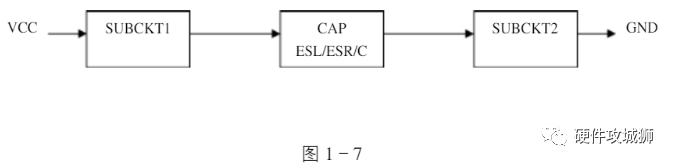

通過以上過程,我們得到了回路所有構件的RLC參數,由此我們可以建立以下電流回路,如圖1-7所示。

VCC3.3V -----子電路1----- pin1----- 電容(C/ESL/ESR)----- pin2 ----- 子電路2 ----- GND

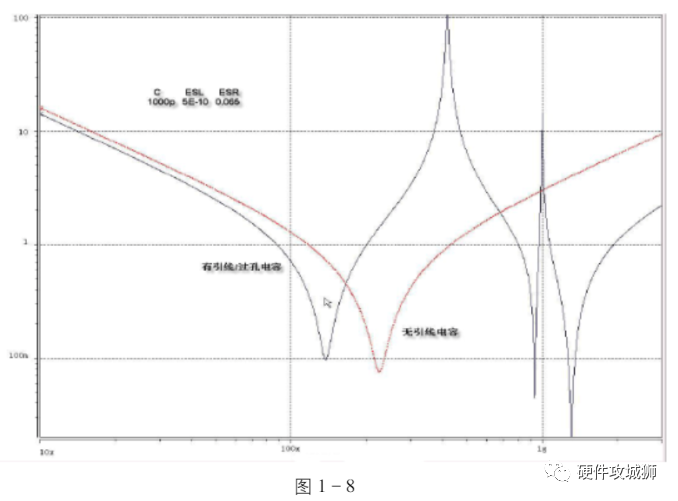

定義各部分子電路的連接關系,我們可以得出電容和引線/過孔對結果的影響,取電容值為:1000pf;ESL=5E-10;ESR=0.065(AVX),得到無引線電容和考慮過孔與引線電容的頻率響應曲線如圖所示,其中紅色曲線為無引線電容的阻抗-頻率曲線,藍色曲線為有引線/過孔的阻抗-頻率曲線,我們可以得出分析結果如圖1-8所示。

1)由于引線及過孔的分布參數存在,電容的諧振點會向低頻率漂移;

2)由于在電源地之間加入了電容、引線及過孔,會帶來新的諧振點,在設計中必須充分加以考慮。

| C | ESL | ESR | |

| X7R | 0.1u | 5E-10 | 0.035 |

| 0.01u | 5E-10 | 0.097 | |

| 4700p | 5E-10 | 0.134 | |

| 3300p | 5E-10 | 0.157 | |

| 2200p | 5E-10 | 0.186 | |

| 1000p | 5E-10 | 0.261 | |

| NPO | 1000p | 5E-10 | 0.065 |

| 470p | 5E-10 | 0.09 | |

| 330p | 5E-10 | 0.1 | |

| 220p | 5E-10 | 0.125 | |

| 100p | 5E-10 | 0.175 | |

| 68p | 5E-10 | 0.206 |

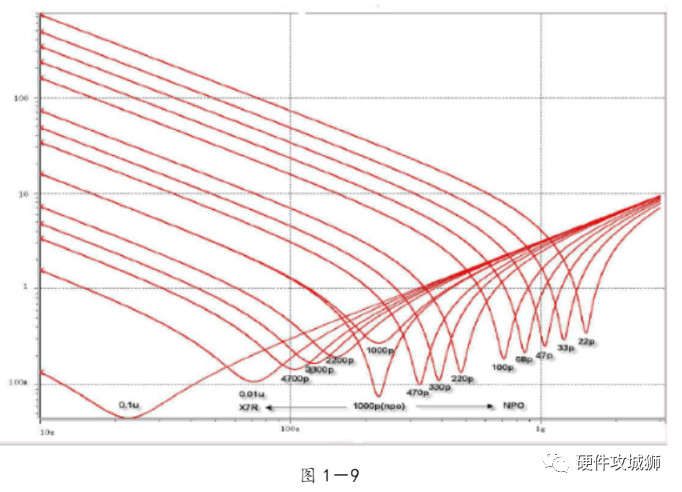

由上表的參數,得到如下的無引線電容的阻抗-頻率曲線,如圖1-9所示。

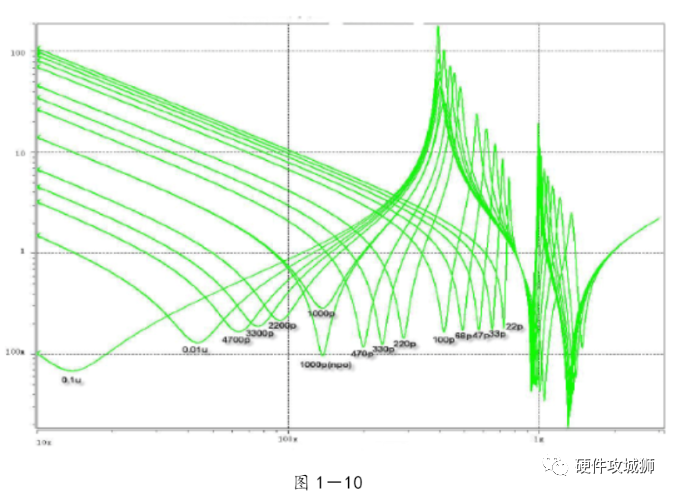

考慮引線與過孔的影響,可以推算出電容加上兩端引線和過孔的阻抗-頻率響應曲線,如圖1-10所示:

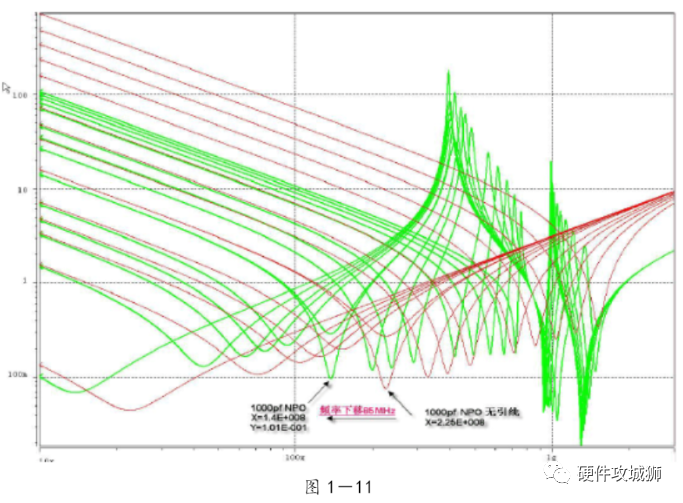

圖1-11反映了有引線/過孔的電容(綠色曲線)和無引線/過孔電容(紅色曲線)的阻抗-頻率特性的比較,可以看出電容的諧振點有向下漂移的趨勢。

4、電源完整性分析軟件對電容分布參數的計算:

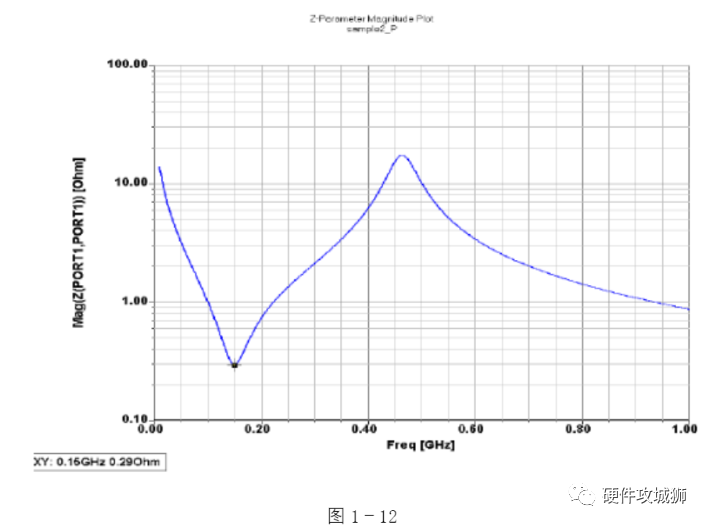

使用SIWAVE也可以分析出電容的引線及過孔的電感對諧振點的影響,將上面的例子轉換成siw文件,加入上述參數的電容(NPO 1000pf),設定PORT,得到如圖1-12的阻抗-頻率曲線。

從圖1-12可以看出:SIWAVE計算阻抗時已經考慮了引線及過孔的影響,1000pf電容的諧振點已經由225MHz向下漂移到150MHz左右。

【仿真電容問題總結】

1)電容的建模問題是PI仿真非常重要的一步,電容廠家很多,參數不一致,影響PI仿真結果的準確性。一般國內的電容廠家的ESL/ESR值很難提供,可以借助于儀器測量得到參數;

2)在PCB上完成電容引線時,應該以最小ESL為原則,如:加粗引線,加大過孔等,盡量減小分布電感對諧振點的影響;

3)可以適當采用電容組合;

4)對高頻段采用小電容要慎重,以防引線/過孔電感造成實際諧振點的向低漂移與產生新的諧振點(反諧振),高頻段應該以改進與優化PCB設計為原則。

電源完整性分析與EMI控制

PCB板上存在有兩個主要輻射源。第一是來自頂層和底層的傳輸線。假設這些線相對應的參考平面是理想的,那么它們的差模輻射是可以根據導線電流計算得到的。對于頂層和底層的傳輸線,尤其是時鐘,應避免1/4波長的走線;第二個源就是邊緣輻射。電磁場從激發區域經過電源地平面間傳播到邊緣,在那里產生輻射。平面上存在的任何過孔、不連續阻抗等,都將轉變為電源/地噪聲和邊緣輻射,因此,邊緣輻射直接和電源/地噪聲和電源完整性相關。一塊具有良好信號完整性的PCB很自然的具有較低的電源/地噪聲和較低的邊緣輻射。

下面結合高速PCB的SI和設計過程和本人在設計中積累的經驗,介紹一些通用的設計規則和值得注意的設計要點:

1、信號的過沖與振鈴:

信號質量是我們首要關注的問題,信號的過沖與振鈴會帶來一系列可靠性問題,在EMI的測試方面,數據/地址等信號線的過沖與振鈴是輻射背景噪聲的主要貢獻者。

解決信號過沖與振鈴問題的主要手段是端接,選用適當的拓撲結構等。

在我們進行高速系統級仿真時,往往常常分析的問題是:當CPU通過總線,接插件,板間級連,PCB走線和多個對象通訊時,在不同對象個數、不同信號傳輸方向的情況下,系統的各個接收端波形會產生很大的差異,采用適當的端接策略可以解決這些SI問題,

下面舉例說明:

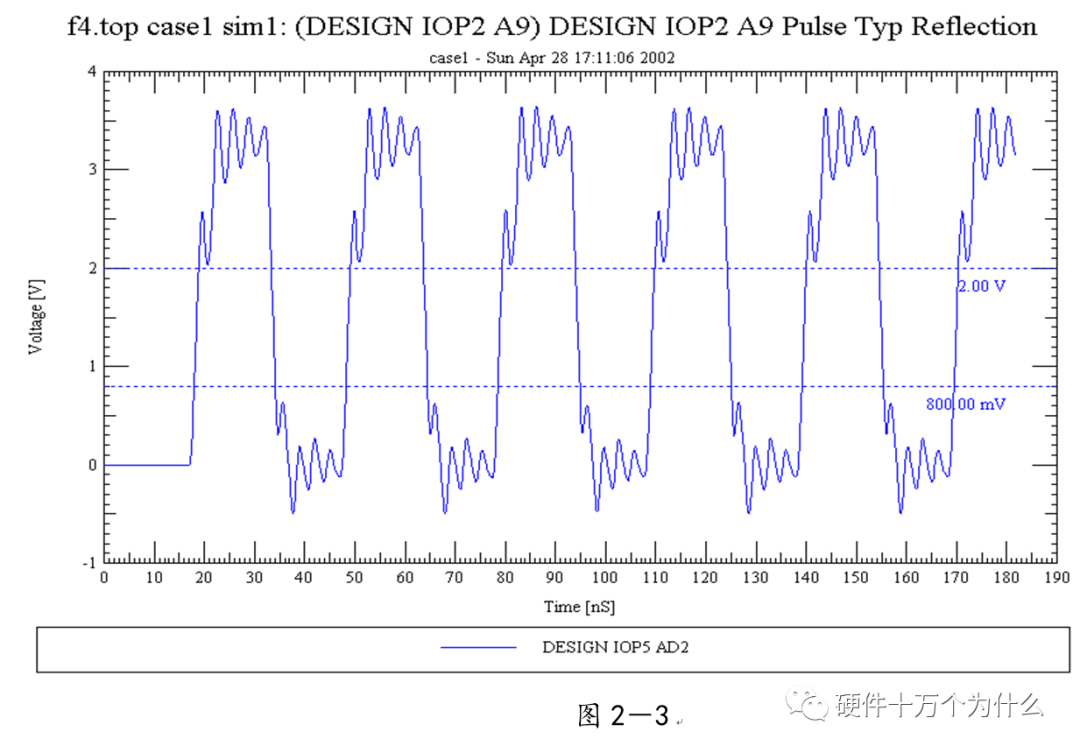

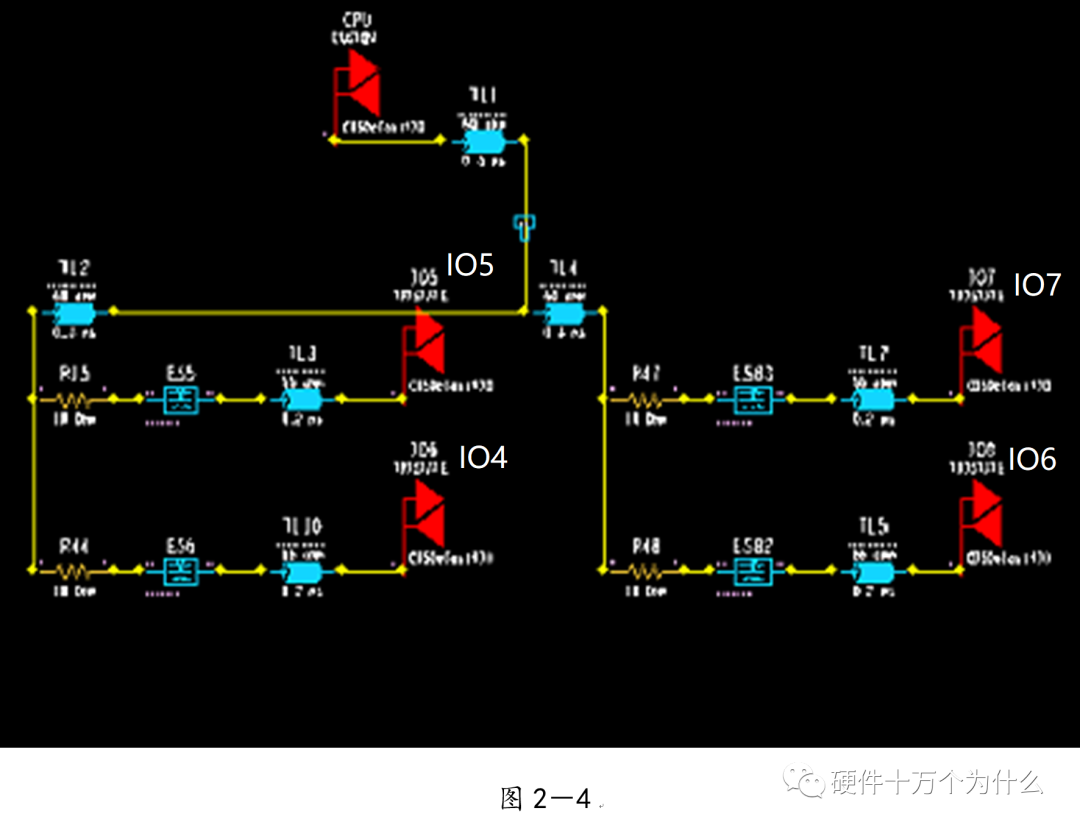

圖2-2是一個典型的CPU通過板級互連的點到多點拓撲結構圖,在源端已經加匹配電阻端接,以下是CPU發送,IOP5接收,在不同負載的條件下,IOP5的接收波形,圖2-3是IOP6不用,其余3個接收端使用的情況下,IOP5的接收波形,可以看出,接收端有明顯的過沖。

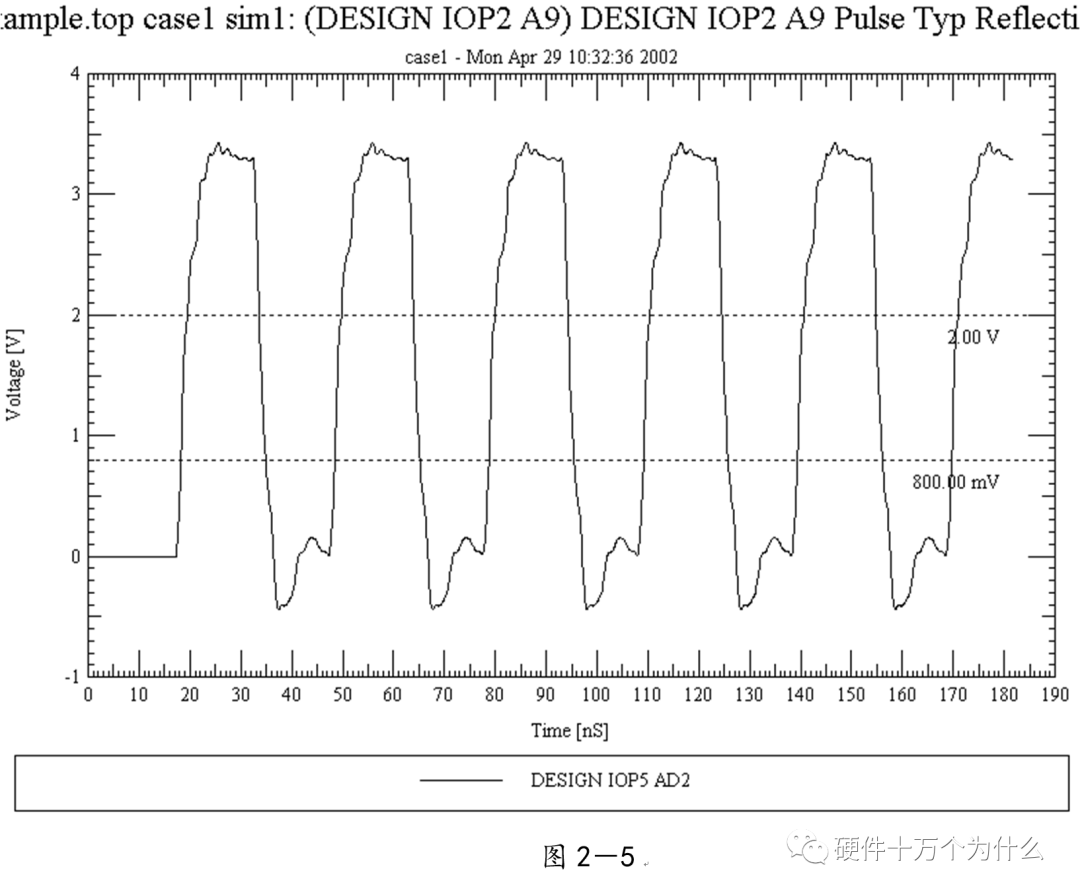

解決的方法有:更改拓撲結構、調整PCB走線的線長,阻抗、更換器件、調整端接方案等。通過改變圖2-2的拓撲結構的端接電阻的位置,得到拓撲結構圖2-4,我們得到當IOP6不用,其余3個接收端使用的情況下,IOP5的接收波形,見圖2-5。

比較圖2-3和圖2-5可以看出,信號的單調性(monotonic),過沖(Overshoot,undershoot)等方面已經得到了明顯的改善,同時,時序的改善也是顯而易見的。

2、時鐘電路的處理

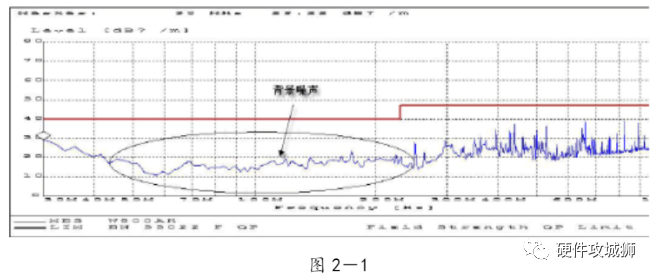

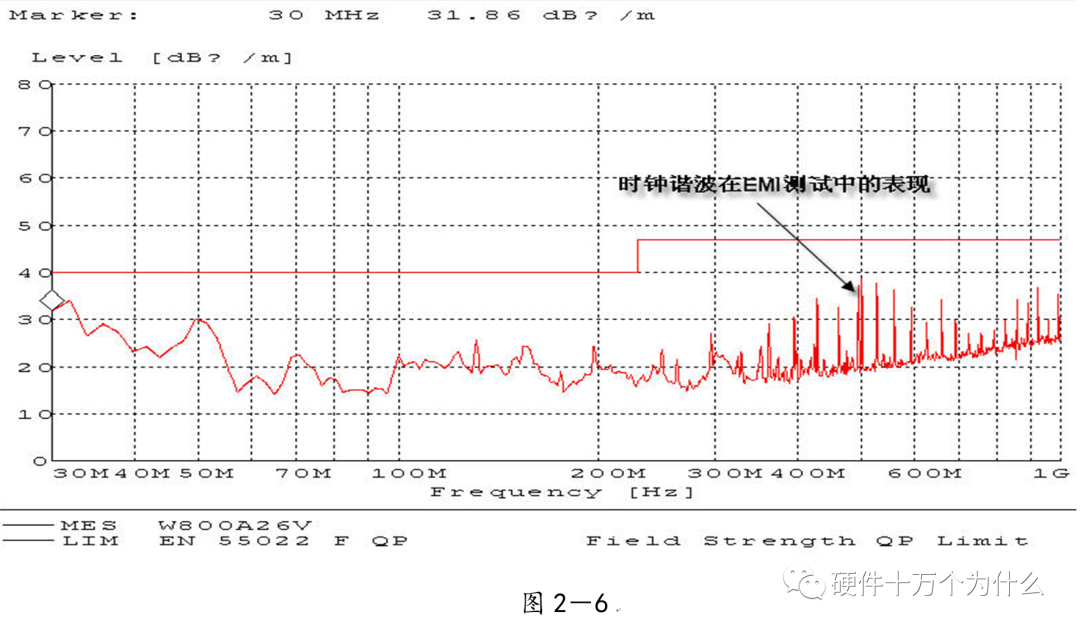

時鐘電路的設計和EMI問題切切相關,高速PCB的時鐘電路的設計必須遵循嚴格的設計原則保證SI和PI的要求,由于時鐘的周期性,在遠場表現為離散的頻譜,EMI超標的部分往往是時鐘或時鐘的諧波,時鐘對遠場EMI的貢獻如圖2-6所示。

在高速PCB的時鐘電路的設計中,建議遵循以下幾個設計原則:

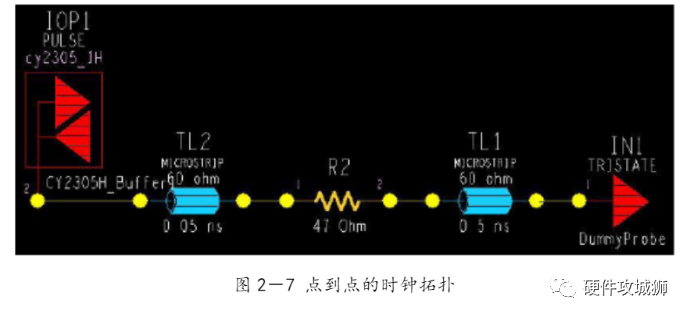

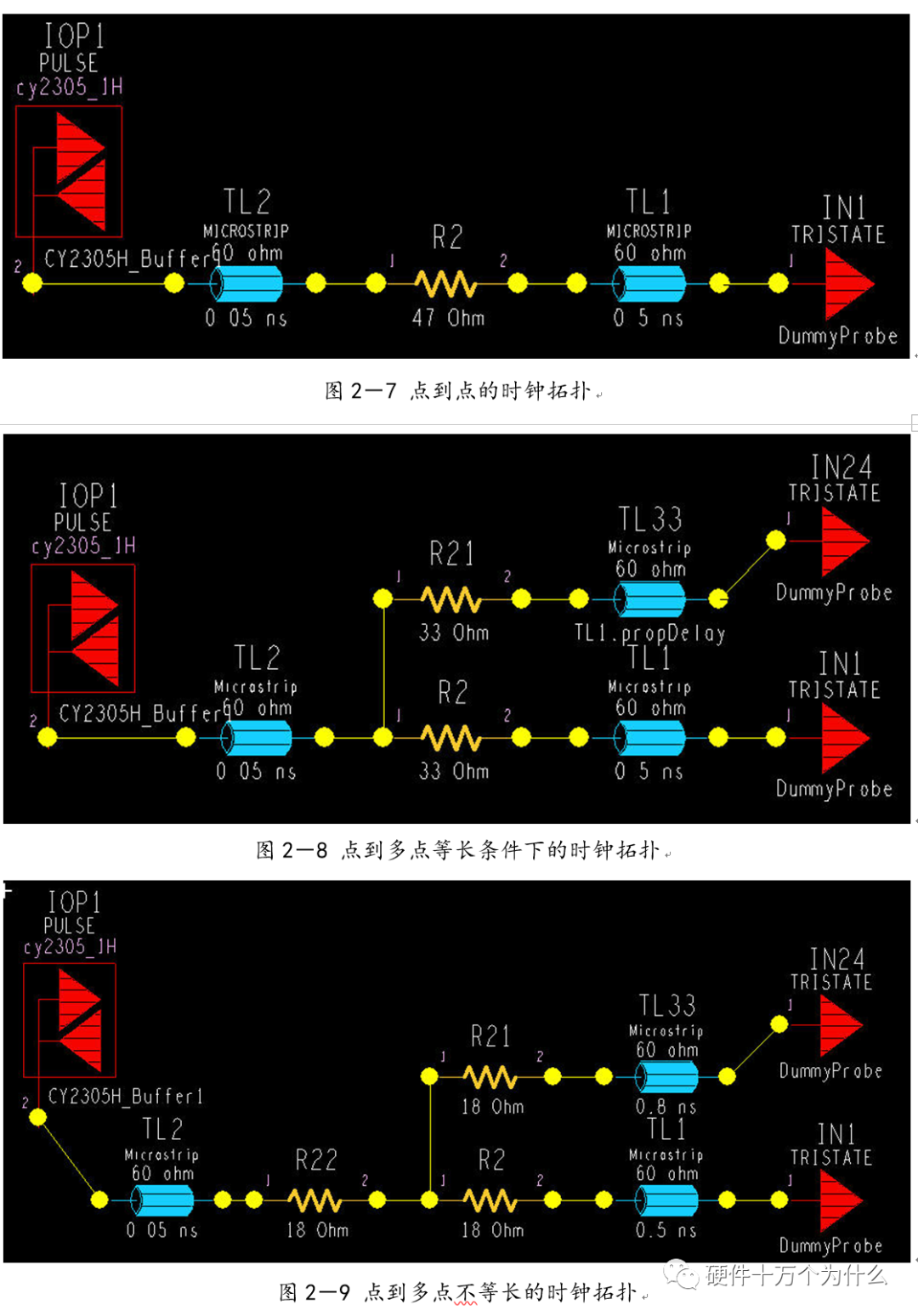

◎在點到點或點到多點的時鐘電路設計中要做嚴格的SI分析確保時鐘最小的過沖與最大噪聲余量,時鐘電路一般采用源端匹配和終端上下拉的方式匹配,如圖2-7、圖2-8、圖2-9,串阻值可以在SQ中用掃描的方法獲得,在保證時序空間有較大余量的前提下,可以調整串阻值將延適當變緩以減小EMI。

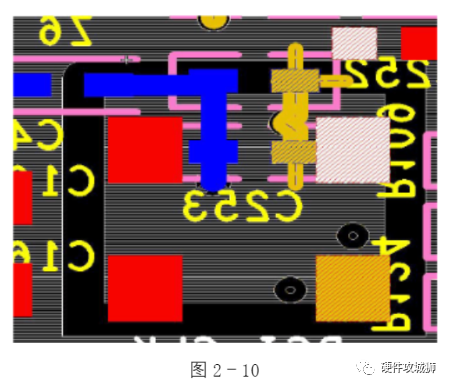

◎晶振的電源單獨供電,通過磁珠加電容濾波電路,將時鐘供電電源與VCC在PCB上隔開,如圖2-10,供電電源由VCC經過磁珠Z6和電容C252(0.01u)和C253(1000pf)組成獨立的電源濾波電路,同樣的設計方法可以用于帶PLL時鐘分配器等電路。

◎時鐘線應盡量走線在內層并少打過孔,保證時鐘與回流路徑的最小面積。

3、合理的疊層設計

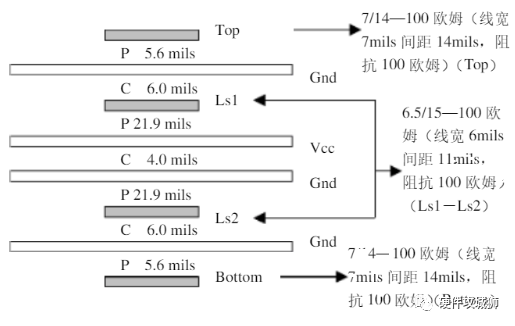

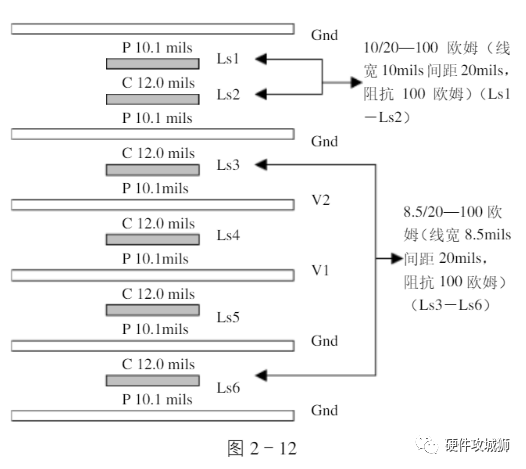

高速PCB的疊層設計在保證電源/地阻抗及EMI控制方面有較大影響,多層板的疊層設計在SI方面的設計指南中重點提及,可以參閱其它SI設計文檔,這里舉一例說明,如圖2-11是一個常用的8層板疊層設計,圖2-12是12層背板疊層設計圖:

為保證電源完整性的要求,減小高速PCB的EMI,疊層設計一般遵循以下幾個設計原則:

◎電源和地平面采用緊耦合,及電源平面緊貼地平面;

◎在線寬可以滿足的條件下,信號線盡量與參考平面(一般是地)緊耦合;

◎盡量以地平面為參考平面。

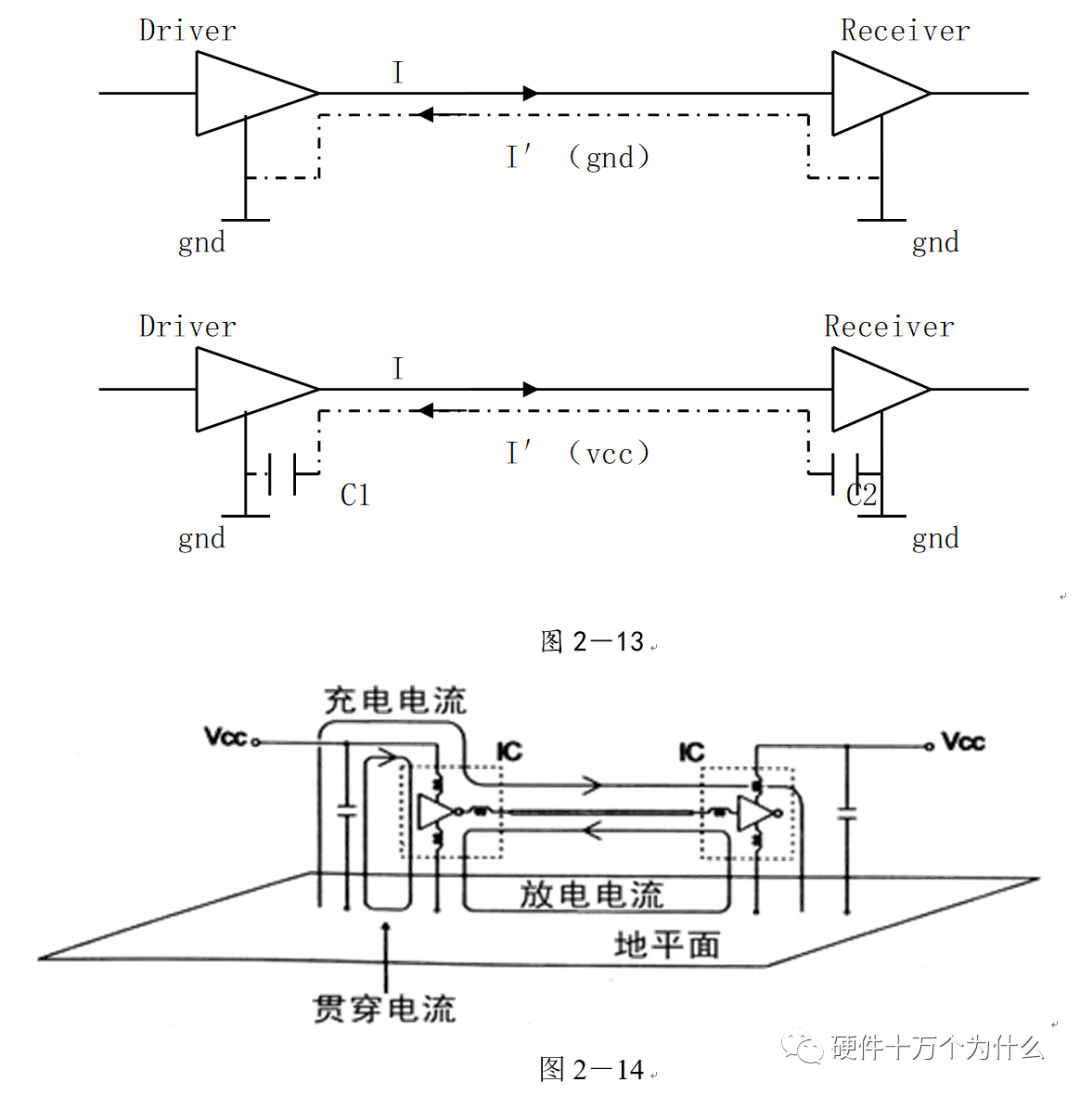

4、控制信號線的回流路徑

EMI取決于兩個諧振回路,一個是“旁路環路”,由IC和旁路電容構成;另一個是“信號環路”,包括信號線在內。根據克希霍夫定律,任何時域信號由源到負載的傳輸都必須有一個最低阻抗的路徑。圖中I=I′,大小相等,方向相反。圖中I我們稱為信號電流,

I′稱為映象電流,如果信號電流下方是電源層,此時的映象電流回路是通過電容耦合所達到的。見圖2-13。

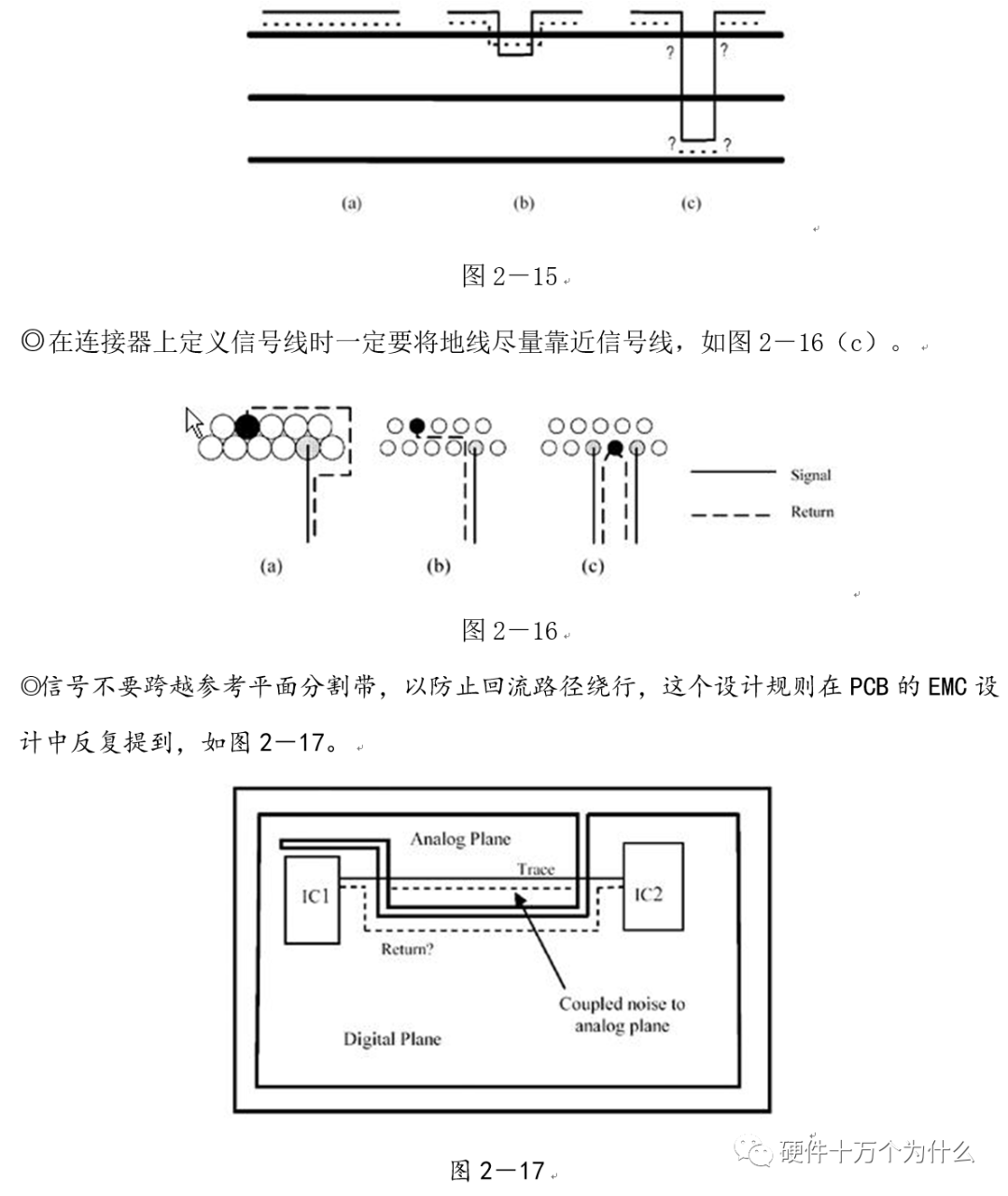

由此,我們得出在多層PCB中應遵循以下基本原則:

◎電源平面緊貼地平面。

◎信號層和參考平面層靠近,保證信號和回流組成的最小面積,重要信號應該以地平面作參考平面。

◎保證電源與地層阻抗最低,電源地的阻抗分析在下面的PI分析中將重點介紹。

◎高速信號線在換層時,會出現過孔等阻抗不連續點,應加地過孔或加旁路電容。

5、采用屏蔽過孔抑制EMI

在高速PCB中,電源地之間的噪聲一般通過對外部的連線(如網線)或PCB的邊緣輻射,在PCB邊緣加上屏蔽過孔對邊緣輻射起到阻隔的作用。

6、相鄰平面層的交疊處理

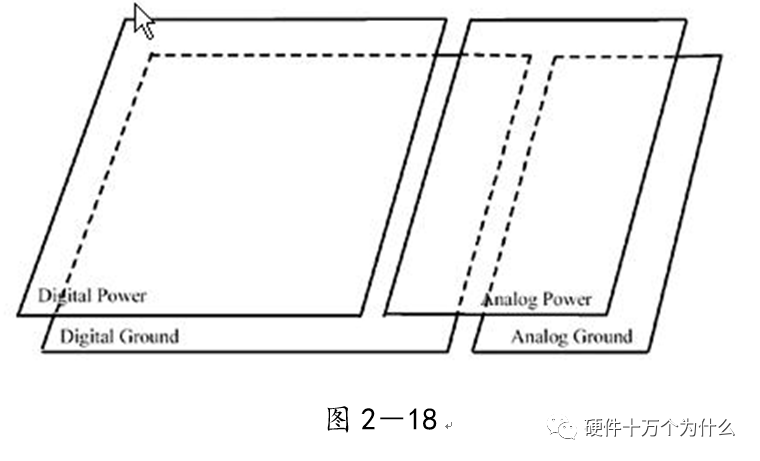

不要將沒有聯系的平面之間形成交疊,如:模擬電源/模擬地與數字電源/數字地,兩者要嚴格分開,不要在平面上存在容性耦合,如圖2-18所示。

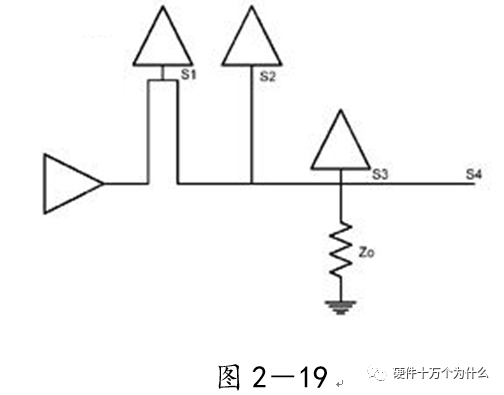

7、信號拓撲中Stub的控制

在高速PCB設計中,尤其要注意盡量減小高速信號的Stub長度,減小“尾巴”的反射,如圖2-19中的S3-S4部分。

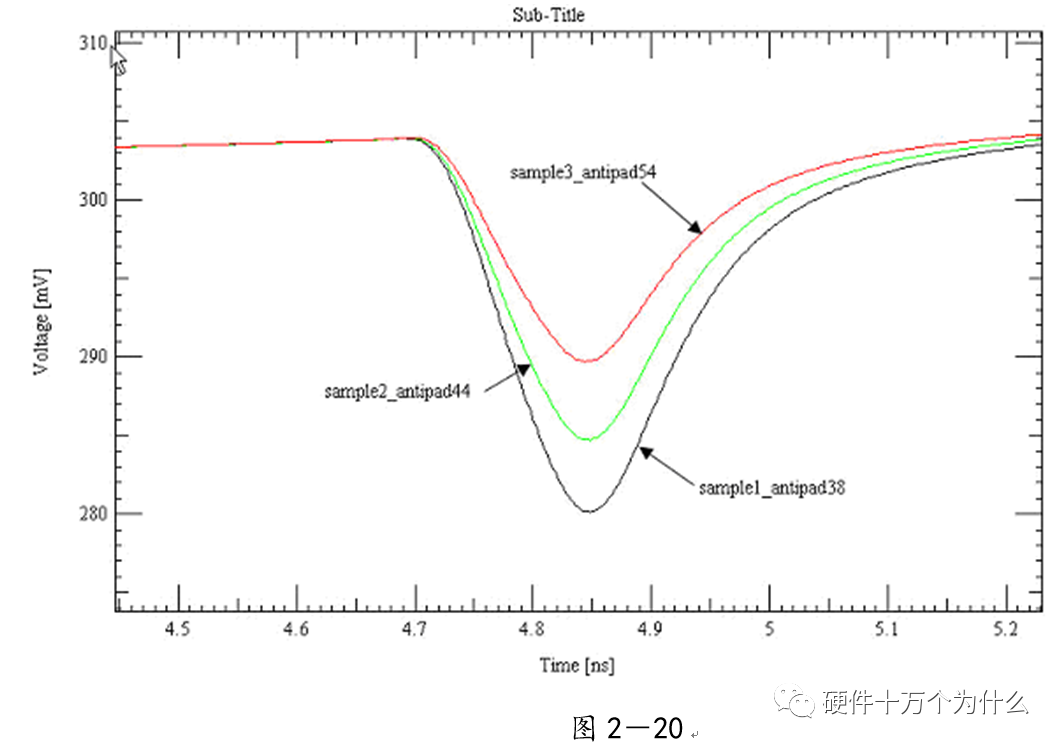

8、高速線過孔的優化問題

這類問題在高速背板設計文檔中有詳盡介紹,本文以一常用的過孔的實例介紹過孔的反焊盤的優化過程,我們設計了三種過孔結構的樣板,過孔為12mil,焊盤為24mil,反焊盤分別為38mil/44mil/54mil,三種反焊盤的尺寸的TDR仿真分析結果對比如圖2-20所示。

由此,我們可以得出結論,隨著過孔反焊盤的加大,過孔的阻抗不連續的情況會得到改善。

(上例中過孔兩端的差分阻抗為100ohm)。

高速PCB的電源完整性仿真要領與實例

高速PCB的SI與PI分析是高速電路設計的重要部分,SI和PI兩者是相輔相成的關系,完善的PI設計是保證SI的基礎,S-PI設計的成功會帶來EMI的改善或者為EMC設計爭取更大的設計余量與空間,減少EMC的設計難度,為高速PCB的EMC問題的最終解決奠定基礎。

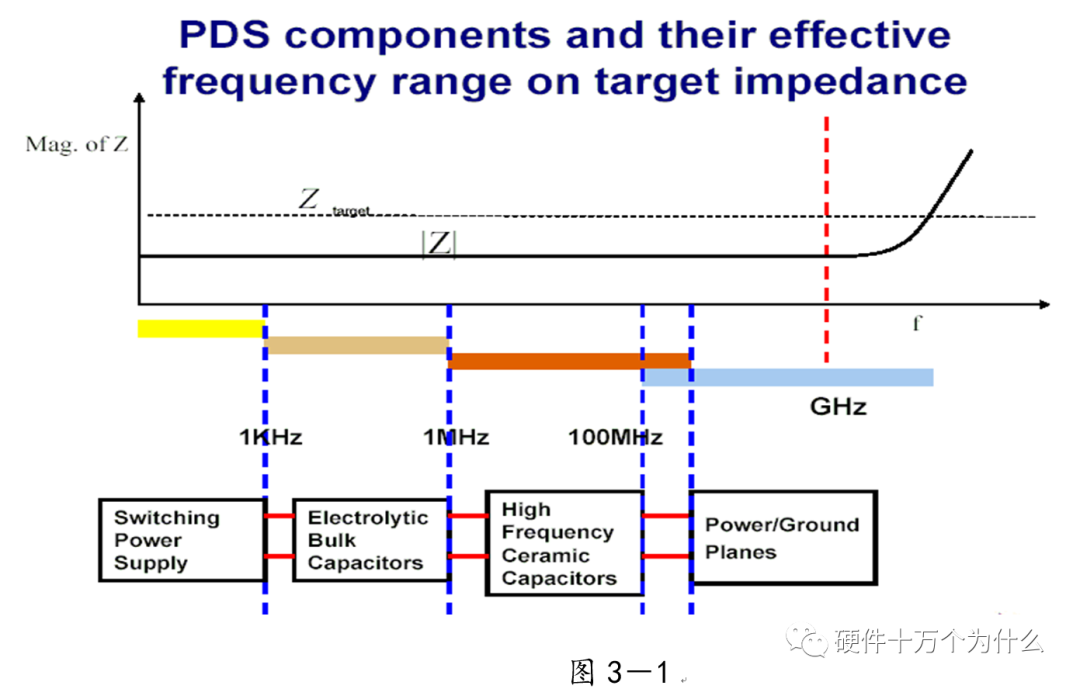

對于電源分布系統(PDS)的設計,在本文中首先關注的對象是:電源/地平面的阻抗,圖3-1顯示了PCB的PDS設計中不同頻率范圍,我們選用的電容是不一樣的,不同的電容都有自己的適用范圍,在1KHz以下,主要控制對象在開關電源;從1KHz到1MHz,我們采用電解電容來完成濾波,從1MHz到100MHz,我們通常選用用高頻陶瓷電容;對于高頻段,我們關注的對象是電源地平面的設計。高頻段是PI設計也是EMI分析的難點,PCB設計顯得尤為重要。

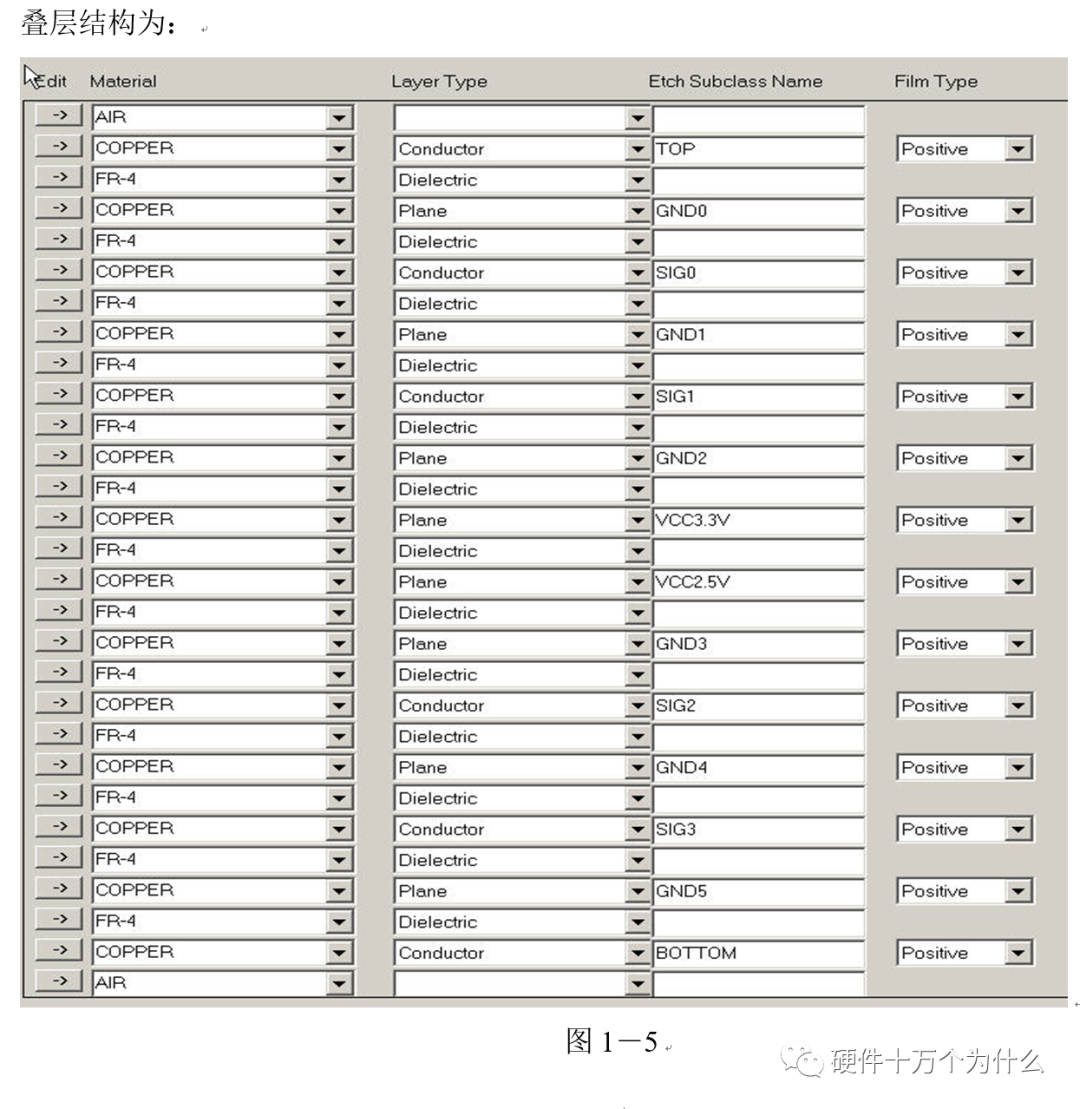

下面介紹一例復雜單板的電源地阻抗分析與控制過程,該單板的疊層結構如圖1-5,在仿真過程中為了優化電容的引線方式,減小寄生電感,對該板的疊層結構做了取樣分析與計算,得到的電容引線電感的分析數據如第一章所述,以下是電源地阻抗的解決過程:

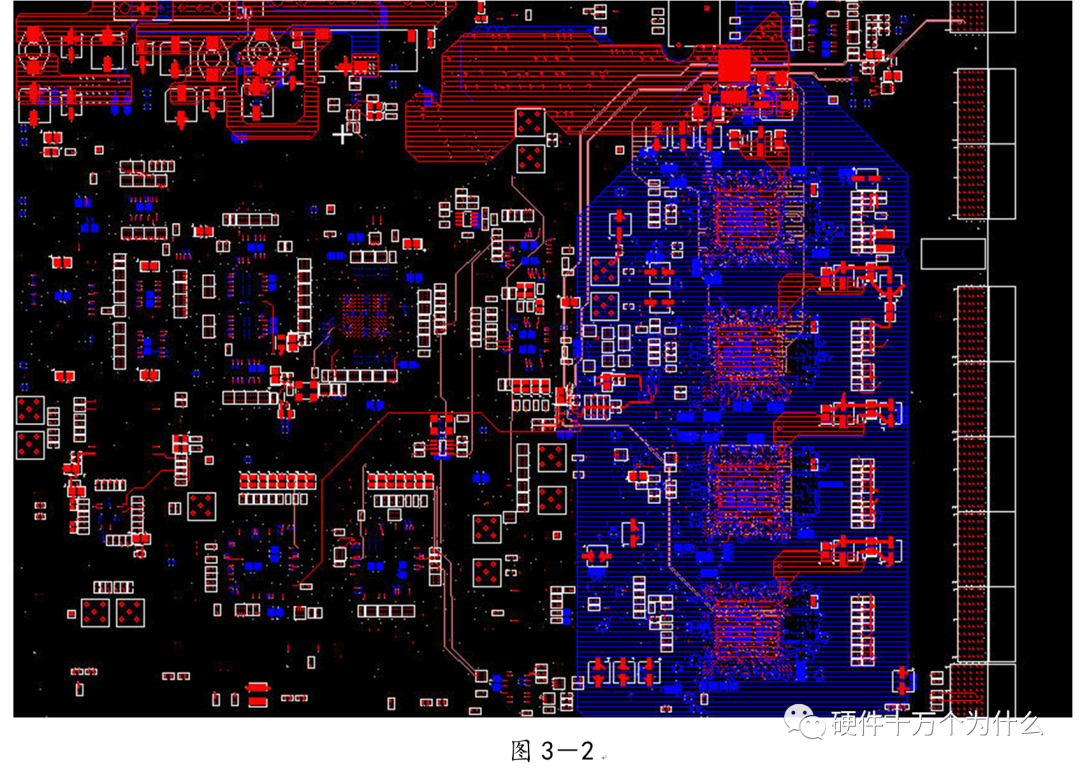

該板的設計難點是VCC1.8V和GND的阻抗,由于VCC1.8V是芯片的核電壓,在PCB的局部區域采用,因此,在PCB上沒有完整平面,采用在SIG0和BOTTOM鋪銅的方法給芯片供電,圖3-2的蘭色區域是BOTTOM層的VCC1.8V鋪銅。

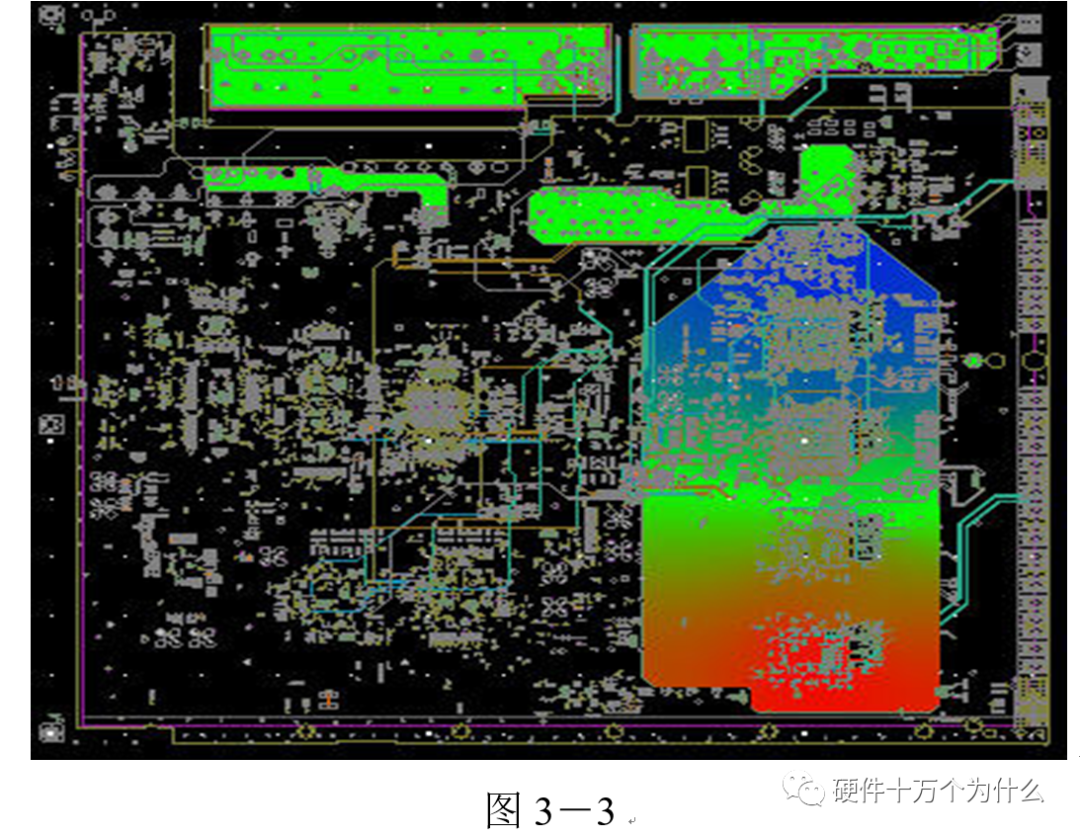

PCB在Resonant模式下VCC1.8/GND的諧振區域如圖3-3。

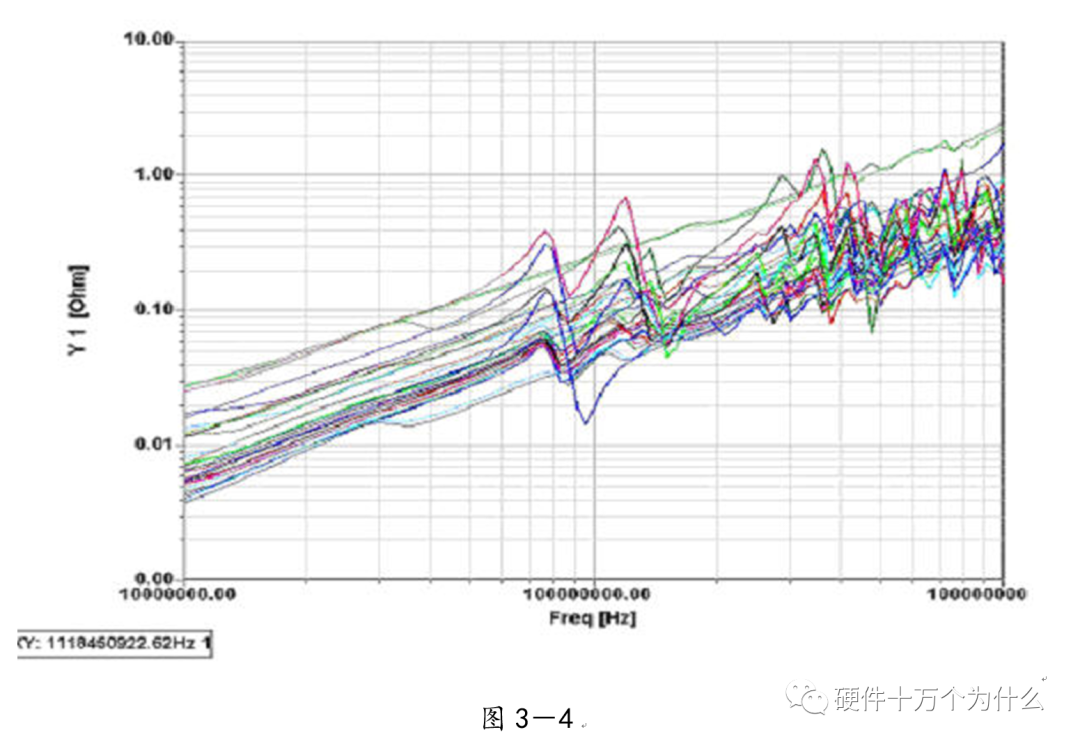

在VCC1.8/GND的各個平面層間定義PORT,得到Z參數曲線如圖3-4。

圖3-4反映了阻抗在高頻段逐步走高的趨勢,這是一個較難解決的問題,因為以往的加旁路電容的方法在這里不能完全解決這類問題,為此,我們對PCB作了以下的改進工作:

a)電容Fanout方式的正確選擇,詳細過程參見圖1-7,考慮到公司的工藝要求與實際PCB的密度,選擇了第二種引線方式,同時將過孔孔徑從12mil調整到16mil,盡量減小過孔電感。

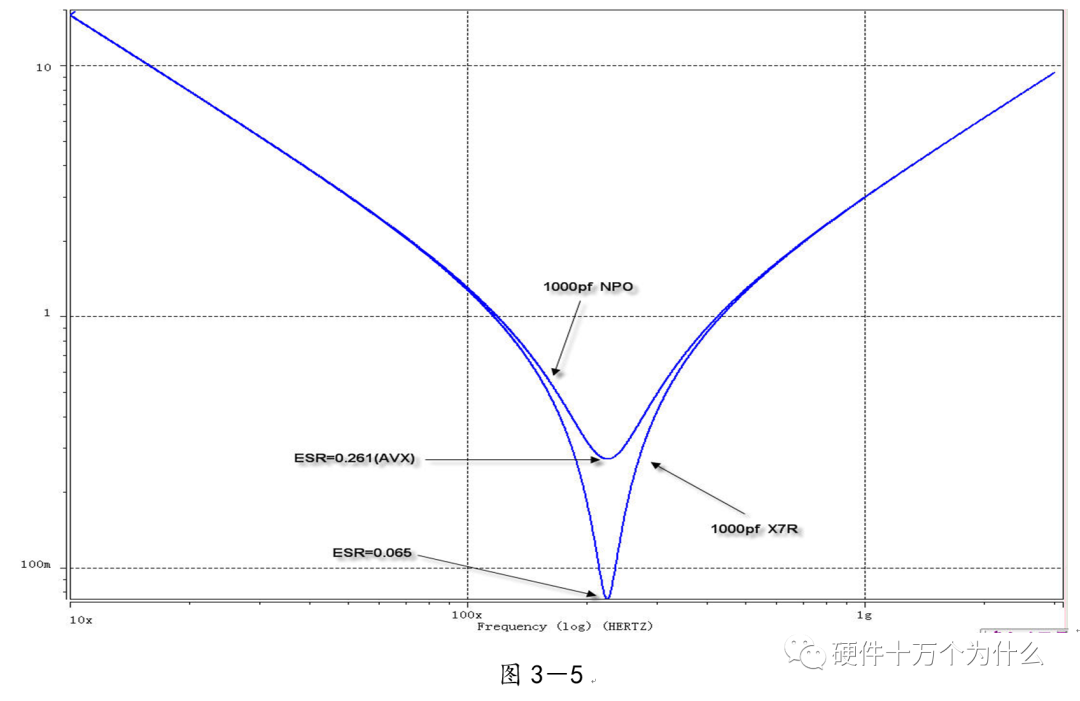

b)適當加一些ESR較低的NPO電容,在本板PI分析中,針對圖3-4的Z參數曲線,在IC芯片周圍等關鍵點增加了60個1000pf的NPO電容,NPO和X7R的阻抗曲線比較如圖3-5所示(未考慮引線),這兩種AVX電容在公司庫中均有代碼,NPO的ESR值為0.065 ohm;X7R的ESR值為0.261 ohm。

c)改進VCC1.8V平面層形狀與結構;

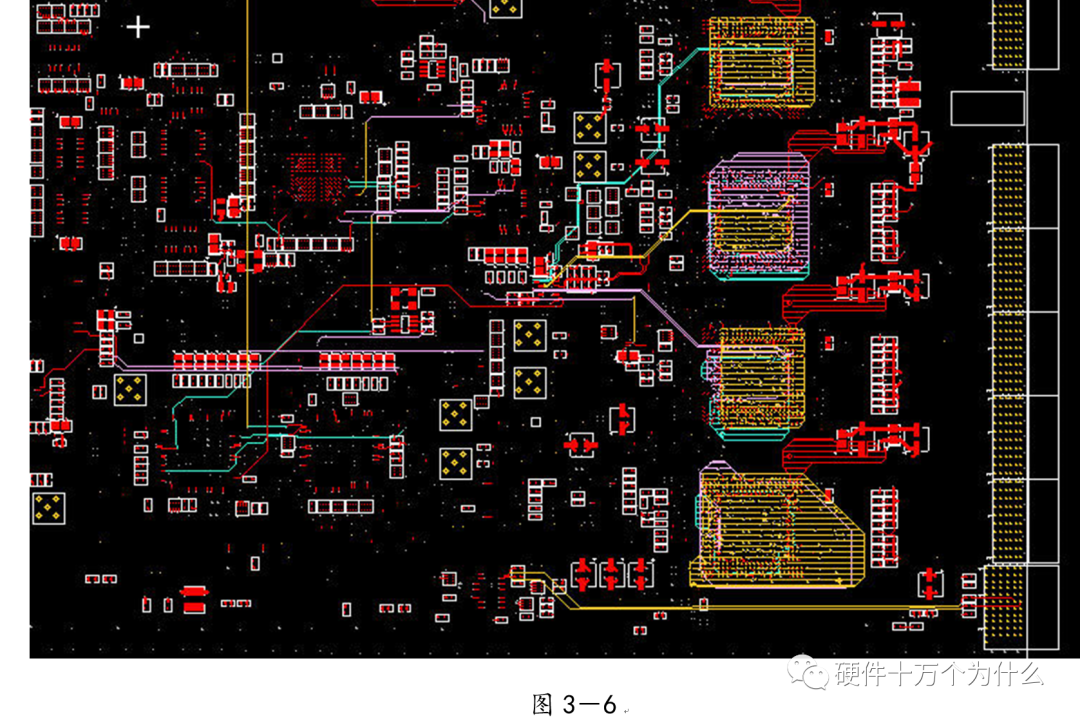

移開BGA下的走線,在其它信號層的BGA下鋪銅,由于該設計的特殊情況,VCC1.8V采用在SIG0與BOTTOM兩層的鋪銅來實現,不如VCC3.3和VCC2.5那樣有完整的平面,因此,增加VCC1.8V與GND之間的平面耦合電容也是解決高頻段阻抗問題的主要手段,如圖3-6所示。

d)在VCC1.8V與GND之間的鋪銅層加地過孔,使各個BGA下的VCC1.8V平面層貫通。

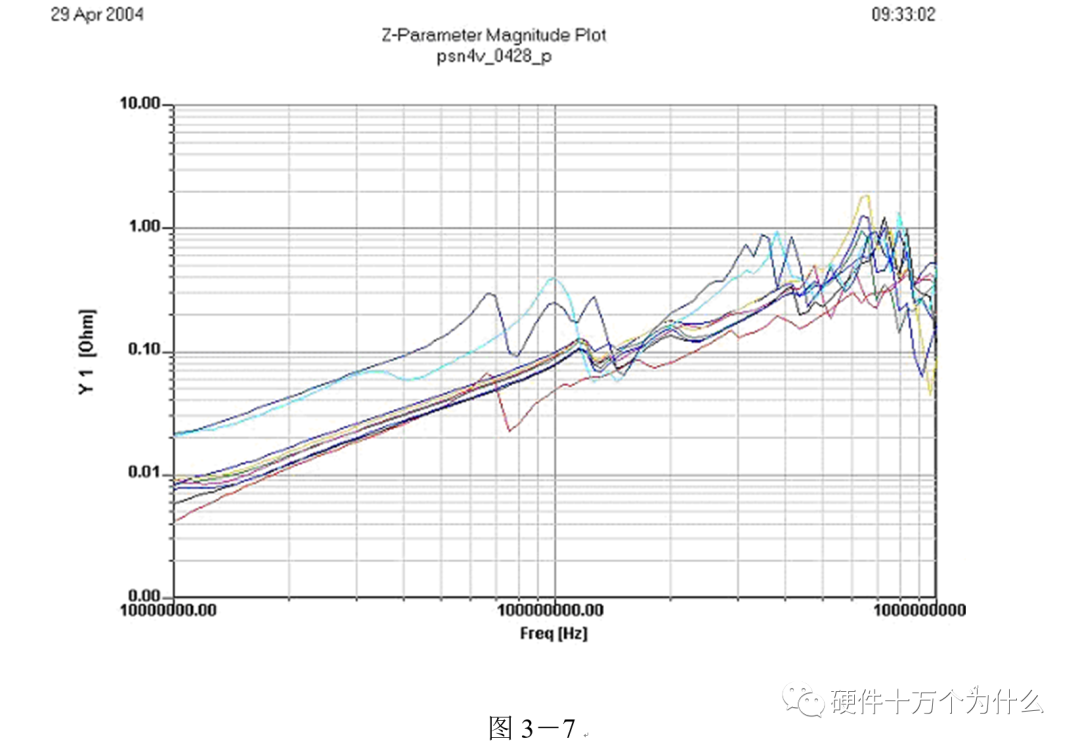

經過以上四步對PCB的改進過程,再將改進后的brd文件重新調入仿真,得到改進后的Z參數曲線如圖3-7所示。

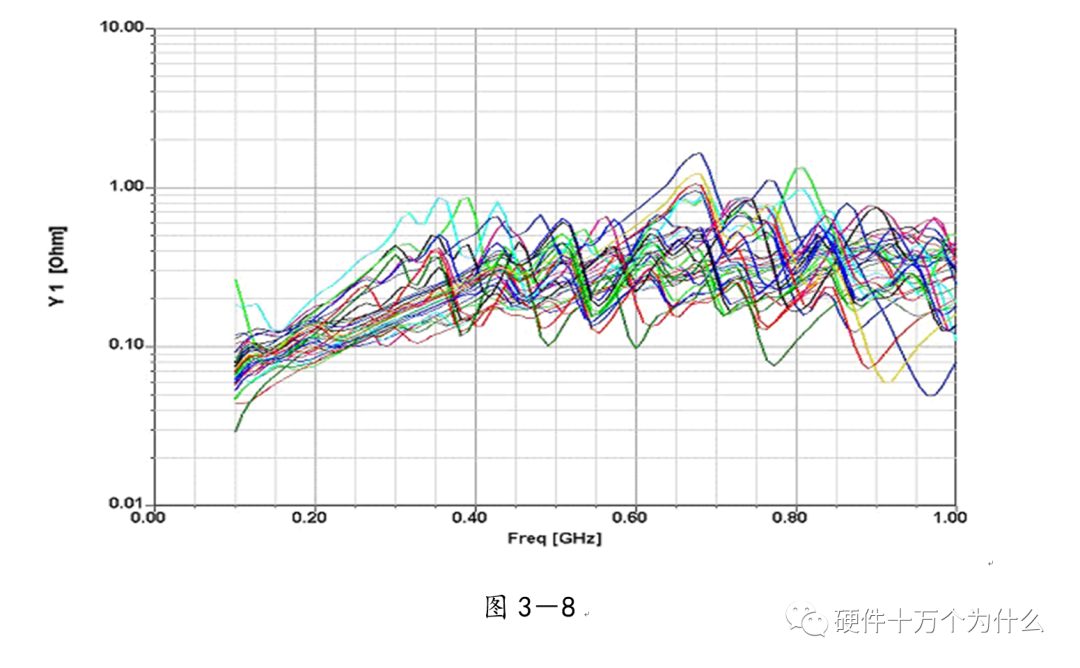

比較圖3-4和圖3-7可以看出,高頻段Z參數曲線的逐步走高的現象得以解決,剩下的問題是解決高頻段部分頻率點的諧振問題,圖3-7高頻段Z參數曲線的放大圖如圖3-8所示。

根據圖3-8的阻抗曲線,我們又著手下一步的改進方案:

1、首先檢查Brd文件,發現放在BOTTOM層BGA下方的有些旁路電容引線方式(線寬與過孔)還沒有按要求調整,另外SIG0和SIG1層4片BGA下方有的鋪銅還可以進一步擴大;

2、增加BGA下的地過孔;

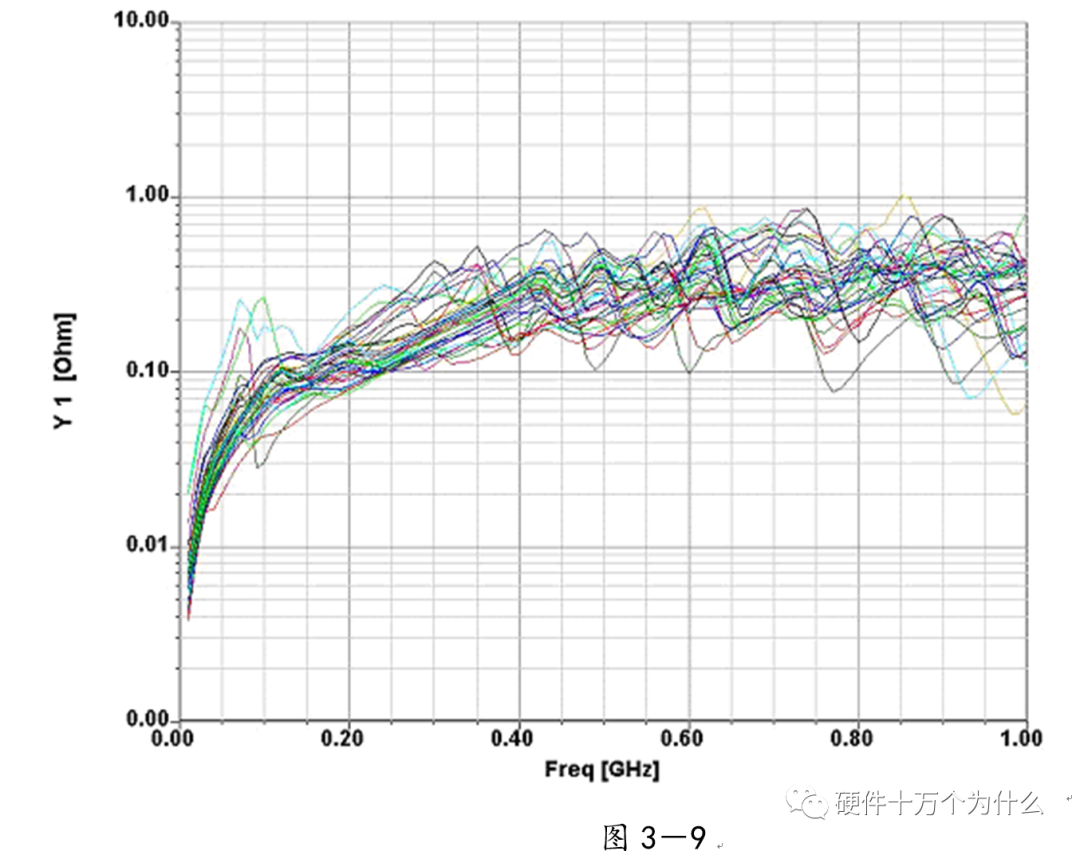

3、由于4片BGA下的空間有限,再增加電容已經不可能,因此采取了更改部分BGA下濾波電容值的辦法解決,首先將原先8個0.1u的退耦電容,取出其中3個改為NPO高頻旁路電容,注意選用高頻段電容時一定要考慮到引線/過孔的影響。通過對BRD文件的進一步改進,得到Z參數曲線如圖3-9。

【電源/地阻抗分析問題總結】

1、PCB的電源地阻抗分析是解決電源地噪聲的關鍵所在,也是PI分析很重要的一步,本章節主要通過實例來說明分析過程;

2、電源地平面結構會對阻抗分析結果產生重要影響;

3、電容的引線方式與過孔的選擇在高速PCB的電源系統分析中不可忽視,尤其在高頻段;

4、由于本文的篇幅有限,對PI仿真的目標阻抗計算,退耦電容的計算、電容的選取、PCB的材料與結構對阻抗的影響等沒有作詳細介紹,大家可以參閱PI設計的相關文檔。

四、結束語

本文主要介紹了高速系統的信號/電源完整性分析及實現方法,集中介紹了電源完整性/信號完整性分析對EMI控制的影響,指出了信號/電源完整性仿真設計和EMC設計的內在聯系,介紹了信號完整性分析和電源完整性分析中應當注意的問題,最后以實例說明PI分析中阻抗分析的過程,希望本文對于從事這方面工作的開發人員能有所借鑒。

高速電路的設計設計過程往往是一個不斷反復的過程,EMC問題的分析與解決過程涉及到電路設計、EDA設計、可靠性設計等方方面面的內容,PCB設計尤其是高速PCB設計優劣是EMI能否得到控制的重要方面,這一點已經被實踐所證明,嚴格的信號完整性仿真與電源完整性仿真可以幫助我們最終解決EMC問題,器件和單板的EMI控制是從根本上解決問題,可以給系統最大的設計空間,這對于提高系統的穩定性和可靠性起到非常重要的作用。

審核編輯:湯梓紅

-

pcb

+關注

關注

4317文章

23002瀏覽量

396228 -

仿真

+關注

關注

50文章

4040瀏覽量

133412 -

eda

+關注

關注

71文章

2708瀏覽量

172865 -

emc

+關注

關注

169文章

3872瀏覽量

182862 -

電源完整性

+關注

關注

8文章

209瀏覽量

20707

原文標題:電源完整性仿真與EMC分析

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

電源完整性仿真與EMC分析

電源完整性仿真與EMC分析

評論