LVDS (Low Voltage Differential Signaling)是一種小振幅差分信號(hào)技術(shù),它使用非常低的幅度信號(hào) (250mV~450mv)通過(guò)一對(duì)平行的 PCB 走線(xiàn)或平衡電纜傳輸數(shù)據(jù)。

在兩條平行的差分信號(hào)線(xiàn)上流經(jīng)的電流及電壓振幅相反,噪聲信號(hào)同時(shí)耦合到兩條線(xiàn)上,而接受端只關(guān)心兩信號(hào)的差值,于是噪聲被抵消。由于兩條信號(hào)線(xiàn)周?chē)碾姶艌?chǎng)也相互抵消,故差分信號(hào)傳輸比單線(xiàn)信號(hào)傳輸電磁輻射小得多。

此外,該傳輸標(biāo)準(zhǔn)采用電流模式驅(qū)動(dòng)輸出,不會(huì)產(chǎn)生振鈴和信號(hào)切換所帶來(lái)的尖峰信號(hào),具有良好的EMI特性。

由于LVDS 差分信號(hào)技術(shù)降低了對(duì)噪聲的關(guān)注,所以可以采用較低的信號(hào)電壓幅度。這個(gè)特性非常重要,它使提高數(shù)據(jù)傳輸率和降低功耗成為可能。低驅(qū)動(dòng)振幅意味著數(shù)據(jù)可更快地反轉(zhuǎn)。

由于驅(qū)動(dòng)器是恒流源模式,功耗幾乎不會(huì)隨頻率而變化,而且單路的功耗非常低。

因此,采用這種技術(shù)后,只要保證一對(duì)平行傳輸線(xiàn)的長(zhǎng)度足夠一致,并在接受端提供良好的匹配端接阻抗技術(shù),以減小反射信號(hào)的產(chǎn)生,就可以提供非常高的數(shù)據(jù)傳輸率。

目前,不用經(jīng)過(guò)復(fù)雜和特殊的處理,提供 840MHZ 的數(shù)據(jù)傳輸速率已經(jīng)非常容易。

LVDS 驅(qū)動(dòng)和接收

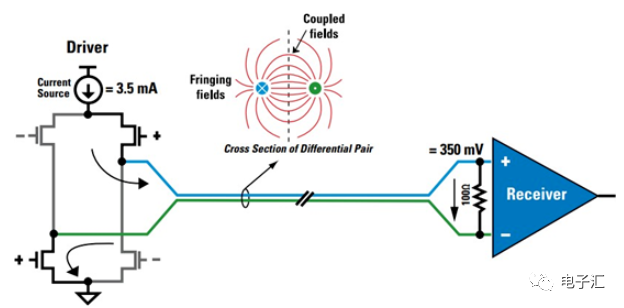

上圖為L(zhǎng)VDS 的工作原理示意圖,其驅(qū)動(dòng)器由個(gè)恒流源(通常為 3.5mA)驅(qū)動(dòng)一對(duì)差分信號(hào)線(xiàn)組成。在接收端有一個(gè)高的直流輸入阻抗(幾乎不會(huì)消耗電流),所以幾乎全部的驅(qū)動(dòng)電流將流經(jīng) 100歐的終端電阻在接收器輸入端產(chǎn)生約 350mV的電壓。

當(dāng)驅(qū)動(dòng)狀態(tài)反轉(zhuǎn)時(shí),流經(jīng)電阻的電流方向改變,于是在接收端產(chǎn)生一個(gè)有效的〞0〞或〞1〞邏輯狀態(tài)。LVDS 技術(shù)特點(diǎn)包括:

1.高速傳輸能力,LVDS 的傳輸能力最高可達(dá) 2Gbps;

2.低電壓、低功耗,LVDS 采用 CMOS 工藝實(shí)現(xiàn),靜態(tài)功耗較低;

3.低噪聲輻射;

4.采用差分傳輸模式有較強(qiáng)的抗干擾能力;

LVDS 比傳統(tǒng)的單端信號(hào)拓?fù)浣Y(jié)構(gòu)(如并行 LVTTL/LVCNOS) 有許多優(yōu)點(diǎn),主要優(yōu)點(diǎn)包括 EMI(電磁干擾)減少,更快的數(shù)據(jù)速率更遠(yuǎn)的擴(kuò)展傳輸距離和成本及便利性。

對(duì)于第 2 代和第 3 代 LVDS SerDes(串行器/解串器),另一個(gè)好處是通過(guò) RBS(隨機(jī)化,DC 平衡,加擾)編碼提高系統(tǒng)可靠性和降低 EMI。靜態(tài)的顯示圖像可以包括許多相同的顏色位,這可能產(chǎn)生 DC漂移并影響信號(hào)質(zhì)量以及創(chuàng)造 EMI 峰值。RBS編碼使數(shù)據(jù)隨機(jī)化并加擾比特位的位置,移除靜態(tài)模式并確保轉(zhuǎn)換正確,然后通過(guò)平衡 DC來(lái)允許 AC耦合并提供隔離。這種編碼的最終結(jié)果是抖動(dòng)更小和通過(guò)更多的傳輸頻譜擴(kuò)展以降低 EMI。

數(shù)據(jù)速率,距離和成本/便利性

由于并行接口的數(shù)據(jù)速率非常有限,故數(shù)據(jù)速率是 LVDS 優(yōu)于 LVTTL / LVCMOS的另一個(gè)好處。如前面所述,當(dāng)許多輸出并行傳輸時(shí),每個(gè)信號(hào)傳播越快,它產(chǎn)生的 EMI就越多。此外,信號(hào)間延時(shí)差也限制了信號(hào)可以傳播的距離,在更快的數(shù)據(jù)速率下會(huì)變得更糟。而使用 LVDS,數(shù)據(jù)速率可以更高,距離也可以延長(zhǎng)至超過(guò) 10米。由于長(zhǎng)度匹配的考慮減少以及更多的使用空間, PCB 的設(shè)計(jì)也容易很多。

在設(shè)計(jì)過(guò)程中,請(qǐng)考慮以下幾點(diǎn):

? EMI

LVDS 信號(hào)濾波設(shè)計(jì)主要針對(duì)如時(shí)鐘信號(hào)、總線(xiàn)信號(hào)做濾波設(shè)計(jì),時(shí)鐘信號(hào)在發(fā)送端增加 RC 濾波設(shè)計(jì),減小時(shí) 鐘對(duì)外的輻射干擾;針對(duì)差分信號(hào),其濾波設(shè)計(jì)需在端口增加共模電感進(jìn)行濾波抑制共模噪聲。

LVDS 信號(hào)抗干擾設(shè)計(jì)分為固定路徑干擾和環(huán)境干擾。

? 固定路徑的干擾

干擾路徑一般為電源或者信號(hào)線(xiàn),故 LVDS 電路設(shè)計(jì)只需要在接口增加防護(hù)設(shè)計(jì),接口增加磁珠吸收后對(duì)地增加電容,使干擾以最快的路徑泄放掉。

? 環(huán)境干擾

這種干擾是由環(huán)境中外部源的電磁輻射引起的,通常使用諸如添加鐵氧體磁珠和電容的保護(hù)措施來(lái)減少這種干擾的影響。

? 為了減少單端信號(hào)和 LVDS信號(hào)之間的串?dāng)_,應(yīng)該遵循:

1.在同一 PCB 層上,單端信號(hào)距離 LVDS 信號(hào)至少 12 mm;

2.差分線(xiàn)之間的距離不應(yīng)超過(guò)信號(hào)線(xiàn)寬度的兩倍, 電路板的厚度應(yīng)大于信號(hào)線(xiàn)之間的距離;

3.兩個(gè)相鄰差分對(duì)之間的距離應(yīng)大于或者等于 2 倍獨(dú)立信號(hào)線(xiàn)之間距離。

? 阻抗匹配

LVDS 信號(hào)設(shè)計(jì)阻抗匹配時(shí),應(yīng)遵循:

1.PCB至少為 4層板,LVDS信號(hào)和 TTL/CMOS信號(hào)需用電源層或地層進(jìn)行隔離; LVDS的驅(qū)動(dòng)器和接收器盡可能靠近連接器放置;

2.靠近驅(qū)動(dòng)器或接收器 Vcc管腳處放置一個(gè) 4.7μF或 10μF 電容,且要考慮信號(hào)的工作頻率和電容最佳工作頻率的匹配性;

3.靠近一個(gè)驅(qū)動(dòng)器或接收器 Vcc管腳處放置至少一個(gè) 0.1μF和一個(gè) 0.001μF電容;

4.電源和地線(xiàn)盡量地寬以降低電源回流阻抗。

審核編輯:湯梓紅

-

pcb

+關(guān)注

關(guān)注

4317文章

23002瀏覽量

396229 -

emi

+關(guān)注

關(guān)注

53文章

3582瀏覽量

127343 -

lvds

+關(guān)注

關(guān)注

2文章

1036瀏覽量

65700 -

差分信號(hào)

+關(guān)注

關(guān)注

3文章

367瀏覽量

27649 -

噪聲信號(hào)

+關(guān)注

關(guān)注

0文章

5瀏覽量

6343

原文標(biāo)題:LVDS基礎(chǔ)知識(shí)

文章出處:【微信號(hào):電子匯,微信公眾號(hào):電子匯】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

labview基礎(chǔ)知識(shí)

通信基礎(chǔ)知識(shí)教程

電子電路基礎(chǔ)知識(shí)

計(jì)算機(jī)基礎(chǔ)知識(shí)介紹

使用Eclipse基礎(chǔ)知識(shí)

LVDS實(shí)現(xiàn)3G基站的高速信號(hào)傳送

電源管理基礎(chǔ)知識(shí)電源管理基礎(chǔ)知識(shí)電源管理基礎(chǔ)知識(shí)

LVDS基礎(chǔ)知識(shí)

LVDS基礎(chǔ)知識(shí)

評(píng)論