最近一直在說(shuō)MOS管的知識(shí),就有朋友留言說(shuō)能具體說(shuō)一下MOS管的導(dǎo)通和關(guān)斷過(guò)程嗎,那我們今天來(lái)說(shuō)一下MOS管的導(dǎo)通和關(guān)斷具體過(guò)程。

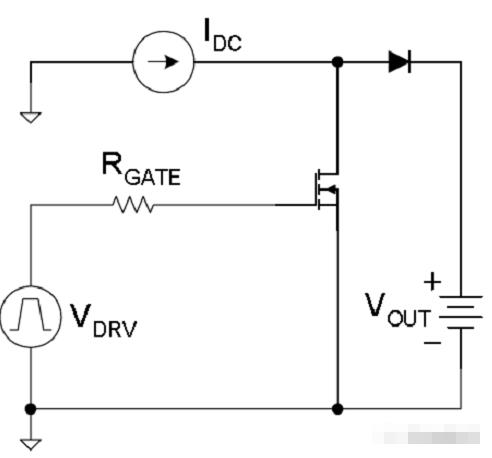

為了更好的理解MOS管的導(dǎo)通和關(guān)斷過(guò)程,我們一般會(huì)將電路中的寄生電感忽略掉,下面我們以一個(gè)最簡(jiǎn)單的鉗位感應(yīng)開(kāi)關(guān)模型來(lái)說(shuō)明。

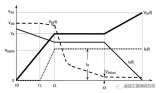

對(duì)于MOS的導(dǎo)通過(guò)程我們可以將其劃分為4個(gè)階段:首先第一個(gè)階段為輸入電容從0開(kāi)始充電到Vth,在這個(gè)過(guò)程中,柵極絕大部分電流都用來(lái)給電容CGS充電,也有很小的電流流過(guò)電容CGS。當(dāng)電容CGS的電壓增加到門的極限時(shí),它的電壓就會(huì)有稍微的減小;這個(gè)過(guò)程稱為導(dǎo)通延遲,這是因?yàn)榇藭r(shí)器件的漏極電流和漏極電壓均未發(fā)生變化;當(dāng)柵極電壓達(dá)到開(kāi)啟電壓時(shí),MOSFET處于微導(dǎo)通狀態(tài)。進(jìn)入第二個(gè)階段。

在第二個(gè)階段中,柵極電壓從Vth上升到Miller平坦區(qū),即VGS。這是器件的線性工作區(qū),電流和柵極電壓成正比。在柵極的一側(cè),電流如第一階段一樣流入電容CGS和CGD,電容VGS的的電壓將會(huì)不斷升高。在器件的輸出端,漏極電流也不斷變大,但是漏源電壓基本不變,保持先前水平(VDS,OFF)。當(dāng)所有電流都流入MOSFET而且二極管完全截止后,漏極電壓必須保持在輸出電壓水平;這時(shí)就進(jìn)入第三個(gè)階段。

進(jìn)入第三個(gè)階段后,柵極電壓已經(jīng)足夠使漏極電流全部通過(guò),而且整流二極管處于完全截止?fàn)顟B(tài)。現(xiàn)在允許漏極電壓下降。在器件漏極電壓下降過(guò)程中,柵源電壓保持不變。這就是柵極電壓波形的Miller平坦區(qū)。從驅(qū)動(dòng)得到的可用的所有柵極電流通過(guò)電容CGD放電,這將加快漏源電壓變化。而漏極電流幾乎不變,這是由于此刻它受外部電路限制。

最后一個(gè)階段是MOS溝道增強(qiáng),處于完全導(dǎo)通狀態(tài),這得益于柵極的電壓已經(jīng)足夠高。最終的VGS電壓幅度將決定器件最終導(dǎo)通阻抗。

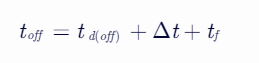

而MOS的關(guān)斷過(guò)程恰好和它的導(dǎo)通過(guò)程是相反的:首先是關(guān)斷延遲,這階段需要電容CISS從最初值電壓放電到Miller平坦區(qū)水平。這期間柵極電流由電容CISS提供,而且它流入MOSFET的電容CGS和CGD。器件的漏極電壓隨著過(guò)載電壓的減小而略微的增大,然后進(jìn)入第二個(gè)階段,管子的漏源電壓從IDC·RDS(On)增加到最終值(VDS(off)),進(jìn)而促使二極管導(dǎo)通,進(jìn)入第三個(gè)階段,二極管給負(fù)載電流提供另一通路;柵極電壓從VGS,Miller降到Vth;大部分的柵極電流來(lái)自于電容CGS,在這個(gè)階段的最后漏極電流幾乎達(dá)到0;但是由于整流二極管的正向偏置,所以漏極電壓將維持在VDS(off)。

截止過(guò)程的最后一個(gè)階段是器件的輸入電容完全放電:電壓VGS進(jìn)一步減小到0;占柵極電流較大比例部分的電流,和截止過(guò)程的第三階段一樣,由電容CGS提供;器件的漏極電流和漏極電壓保持不變。

-

MOS管

+關(guān)注

關(guān)注

107文章

2293瀏覽量

65460 -

導(dǎo)通

+關(guān)注

關(guān)注

1文章

31瀏覽量

11220 -

寄生電感

+關(guān)注

關(guān)注

1文章

152瀏覽量

14536 -

MCGS

+關(guān)注

關(guān)注

11文章

87瀏覽量

34724 -

關(guān)斷

+關(guān)注

關(guān)注

0文章

17瀏覽量

8147

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

MOS管燒壞常見(jiàn)的可能性故障分析

MOS管損壞的原因及解決方案

MOS管的導(dǎo)通條件 MOS管的導(dǎo)通過(guò)程

功率MOS管燒毀的原因

MOS管的開(kāi)通/關(guān)斷原理

導(dǎo)通損耗和關(guān)斷損耗的相關(guān)資料推薦

討論一下IGBT的關(guān)斷過(guò)程

功率MOS管損壞的主要原因

什么是MOS管?MOS管損壞的原因有哪些

MOS管竟然是這樣燒壞的

MOS管是如何燒壞的

功率MOS管燒毀的原因(米勒效應(yīng))

關(guān)于對(duì)IGBT關(guān)斷過(guò)程的分析

igbt怎樣導(dǎo)通和關(guān)斷?igbt的導(dǎo)通和關(guān)斷條件

IGBT關(guān)斷過(guò)程分析

MOS管的導(dǎo)通和關(guān)斷過(guò)程

MOS管的導(dǎo)通和關(guān)斷過(guò)程

評(píng)論