在現代SoC芯片驗證過程中,不可避免的都會使用FPGA原型驗證,或許原型驗證一詞對你而言非常新鮮,但是FPGA上板驗證應該是非常熟悉的場景了。通常有三種方式:第一種,自己制作FPGA電路板,用來驗證自身SoC設計;第二種,購買FPGA原廠的開發板,用來搭建FPGA原型驗證系統;第三種,對于大型的SoC芯片,一般會購買專業的FPGA原型驗證平臺,用來搭建其原型驗證平臺。

為什么SoC驗證一定需要FPGA原型驗證呢??

基于FPGA原型驗證,可以提供更高的驗證精度和驗證性能;

基于FPGA原型驗證,可以在實驗室真實硬件環境測試與展示。

FPGA原型驗證可以用來做什么?

由于其高精度和高性能,可以測試實時數據流,更早期地進行軟硬件的協同,同步進行硬件與軟件的早期開發與驗證;

由于其真實世界的模擬,可以在SoC流片之前進行真實世界數據交互效果,可以測到在仿真環境中無法模擬的罕見的一些隨機場景,并且可以進行人機交互的測試;

由于其真實硬件展示的特性,可以進行可行性評估與展示,以此給投資者信心。

雖然在Simulation階段已經對RTL進行了大量的測試,但是原型驗證可以結合軟件進一步擴展RTL的驗證與調試。

01

高性能和高精度

只有基于FPGA的原型設計才能提供正確測試設計的許多方面所需的速度和精度,這是團隊進行原型設計的最可能的根本原因。整個團隊的目標可能是驗證SoC相關的嵌入式軟件系統,看它如何在真實硬件上快速運行。

02

實時數據流

驗證SoC很難的部分原因是,SoC的狀態取決于許多變量,包括其先前的狀態、輸入序列和SoC輸出的更廣泛的系統影響。以實時速度運行SoC設計,將其連接到系統的其他部分,使我們能夠看到實時條件、輸入和系統反饋的即時影響。

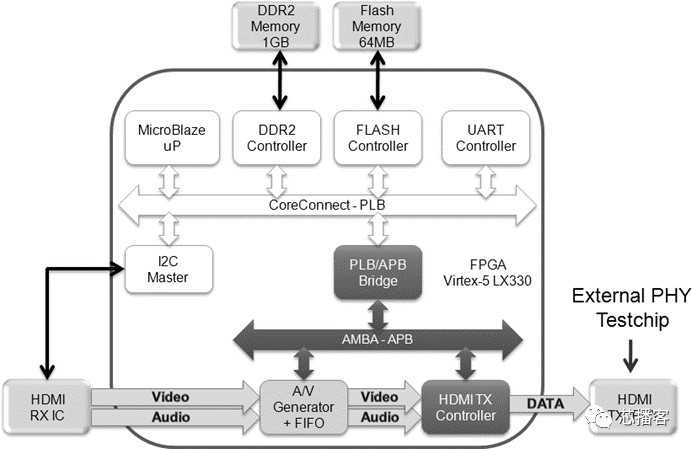

一個高清媒體數據流通過一個處理器核心的原型被路由到一個高清顯示器。當我們在原型中考慮IP使用時,在圖的底部,有來自接收器的音頻和高清視頻數據流通過原型實時傳輸到外部監視器的實時HDMI PHY連接。只有基于FPGA的原型設計才允許這種實時數據流,這不僅給這種多媒體應用帶來了巨大的好處,也給許多其他需要對輸入數據流進行實時響應的應用帶來了極大的好處。

03

軟硬件早期集成

在上面的例子中,有一個小的MicroBlaze原型中的CPU以及外圍設備和存儲器,因此SoC中所有熟悉的模塊都存在。在這種設計中,CPU中運行的軟件主要用于加載和控制AV處理,然而,在許多SoC設計中,它是需要大部分設計工作的軟件。

鑒于軟件已經成為SoC開發工作的主導,軟件工作處于項目進度的關鍵路徑上的情況越來越普遍。軟件開發和驗證決定了SoC能夠有效達到批量生產的實際完成日期。在這種情況下,系統團隊可以做什么來提高軟件開發和驗證的生產力?硬件系統盡早搭建完成可以及早的進行軟硬件系統的協同驗證,而FPGA原型驗證,正是順應了這種趨勢。

04

軟件開發的SoC建模

任何級別的SoC建模都需要我們表示硬件和堆棧,直到當前級別以下的層,以進行驗證,并且最佳情況下,我們應該以足夠的精度進行工作,以實現最大性能。

例如,堆棧頂部的應用程序開發人員可以在真實的SoC或模型上測試他們的代碼。在這種情況下,模型只需要足夠精確,以欺騙應用程序,使其認為它運行在真正的SoC上,即,它不需要硬件的周期精度或細粒度可見性。然而,速度很重要,因為在許多情況下,多個應用程序將同時運行并與真實世界數據交互。這種模型對軟件層具有“剛剛足夠的精度”的方法導致了SoC項目期間不同軟件開發人員在不同時間使用的許多不同建模環境。

可以使用事務級模擬,以SystemC等語言建模,以創建以低精度運行但以足夠高的速度運行許多應用程序的模擬器模型。如果實時、真實世界數據的處理并不重要,那么我們最好考慮采用這種虛擬原型方法。然而,當整個軟件堆棧必須一起運行或必須處理真實數據時,基于FPGA的原型設計變得最有用。

總結

今天的SoC是許多不同專家的工作組合,從算法研究人員到硬件設計師,到軟件工程師,再到芯片布局團隊,隨著項目的進展,每個SoC都有自己的需求。SoC項目的成功在很大程度上取決于上述專家使用的硬件驗證、硬件-軟件聯合驗證和軟件驗證方法。基于FPGA的原型設計為這些專家帶來了不同的好處:

對于硬件團隊來說,驗證工具的速度對驗證吞吐量起著重要作用。在大多數SoC開發中,隨著項目的成熟,有必要進行多次模擬和重復回歸測試。仿真器和模擬器是用于該類型RTL驗證的最常用平臺。然而,由于運行時間長,即使使用基于TLM的模擬和建模,RTL內或RTL與外部刺激之間的某些交互也無法在模擬或仿真中重新創建。。因此,一些團隊使用基于FPGA的原型設計為此類硬件測試提供更高性能的平臺。例如,我們可以相對實時地運行整個OS引導,從而節省幾天的模擬時間來實現相同的目標。

對于軟件團隊來說,基于FPGA的原型設計為目標硅提供了一個獨特的硅前模型,該模型足夠快速和準確,能夠在接近最終條件下調試軟件。

對于整個團隊來說,SoC項目的一個關鍵階段是軟件和硬件首次相互介紹。硬件將由最終軟件以硬件驗證計劃未單獨設想或預測的方式進行測試,從而暴露出新的硬件問題。這在多核系統或運行并發實時應用程序的系統中尤為普遍。如果這種硬件軟件的引入是在第一次硅制造之后才發生的,那么溫和地說,在那個時候發現新的bug是不理想的。

基于FPGA的原型允許盡早將軟件引入硬件的周期準確和快速模型。SoC團隊經常告訴我們,基于FPGA的原型設計的最大好處是,當第一塊硅可用時,系統和軟件一天就能啟動并運行。

審核編輯:劉清

-

FPGA

+關注

關注

1620文章

21507瀏覽量

598845 -

HDMI

+關注

關注

32文章

1594瀏覽量

151131 -

soc

+關注

關注

38文章

4020瀏覽量

217008 -

RTL

+關注

關注

1文章

384瀏覽量

59506

原文標題:為什么要做FPGA原型驗證?

文章出處:【微信號:于博士Jacky,微信公眾號:于博士Jacky】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

驗證中的FPGA原型驗證 FPGA原型設計面臨的挑戰是什么?

高頻RFID芯片的FPGA原型驗證平臺設計及驗證

基于FPGA原型的GPS基帶驗證系統設計與實現

什么是FPGA原型驗證?如何用FPGA對ASIC進行原型驗證

從SoC仿真驗證到FPGA原型驗證的時機

為什么SoC驗證一定需要FPGA原型驗證呢??

為什么SoC驗證一定需要FPGA原型驗證呢??

評論