1、什么是嵌入式

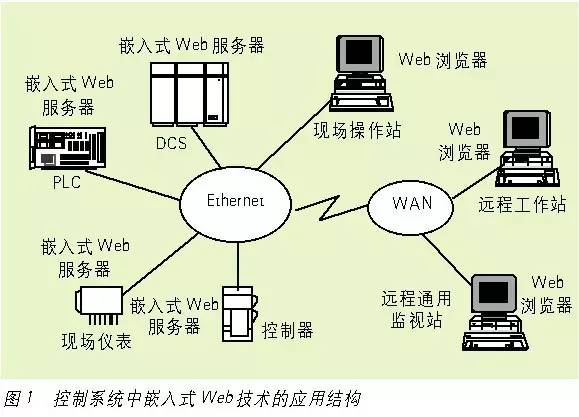

IEEE(Institute of Electrical and Electronics Engineers,美國電氣和電子工程師協(xié)會)對嵌入式系統(tǒng)的定義:“用于控制、監(jiān)視或者輔助操作機器和設(shè)備的裝置”。原文為:Devices Used to Control,Monitor or Assist the Operation of Equipment,Machinery or Plants)。

嵌入式系統(tǒng)是一種專用的計算機系統(tǒng),作為裝置或設(shè)備的一部分。通常,嵌入式系統(tǒng)是一個控制程序存儲在ROM中的嵌入式處理器控制板。事實上,所有帶有數(shù)字接口的設(shè)備,如手表、微波爐、錄像機、汽車等,都使用嵌入式系統(tǒng),有些嵌入式系統(tǒng)還包含操作系統(tǒng),但大多數(shù)嵌入式系統(tǒng)都是由單個程序?qū)崿F(xiàn)整個控制邏輯。

從應(yīng)用對象上加以定義,嵌入式系統(tǒng)是軟件和硬件的綜合體,還可以涵蓋機械等附屬裝置。國內(nèi)普遍認同的嵌入式系統(tǒng)定義為:以應(yīng)用為中心,以計算機技術(shù)為基礎(chǔ),軟硬件可裁剪,適應(yīng)應(yīng)用系統(tǒng)對功能、可靠性、成本、體積、功耗等嚴格要求的專用計算機系統(tǒng)。

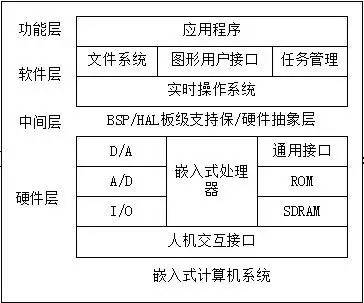

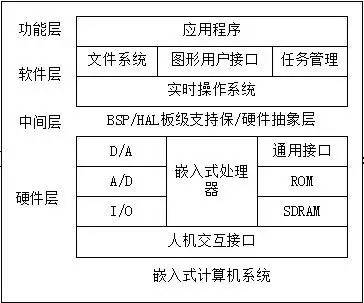

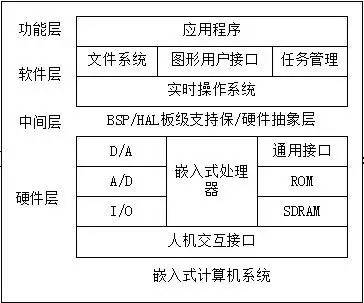

一個嵌入式系統(tǒng)裝置一般都由嵌入式計算機系統(tǒng)和執(zhí)行裝置組成,嵌入式計算機系統(tǒng)是整個嵌入式系統(tǒng)的核心,由硬件層、中間層、系統(tǒng)軟件層和應(yīng)用軟件層組成。執(zhí)行裝置也稱為被控對象,它可以接受嵌入式計算機系統(tǒng)發(fā)出的控制命令,執(zhí)行所規(guī)定的操作或任務(wù)。執(zhí)行裝置可以很簡單,如手機上的一個微小型的電機,當手機處于震動接收狀態(tài)時打開;也可以很復雜,如SONY 智能機器狗,上面集成了多個微小型控制電機和多種傳感器,從而可以執(zhí)行各種復雜的動作和感受各種狀態(tài)信息。

2、嵌入式系統(tǒng)的組成

一、 硬件層 硬件層中包含嵌入式微處理器、存儲器(SDRAM、ROM、Flash等)、通用設(shè)備接口和I/O接口(A/D、D/A、I/O等)。在一嵌入式處理器基礎(chǔ)上添加電源電路、時鐘電路和存儲器電路,就構(gòu)成了一個嵌入式核心控制模塊。其中操作系統(tǒng)和應(yīng)用程序都可以固化在ROM中.

二、 中間層 硬件層與軟件層之間為中間層,也稱為硬件抽象層(Hardware Abstract Layer,HAL)或者板級支持包(Board Support Package,BSP),它半系統(tǒng)上層軟件與底層硬件分離開來,使系統(tǒng)的底層驅(qū)動程序與硬件無關(guān),上層軟件開發(fā)人員無需關(guān)心底層硬件的具體情況,根據(jù)BSP層提供的接口即可進行開發(fā)。該層一般包含相關(guān)底層硬件的初始化、數(shù)據(jù)的輸入/輸出操作和硬件設(shè)備的配置功能。 實際上,BSP是一個介于操作系統(tǒng)和底層硬件之間的軟件層次,包括了系統(tǒng)中大部分與硬件聯(lián)系緊密的軟件模塊。設(shè)計一個完整的BSP需要完成兩部分工作:嵌入工系統(tǒng)的硬件初始化的BSP功能,設(shè)計硬件相關(guān)的設(shè)備驅(qū)動。

三、 系統(tǒng)軟件層 系統(tǒng)軟件層由實時多任務(wù)操作系統(tǒng)(Real-time Operation System,RTOS)、文件系統(tǒng)、圖形用戶接口(Graphic User Interface,GUI)、網(wǎng)絡(luò)系統(tǒng)及通用組件模塊組成。RTOS是嵌入式應(yīng)用軟件的基礎(chǔ)和開發(fā)平臺。

3、實時系統(tǒng)

(1)定義:能在指定或確定的時間內(nèi)完成系統(tǒng)功能和對外部或內(nèi)部、同步或異步時間做出響應(yīng)的系統(tǒng)。

(2)區(qū)別:通用系統(tǒng)一般追求的是系統(tǒng)的平均響應(yīng)時間和用戶的使用方便;而實時系統(tǒng)主要考慮的是在最壞情況下的系統(tǒng)行為。

(3)特點:時間約束性、可預(yù)測性、可靠性、與外部環(huán)境的交互性。

(4)硬實時(強實時):指應(yīng)用的時間需求應(yīng)能夠得到完全滿足,否則就造成重大安全事故,甚至造成重大的生命財產(chǎn)損失和生態(tài)破壞,如:航天、軍事。

(5)軟實時(弱實時):指某些應(yīng)用雖然提出了時間的要求,但實時任務(wù)偶爾違反這種需求對系統(tǒng)運行及環(huán)境不會造成嚴重影響,如:監(jiān)控系統(tǒng)、實時信息采集系統(tǒng)。

(6)任務(wù)的約束包括:時間約束、資源約束、執(zhí)行順序約束和性能約束。

5、實時系統(tǒng)的調(diào)度

(1)調(diào)度:給定一組實時任務(wù)和系統(tǒng)資源,確定每個任務(wù)何時何地執(zhí)行的整個過程。

(2)搶占式調(diào)度:通常是優(yōu)先級驅(qū)動的調(diào)度,如uCOS。優(yōu)點是實時性好、反應(yīng)快,調(diào)度算法相對簡單,可以保證高優(yōu)先級任務(wù)的時間約束;缺點是上下文切換多。

(3)非搶占式調(diào)度:通常是按時間片分配的調(diào)度,不允許任務(wù)在執(zhí)行期間被中斷,任務(wù)一旦占用處理器就必須執(zhí)行完畢或自愿放棄,如WinCE。優(yōu)點是上下文切換少;缺點是處理器有效資源利用率低,可調(diào)度性不好。

(4)靜態(tài)表驅(qū)動策略:系統(tǒng)在運行前根據(jù)各任務(wù)的時間約束及關(guān)聯(lián)關(guān)系,采用某種搜索策略生成一張運行時刻表,指明各任務(wù)的起始運行時刻及運行時間。

(5)優(yōu)先級驅(qū)動策略:按照任務(wù)優(yōu)先級的高低確定任務(wù)的執(zhí)行順序。

(6)實時任務(wù)分類:周期任務(wù)、偶發(fā)任務(wù)、非周期任務(wù)。

(7)實時系統(tǒng)的通用結(jié)構(gòu)模型:數(shù)據(jù)采集任務(wù)實現(xiàn)傳感器數(shù)據(jù)的采集,數(shù)據(jù)處理任務(wù)處理采集的數(shù)據(jù)、并將加工后的數(shù)據(jù)送到執(zhí)行機構(gòu)管理任務(wù)控制機構(gòu)執(zhí)行。

5、嵌入式微處理器體系結(jié)構(gòu)

(1)馮諾依曼結(jié)構(gòu):程序和數(shù)據(jù)共用一個存儲空間,程序指令存儲地址和數(shù)據(jù)存儲地址指向同一個存儲器的不同物理位置,采用單一的地址及數(shù)據(jù)總線,程序和數(shù)據(jù)的寬度相同。例如:8086、ARM7、MIPS…

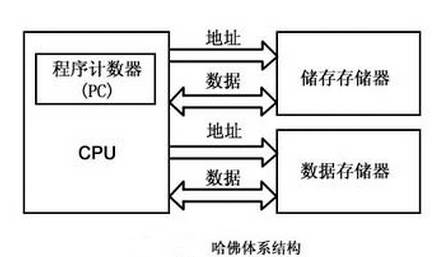

(2)哈佛結(jié)構(gòu):程序和數(shù)據(jù)是兩個相互獨立的存儲器,每個存儲器獨立編址、獨立訪問,是一種將程序存儲和數(shù)據(jù)存儲分開的存儲器結(jié)構(gòu)。例如:AVR、ARM9、ARM10…

(3)CISC與RISC的特點比較。

計算機執(zhí)行程序所需要的時間P可以用下面公式計算:

P=I×CPI×T

I:高級語言程序編譯后在機器上運行的指令數(shù)。

CPI:為執(zhí)行每條指令所需要的平均周期數(shù)。

T:每個機器周期的時間。

(4)流水線的思想:在CPU中把一條指令的串行執(zhí)行過程變?yōu)槿舾芍噶畹淖舆^程在CPU中重疊執(zhí)行。

(5)流水線的指標:

吞吐率:單位時間里流水線處理機流出的結(jié)果數(shù)。如果流水線的子過程所用時間不一樣長,則吞吐率應(yīng)為最長子過程的倒數(shù)。

建立時間:流水線開始工作到達最大吞吐率的時間。若m個子過程所用時間一樣,均為t,則建立時間T=mt。

(6)信息存儲的字節(jié)順序

A、存儲器單位:字節(jié)(8位)

B、字長決定了微處理器的尋址能力,即虛擬地址空間的大小。

C、32位微處理器的虛擬地址空間位232,即4GB。

D、小端字節(jié)順序:低字節(jié)在內(nèi)存低地址處,高字節(jié)在內(nèi)存高地址處。

E、大端字節(jié)順序:高字節(jié)在內(nèi)存低地址處,低字節(jié)在內(nèi)存高地址處。

F、網(wǎng)絡(luò)設(shè)備的存儲順序問題取決于OSI模型底層中的數(shù)據(jù)鏈路層。

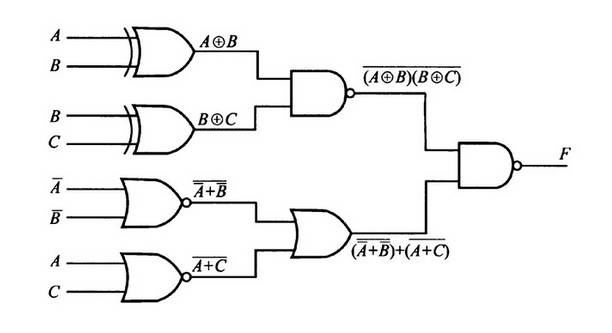

6、邏輯電路基礎(chǔ)

(1)根據(jù)電路是否具有存儲功能,將邏輯電路劃分為:組合邏輯電路和時序邏輯電路。

(2)組合邏輯電路:電路在任一時刻的輸出,僅取決于該時刻的輸入信號,而與輸入信號作用前電路的狀態(tài)無關(guān)。常用的邏輯電路有譯碼器和多路選擇器等。

(3)時序邏輯電路:電路任一時刻的輸出不僅與該時刻的輸入有關(guān),而且還與該時刻電路的狀態(tài)有關(guān)。因此,時序電路中必須包含記憶元件。觸發(fā)器是構(gòu)成時序邏輯電路的基礎(chǔ)。常用的時序邏輯電路有寄存器和計數(shù)器等。

(4)真值表、布爾代數(shù)、摩根定律、門電路的概念。

(5)NOR(或非)和NAND(與非)的門電路稱為全能門電路,可以實現(xiàn)任何一種邏輯函數(shù)。

(6)譯碼器:多輸入多輸出的組合邏輯網(wǎng)絡(luò)。

每輸入一個n位的二進制代碼,在m個輸出端中最多有一個有效。

當m=2n是,為全譯碼;當m《2n時,為部分譯碼。

(7)由于集成電路的高電平輸出電流小,而低電平輸出電流相對比較大,采用集成門電路直接驅(qū)動LED時,較多采用低電平驅(qū)動方式。液晶七段字符顯示器LCD利用液晶有外加電場和無外加電場時不同的光學特性來顯示字符。

(8)時鐘信號是時序邏輯的基礎(chǔ),它用于決定邏輯單元中的狀態(tài)合適更新。同步是時鐘控制系統(tǒng)中的主要制約條件。

(9)在選用觸發(fā)器的時候,觸發(fā)方式是必須考慮的因素。觸發(fā)方式有兩種:

方式1:電平觸發(fā)方式:具有結(jié)構(gòu)簡單的有點,常用來組成暫存器。

方式2:邊沿觸發(fā)方式:具有很強的抗數(shù)據(jù)端干擾能力,常用來組成寄存器、計數(shù)器等。

-

嵌入式系統(tǒng)

+關(guān)注

關(guān)注

41文章

3568瀏覽量

129234 -

接口

+關(guān)注

關(guān)注

33文章

8501瀏覽量

150839 -

ROM

+關(guān)注

關(guān)注

4文章

562瀏覽量

85676 -

計算機系統(tǒng)

+關(guān)注

關(guān)注

0文章

281瀏覽量

24089

發(fā)布評論請先 登錄

相關(guān)推薦

嵌入式系統(tǒng)知識和接口技術(shù)合集1

嵌入式系統(tǒng)知識和接口技術(shù)合集1

評論