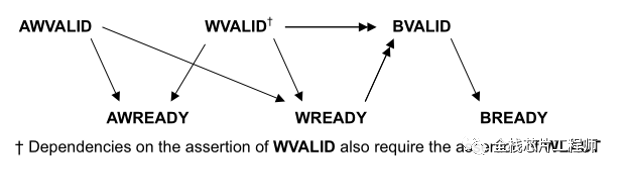

注意AXI3通道之間的寫依賴:

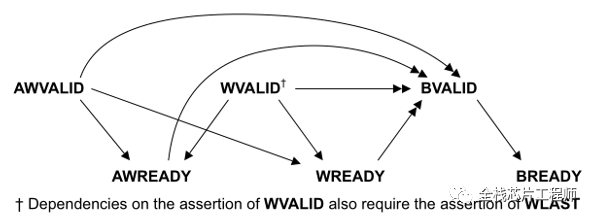

注意AXI4通道之間的寫依賴:

上面兩圖的區(qū)別是相比AXI3,AXI4協(xié)議需要確認(rèn)AWVALID、AWREADY握手完成才能回復(fù)BVALID。

審核編輯:劉清

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

原文標(biāo)題:考考你?:AXI3與AXI4寫響應(yīng)的依賴區(qū)別?

文章出處:【微信號(hào):全棧芯片工程師,微信公眾號(hào):全棧芯片工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

相關(guān)推薦

在 AXI 基礎(chǔ)第 2 講 一文中,曾提到賽靈思 Verification IP (AXI VIP) 可用作為 AXI 協(xié)議檢查工具。在本次第4講中,我們將來(lái)了解下如何使用它在

發(fā)表于 07-08 09:31

?2784次閱讀

。writeIssuingCapability:指明AXI4總線寫最大同時(shí)支持的指令個(gè)數(shù)。combinedIssuingCapability:其值應(yīng)不小于前兩者,用于在AXI4總線讀寫地址通道共用的場(chǎng)景

發(fā)表于 08-02 14:28

讀寫分離的設(shè)計(jì)在Axi4總線中,讀和寫通道是完全相互獨(dú)立,互不干擾。故而無(wú)論是在設(shè)計(jì)Decoder還是Arbiter時(shí),均可以采用讀寫分離的方式。如前文所述,SpinalHDL在基于Axi4總線

發(fā)表于 08-03 14:27

AXI-4 Memory Mapped也被稱之為AXI-4 Full,它是AXI4接口協(xié)議的基礎(chǔ),其他AXI4接口是該接口的變形。總體而言,AXI-

![的頭像]() 發(fā)表于

發(fā)表于 09-23 11:20

?6018次閱讀

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,但PS與PL之間的接口卻只支持前兩種,AXI-Stream只能在PL中實(shí)現(xiàn),不能直接和PS相連,必須通過(guò)

![的頭像]() 發(fā)表于

發(fā)表于 09-24 09:50

?5222次閱讀

新的賽靈思器件設(shè)計(jì)中不可或缺的一部分。充分了解其基礎(chǔ)知識(shí)對(duì)于賽靈思器件的設(shè)計(jì)和調(diào)試都很有幫助。 本篇博文將介紹賽靈思器件上的 AXI3/AXI4 的相關(guān)基礎(chǔ)知識(shí)。首先,我們將從一些通俗易懂的知識(shí)、理論

![的頭像]() 發(fā)表于

發(fā)表于 09-27 11:06

?6554次閱讀

ZYNQ中DMA與AXI4總線 為什么在ZYNQ中DMA和AXI聯(lián)系這么密切?通過(guò)上面的介紹我們知道ZYNQ中基本是以AXI總線完成相關(guān)功能的: 圖4?34連接 PS 和 PL 的

![的頭像]() 發(fā)表于

發(fā)表于 11-02 11:27

?4289次閱讀

本系列我想深入探尋 AXI4 總線。不過(guò)事情總是這樣,不能我說(shuō)想深入就深入。當(dāng)前我對(duì) AXI總線的理解尚談不上深入。但我希望通過(guò)一系列文章,讓讀者能和我一起深入探尋 AXI4。

發(fā)表于 03-17 21:40

?25次下載

AXI4 是一種高性能memory-mapped總線,AXI4-Lite是一只簡(jiǎn)單的、低通量的memory-mapped 總線,而 AXI4-Stream 可以傳輸高速數(shù)據(jù)流。從字面意思去理解

![的頭像]() 發(fā)表于

發(fā)表于 07-04 09:40

?8423次閱讀

AXI4 協(xié)議定義了五個(gè)不同的通道,如 AXI 通道中所述。所有這些通道共享基于 VALID 和 READY 信號(hào)的相同握手機(jī)制

![的頭像]() 發(fā)表于

發(fā)表于 05-08 11:37

?1188次閱讀

上文FPGA IP之AXI4協(xié)議1_協(xié)議構(gòu)架對(duì)協(xié)議框架進(jìn)行了說(shuō)明,本文對(duì)AXI4接口的信號(hào)進(jìn)行說(shuō)明。

![的頭像]() 發(fā)表于

發(fā)表于 05-24 15:05

?1434次閱讀

從 FPGA 應(yīng)用角度看看 AMBA 總線中的 AXI4 總線。

發(fā)表于 06-21 15:21

?2230次閱讀

本文主要集中在AMBA協(xié)議中的AXI4協(xié)議。之所以選擇AXI4作為講解,是因?yàn)檫@個(gè)協(xié)議在SoC、IC設(shè)計(jì)中應(yīng)用比較廣泛。

發(fā)表于 01-17 12:21

?2161次閱讀

AXI4和AXI3是高級(jí)擴(kuò)展接口(Advanced eXtensible Interface)的兩個(gè)不同版本,它們都是用于SoC(System on Chip)設(shè)計(jì)中的總線協(xié)議,用于處理器和其它外設(shè)之間的高速數(shù)據(jù)傳輸。

![的頭像]() 發(fā)表于

發(fā)表于 05-10 11:29

?6027次閱讀

AMBA AXI4(高級(jí)可擴(kuò)展接口 4)是 ARM 推出的第四代 AMBA 接口規(guī)范。AMD Vivado Design Suite 2014 和 ISE Design Suite 14 憑借半導(dǎo)體產(chǎn)業(yè)首個(gè)符合 AXI4 標(biāo)準(zhǔn)的

![的頭像]() 發(fā)表于

發(fā)表于 10-28 10:46

?155次閱讀

AXI3與AXI4寫響應(yīng)的依賴區(qū)別?

AXI3與AXI4寫響應(yīng)的依賴區(qū)別?

評(píng)論