門延遲類型

前兩節中所介紹的門級電路都是沒有延遲的,實際門級電路都是有延遲的。

Verilog 中允許用戶使用門延遲,來定義輸入到其輸出信號的傳輸延遲。

門延遲類型主要有以下 3 種。

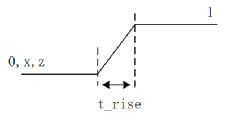

上升延遲

在門的輸入發生變化時,門的輸出從 0,x,z 變化為 1 所需要的轉變時間,稱為上升延遲。

下降延遲

在門的輸入發生變化時,門的輸出從 1,x,z 變化為 0 所需要的轉變時間,稱為下降延遲。

關斷延遲

關斷延遲是指門的輸出從 0,1,x 變化為高阻態 z 所需要的轉變時間。

門輸出從 0,1,z 變化到 x 所需要的轉變時間并沒有被明確的定義,但是它所需要的時間可以由其他延遲類型確定,即為以上 3 種延遲值中最小的那個延遲。

門延遲可以在門單元例化時定義,定義格式如下:

gate_type [delay] [instance_name] (signal_list) ;

其中,delay 的個數可以為 0 個、1 個、2 個或 3個 。

下表為不同延遲個數時,各種類型延遲的取值情況說明。

| 延遲類型 | 無延遲 | 1 個延遲 (d) | 2 個延遲 (d1, d2) | 3 個延遲 (d1, d2, d3) |

|---|---|---|---|---|

| 上升 | 0 | d | D1 | D1 |

| 下降 | 0 | d | D2 | D2 |

| 關斷 | 0 | d | 最小(D1, D2) | D3 |

| to_x | 0 | d | 最小(D1, D2) | 最小(D1, D2, D3) |

如果用戶沒有指定延遲值,則默認延遲為 0 。

如果用戶指定了 1 個延遲值,則所有類型的延遲值大小均為此值。

如果用戶指定了 2 個延遲值,則他們分別代表上升延遲和下降延遲,關斷和“to_x”延遲均為這 2 種延遲值中最小的那個。

如果用戶指定了 3 個延遲值,則他們分別代表上升延遲、下降延遲和關斷延遲,“to_x”延遲為這 3 種延遲值中最小的那個。

帶有延遲值的門級單元例化如下:

//rise, fall and turn-off delay are all 1

and #(1) (OUT1, IN1, IN2) ;

//rise delay = 2.1, fall dalay = 2, trun-off delay = 2

or #(2.1, 2) (OUT2, IN1, IN2) ;

//rise delay = 2, fall dalay = 1, trun-off delay = 1.3

bufif0 #(2, 1, 1.3) (OUT3, IN1, CTRL) ;

需要說明的是,多輸入門(如與門)和多輸出門(如非門)最多只能定義 2 個延遲,因為輸出不會是 z 。

三態門和單向開關單路(MOS 管、CMOS 管等)可以定義 3 個延遲。

上下拉門級電路不會有任何的延遲,因為它表示的是一種硬件屬性,上下拉狀態不會發生變化,且沒有輸出值。

雙向開關(tran)在傳輸信號時沒有延遲,不允許添加延遲定義。

帶有控制端的雙向開關(tranif1, tranif0)在開關切換的時候,會有開或關的延遲,可以給此類雙向開關指定 0 個、1 個或 2 個的延遲,例如:

//turn-on and turn-off delay are all 1

tranif0 #(1) (inout1, inout2, CTRL);

//turn-on delay = 1, turn-off delay = 1.2

tranif1 #(1, 1.2) (inout3, inout4, CTRL);

最小/典型/最大延遲

由于集成電路制造工藝的差異,實際電路中器件的延遲總會在一定范圍內波動。 Verilog 中,用戶不僅可以指定 3 種類型的門延遲,還可以對每種類型的門延遲指定其最小值、典型值和最大值。 在編譯或仿真階段,來選擇使用哪一種延遲值,為更切實際的仿真提供了支持。

最小值:門單元所具有的最小延遲。

典型值:門單元所具有的典型延遲。

最大值:門單元所具有的最大延遲。

下面通過例化實例,來說明最小、典型、最大延遲的用法。

//所有的延遲類型:最小延遲 1, 典型延遲 2, 最大延遲 3

and #(1:2:3) (OUT1, IN1, IN2) ;

//上升延遲:最小延遲 1, 典型延遲 2, 最大延遲 3

//下降延遲:最小延遲 3, 典型延遲 4, 最大延遲 5

//關斷延遲:最小延遲 min(1,3), 典型延遲 min(2,4), 最大延遲 min(3,5)

or #(1:2:3, 3:4:5) (OUT2, IN1, IN2) ;

//上升延遲:最小延遲 1, 典型延遲 2, 最大延遲 3

//下降延遲:最小延遲 3, 典型延遲 4, 最大延遲 5

//關斷延遲:最小延遲 2, 典型延遲 3, 最大延遲 4

bufif0 #(1:2:3, 3:4:5, 2:3:4) (OUT3, IN1, CTRL) ;

D 觸發器

下面從門級建模的角度,對 D 觸發器進行設計。

SR 觸發器

SR 觸發器結構圖及真值表如下所示。

1> 當 S 為低電平,G1 輸出端 Q 為高電平,并反饋到 G2 輸入端。 如果此時 R 為高電平,則 G2 輸出端 Q' 為低電平。

2> R 為低電平 S 為高電平時,分析同理。

3> S 與 R 均為高電平時,如果 Q = 1 (Q' = 0) , 則 Q 反饋到 G2 輸入端后輸出 Q' 仍然為 0, Q' 反饋到 G1 輸入端后輸出 Q 仍然是 1,呈現穩態。 如果 Q =0 (Q' = 1) 同理,Q 與 Q' 的值仍然會保持不變。 即 S 與 R 均為高電平時該電路具有保持的功能。

4> 如果 S 與 R 均為低電平,則輸出 Q 與 Q' 均為高電平,不再成互補的關系。 所以此種情況是禁止出現的。

SR 鎖存器

在基本的 SR 觸發器前面增加 2 個與非門,可構成帶有控制端 SR 鎖存器。

SR 鎖存器及其真值表如下所示。

當 EN=0 時,G3、G4 截止,SR 鎖存器保持輸出狀態不變。

當 EN=1 時,與基本的 SR 觸發器工作原理完全相同。

D 鎖存器

基本的 SR 觸發器輸入端不能同時為 0, 帶有控制端的 SR 鎖存器輸入端不能同時為 1,否則會導致輸出端 Q 與 Q' 的非互補性矛盾。

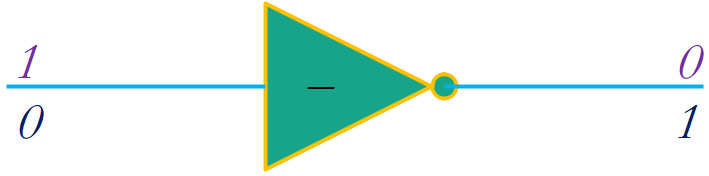

為消除此種不允許的狀態,在帶有控制端的 SR 鎖存器結構中加入取反模塊,保證 2 個輸入端均為相反邏輯,則形成了 D 鎖存器。

其結構圖和真值表如下所示。

1> 當 EN=1 時,輸出狀態隨輸入狀態的改變而改變。

2> 當 EN=0 時,輸出狀態保持不變。

D 鎖存器是一種電平觸發。

如果在 EN=1 的有效時間內,D 端信號發生多次翻轉,則輸出端 Q 也會發生多次翻轉。 這降低了電路的抗干擾能力,不是實際所需求的安全電路。

為提高觸發器的可靠性,增強電路抗干擾能力,發明了在特定時刻鎖存信號的 D 觸發器。

D 觸發器

將兩個 D 鎖存器進行級聯,時鐘取反,便構成了一種簡單的 D 觸發器,又名 Flip-flop。

其結構圖和真值表如下所示。

第一級 D 鎖存器又稱為主鎖存器,在 CP 為低電平時鎖存。 第二級 D 鎖存器又稱為從鎖存器,時鐘較主鎖存器相反,在 CP 為高電平時鎖存。

1> CP=1 時,主鎖存器輸出端 Qm 會和 D 端信號的變化保持一致,而從鎖存器處于保持狀態,輸出 Qs 保持不變。

2> CP由高電平變為低電平時,主鎖存器鎖存當前 D 的狀態,傳遞到輸出端 Qm 并保持不變。 而從鎖存器輸出端 Qs 會和 Qm 的變化保持一致。 此時處于鎖存狀態下的主鎖存器輸出端 Qm 會保持不變,所以 D 觸發器輸出端 Qs 端得到新的 Qm 值后, 也會保持不變。

綜上所述,D 觸發器輸出端 Qs 只會在時鐘 CP 下降沿對 D 端進行信號的鎖存,其余時間輸出端信號具有保持的功能。

將雙級 D 鎖存器展開為門級結構,如下圖所示。

對 D 觸發進行門級建模,并加入門級延時,verilog 模型如下:

module D_TRI(

input D, CP,

output Q, QR);

parameter RISE_TIME = 0.11 ;

parameter FALL_TIME = 0.07 ;

//part1, not gate

wire CPN, DN ;

not #(RISE_TIME, FALL_TIME) (CPN, CP);

not #(RISE_TIME, FALL_TIME) (DN, D);

//part2, master trigger

wire G3O, G4O ;

nand #(RISE_TIME, FALL_TIME) (G3O, D, CP);

nand #(RISE_TIME, FALL_TIME) (G4O, DN, CP);

wire #(RISE_TIME, FALL_TIME) G1O, G2O ;

nand #(RISE_TIME, FALL_TIME) (G1O, G3O, G2O);

nand #(RISE_TIME, FALL_TIME) (G2O, G4O, G1O);

//part3, slave trigger

wire G7O, G8O ;

nand #(RISE_TIME, FALL_TIME) (G7O, G1O, CPN);

nand #(RISE_TIME, FALL_TIME) (G8O, G2O, CPN);

wire G5O, G6O ;

nand #(RISE_TIME, FALL_TIME) (G5O, G7O, G6O);

nand #(RISE_TIME, FALL_TIME) (G6O, G8O, G5O);

assign Q = G5O ;

assign QR = G6O ;

endmodule

testbench 編寫如下:

`timescale 1ns/1ps

module test ;

reg D, CP = 0 ;

wire Q, QR ;

always #5 CP = ~CP ;

initial begin

D = 0 ;

#12 D = 1 ;

#10 D = 0 ;

#14 D = 1 ;

#3 D = 0 ;

#18 D = 0 ;

end

D_TRI u_d_trigger(

.D (D),

.CP (CP),

.Q (Q),

.QR (QR));

initial begin

forever begin

#100;

//$display("---gyc---%d", $time);

if ($time >= 1000) begin

$finish ;

end

end

end

endmodule

仿真結果如下。

由圖可知,Q/QR 信號均在時鐘 CP 下降沿采集到了 D 端信號,并在單周期內保持不變,且輸出有延遲。

對 cap3 時刻進行放大,對延時進行追蹤,如下圖所示。

CP 端到 CPN 端有上升延遲,時間為 110ps;

CPN 端到 G8O 端有下降延遲,時間為 70ps;

G8O 端到 G6O 端有上升延遲,時間為 110ps;

G6O 端到 Q 端有下降延遲,時間為 70ps;

共 360ps,符合設置的門延遲。

-

仿真

+關注

關注

50文章

4048瀏覽量

133431 -

信號

+關注

關注

11文章

2781瀏覽量

76648 -

Verilog

+關注

關注

28文章

1345瀏覽量

109995 -

時鐘

+關注

關注

10文章

1721瀏覽量

131378 -

門級電路

+關注

關注

0文章

15瀏覽量

1956

發布評論請先 登錄

相關推薦

PlanAhead報告時間:路徑延遲類型代表什么?

如何檢查AND門的邏輯門?

智能鎖廠家諾托告訴你不同類型的門如何搭配智能鎖

Xilinx Vivado I/O延遲約束介紹

Verilog HDL提供了哪兩種類型的顯式時序控制

SystemVerilog/Verilog中的各種延遲模型

基本邏輯門的類型及其用途

門延遲類型介紹

門延遲類型介紹

評論