門級建模,是使用基本的邏輯單元,例如與門,與非門等,進行更低級抽象層次上的設(shè)計。 與行為級建模相比,門級建模更注重硬件的實現(xiàn)方法,即通過連接一些基本門電路去實現(xiàn)多種邏輯功能。 雖然行為級建模最后也會被綜合成基本的門級電路網(wǎng)絡(luò),但對于復(fù)雜的設(shè)計來說,行為級建模的效率遠遠高于門級建模。 所以目前 Verilog 大多數(shù)用于描述數(shù)字設(shè)計的行為級層次(RTL),一般只注重設(shè)計實現(xiàn)的算法或流程,而不用特別關(guān)心具體的硬件實現(xiàn)方式。

有些設(shè)計,例如門控時鐘,就需要使用基本門單元,來增加電路的可控性與可靠性。

多輸入門

多輸入門只有單個輸出,有單個或多個輸入端。 Verilog 內(nèi)置多輸入門如下:

and(與門) nand(與非門) or(或門) nor(或非門) xor(異或門) xnor(同或門)

使用基本的邏輯門單元去實現(xiàn)一些簡單的邏輯功能時,使用模塊例化的方式即可。

門級單元第一個端口是輸出,后面端口是輸入,例化調(diào)用時需要注意。

門級單元實例調(diào)用的時候,也可以不指定實例的名字,這為代碼編寫提供了方便。

當(dāng)輸入端口超過 2 個時,只需將輸入信號在端口列表中繼續(xù)排列即可,Verilog 可自動識別。

//basic gate instantiation

and a1 (OUTX, IN1, IN2) ;

nand na1 (OUTX1, IN1, IN2) ;

or or1 (OUTY, IN1, IN2) ;

nor nor1 (OUTY1, IN1, IN2) ;

//3 input

xor xor1 (OUTZ, IN1, IN2, IN3) ;

//no instantiation name

xnor (OUTZ1, IN1, IN2) ;

多輸入門的真值表如下,注意輸出不會出現(xiàn)“Z”。

| 和 | 0 | 1 | x | 跟 | 南德 | 0 | 1 | x | 跟 | |

|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | |

| 1 | 0 | 1 | x | x | 1 | 1 | 0 | x | x | |

| x | 0 | x | x | x | x | 1 | x | x | x | |

| 跟 | 0 | x | x | x | 跟 | 1 | x | x | x |

| 或 | 0 | 1 | x | 跟 | 也不 | 0 | 1 | x | 跟 | |

|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 1 | x | x | 0 | 1 | 0 | x | x | |

| 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | |

| x | x | 1 | x | x | x | x | 0 | x | x | |

| 跟 | x | 1 | x | x | 跟 | x | 0 | x | x |

| 異或 | 0 | 1 | x | 跟 | 出去 | 0 | 1 | x | 跟 | |

|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 1 | x | x | 0 | 1 | 0 | x | x | |

| 1 | 1 | 0 | x | x | 1 | 0 | 1 | x | x | |

| x | x | x | x | x | x | x | x | x | x | |

| 跟 | x | x | x | x | 跟 | x | x | x | x |

多輸出門

多輸出門只有單個輸入,有單個或多個輸出端,又可稱之為 buffer,起緩沖、延時作用。

內(nèi)置多輸入門如下:

buf(緩沖器) not(非門)

和多輸入門類似,可以使用模塊例化的方式對多輸出門進行調(diào)用。

門級單元第一個端口是輸出,最后一個端口是輸入。 當(dāng)輸出端口超過 1 個時,需將輸出信號在最后一個輸入端口前排列。

例化時也可以不指定實例的名字。

//buf

buf buf1 (OUTX2, IN1) ;

//2 output

buf buf2 (OUTY2, OUTY3, IN2) ;

//no instantiation name

not (OUTZ3, IN3) ;

多輸出門的真值表如下,注意輸出不會出現(xiàn)“Z”。

| 布夫 | 0 | 1 | x | 跟 | 不 | 0 | 1 | x | 跟 | |

|---|---|---|---|---|---|---|---|---|---|---|

| 輸出 | 0 | 1 | x | x | 輸出 | 1 | 0 | x | x |

三態(tài)門

Verilog 中還提供了 4 個帶有控制端的 buffer 門單元,稱為三態(tài)門。 只有當(dāng)控制信號有效時,數(shù)據(jù)才能正常傳遞,否則輸出為高阻抗?fàn)顟B(tài)“Z”。

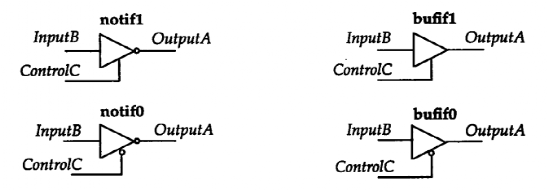

4 個三態(tài)門名稱及符號如下:

例化時,三態(tài)門第一個端口為輸出端,第二個端口為數(shù)據(jù)輸入端,第三個端口為控制輸入端。 例化時信號排列順序要一致。

三態(tài)門不支持輸出端口超過 1 個,但例化時可以不指定實例的名字。

//tri

bufif1 buf1 (OUTX, IN1, CTRL1) ;

bufif0 buf2 (OUTY, IN1, CTRL2) ;

notif1 buf3 (OUTZ, IN1, CTRL3) ;

//no instantiation name

notif0 (OUTX1, IN1, CTRL4) ;

三態(tài)門的真值表如下。

表中有些為可選項,例如,1/z 表明,根據(jù)輸入端和控制端的信號強度,輸出端既可能為 1,也可能為 “z”。

| 布菲夫1 | 控制端 | 布菲夫0 | 控制端 | |

|---|---|---|---|---|

| 0 | 1 | x | 跟 | 0 |

| 0 | 跟 | 0 | 3/9 | 3/9 |

| 1 | 跟 | 1 | 3/8 | 3/8 |

| x | 跟 | x | x | x |

| 跟 | 跟 | x | x | x |

| 通知1 | 控制端 | 通知0 | 控制端 | |

|---|---|---|---|---|

| 0 | 1 | x | 跟 | 0 |

| 0 | 跟 | 1 | 3/8 | 3/8 |

| 1 | 跟 | 0 | 3/9 | 3/9 |

| x | 跟 | x | x | x |

| 跟 | 跟 | x | x | x |

利用三態(tài)門實現(xiàn)可配置輸入輸出 PAD 功能的例程,可參見該教程《1.2 開關(guān)級建模》一節(jié)。

利用三態(tài)門實現(xiàn)可配置上下拉 PAD 功能的例程,可參見《Verilog 教程》的《5.1 Verilog 模塊與端口》一章。

上下拉電阻

上拉是將不確定的信號通過一個電阻鉗制在一個高電平。

下拉是將不確定的信號通過一個電阻與地相連,固定在低電平。

模塊端口的上拉或下拉電阻,具有限流、提高驅(qū)動能力、防靜電等作用,可以有效保護電路。

當(dāng)信號方向為輸入且沒有輸入信號(高阻態(tài))時,上拉會將該信號的邏輯值置為 “1”,下拉會將該信號的邏輯值置為 “0”。

Verilog 提供了為信號設(shè)置上、下拉電阻的邏輯門單元,多用于模塊端口信號。

此類門單元沒有輸入,只有輸出。 關(guān)鍵字如下:

pullup(設(shè)置上拉) pulldown(設(shè)置下拉)

例化調(diào)用時,只需填寫需要設(shè)置上下拉電阻的信號即可。

實例的名字也可以不指定。

pullup p1 (IN1);

pulldown (OUTX);

此處設(shè)置上下拉電阻后就不能再更改。 在《Verilog 教程》的《5.1 Verilog 模塊與端口》一章中,利用三態(tài)門 buffer 實現(xiàn)了可配置上下拉 PAD 功能的實例,歡迎參考。

4 選 1 多路選擇器

下面對比四選一選擇的實現(xiàn)方式,來說明門級建模較行為級建模的繁瑣性。

輸入為 A、B、C、D,輸出為 F,選擇信號為 SEL1、SEL0,則 4 路選擇器的表達式為:

門級建模如下:

module mux4to1_gate(

input A, B, C, D ,

input S0, S1,

output F );

//reversing

wire S0R, S1R ;

not (S0R, S0) ;

not (S1R, S1) ;

//logic and

wire AAND, BAND, CAND, DAND ;

and (AAND, A, S1R, S0R);

and (BAND, B, S1R, S0);

and (CAND, C, S1, S0R);

and (DAND, D, S1, S0);

//logic or

or (F, AAND, BAND, CAND, DAND) ;

endmodule

行為級建模如下:

module mux4to1_behavior(

input A, B, C, D ,

input S0, S1,

output F );

assign F = {S1, S0} == 2'b00 ? A :

{S1, S0} == 2'b01 ? B :

{S1, S0} == 2'b10 ? C :

{S1, S0} == 2'b11 ? D : 0 ;

endmodule

雖然行為級建模綜合后的結(jié)果可能與門級建模一致,但是在設(shè)計時,顯然行為級建模有更好的可讀性、簡潔性。

-

Verilog

+關(guān)注

關(guān)注

28文章

1343瀏覽量

109986 -

三態(tài)門

+關(guān)注

關(guān)注

1文章

34瀏覽量

18798 -

門控時鐘

+關(guān)注

關(guān)注

0文章

27瀏覽量

8943 -

門級電路

+關(guān)注

關(guān)注

0文章

15瀏覽量

1955 -

邏輯單元

+關(guān)注

關(guān)注

0文章

25瀏覽量

5115

發(fā)布評論請先 登錄

相關(guān)推薦

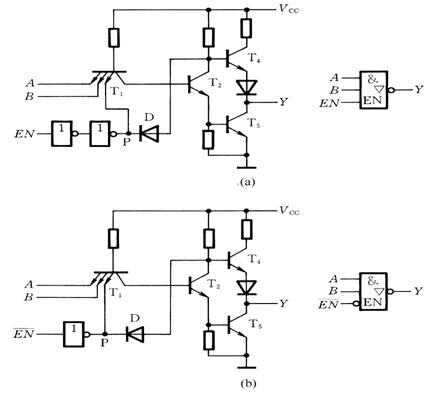

高阻態(tài)與三態(tài)門的電路原理分析

【夢翼師兄今日分享】 三態(tài)門程序設(shè)計講解

集電極開路門和三態(tài)輸出門的應(yīng)用

什么是三態(tài)門? 三態(tài)邏輯與非門電路以及三態(tài)門電路

多輸入多輸出天線系統(tǒng)MIMO分析

三態(tài)門有哪三態(tài)_三態(tài)門有什么特點

多輸入門、多輸出門和三態(tài)門詳解

多輸入門、多輸出門和三態(tài)門詳解

評論