本教程經常有提及綜合這個詞語。 或者說有些邏輯不能綜合成實際電路,或者說有些邏輯設計綜合后的電路會有一些安全隱患。 本章就簡單介紹下邏輯綜合的相關知識,僅從理論層次和普遍認知的角度來闡述。 待那個懵懂求知少年變成中年禿頂大叔,再來介紹邏輯綜合的具體實踐。 好像也沒有多少時日了(手動狗頭)。

基本概念

綜合,就是在標準單元庫和特定的設計約束基礎上,把數字設計的高層次描述轉換為優化的門級網表的過程。 標準單元庫對應工藝庫,可以包含簡單的與門、非門等基本邏輯門單元,也可以包含特殊的宏單元,例如乘法器、特殊的時鐘觸發器等。 設計約束一般包括時序、負載、面積、功耗等方面的約束。

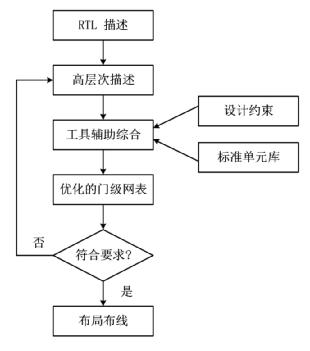

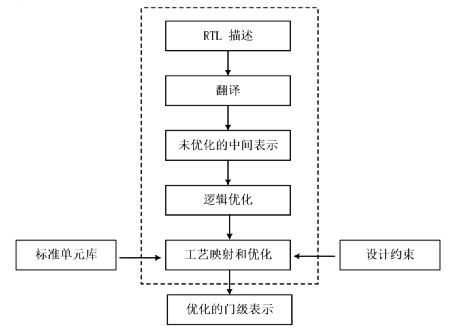

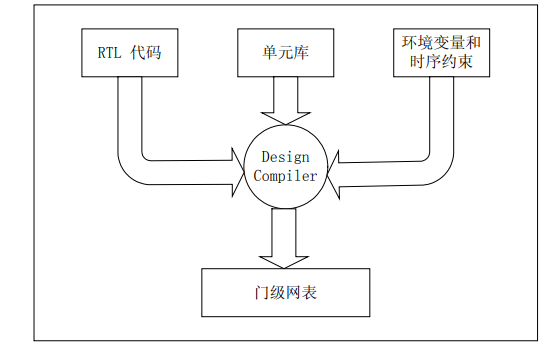

無論是數字芯片設計,還是 FPGA 開發,現在綜合過程基本都是借用計算機輔助邏輯綜合工具,自動的將高層次描述轉換為邏輯門電路。 設計人員可以將精力集中在系統結構方案、高層次描述、設計約束和標準工藝庫等方面,而不用去關心高層次的描述怎么轉換為門級電路。 綜合工具在內部反復進行邏輯轉換、優化,最終生成最優的門級電路。 該過程如下所示。

結構解釋

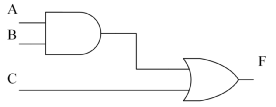

簡單的賦值語句通常被綜合為基本的邏輯門單元

assign F = (A & B) | C ;

上述代碼通常會被綜合為如下門級電路:

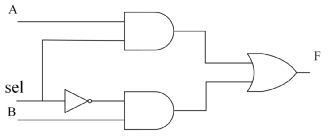

條件語句通常被綜合為選擇器

assign F = sel ? A : B ;

上述代碼通常會被綜合為如下門級電路:

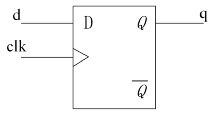

always 塊中時鐘觸發的賦值語句通常被綜合為觸發器

always @(posedge clk) begin

q <= d ;

end

上述代碼通常會被綜合為如下電路:

再復雜的設計,綜合之后,都會被轉換為由各種單元庫原件組成的門級網表。 總之,邏輯綜合可以狹隘的理解為,將 Verilog 設計轉換為用優化的基本邏輯門單元、特殊的宏單元表示的過程。

綜合流程

從高層次 RTL 描述到門級網表的詳細綜合過程如下圖所示。

RTL 描述

用硬件描述語言(例如 Verilog)設計數字電路,并進行仿真保證邏輯功能的正確性。

翻譯

RTL 描述會被綜合工具轉換為一個未經優化的中間表示。 該過程讀入 Verilog 描述的基本原語和操作,不考慮面積、時序、功耗等設計約束,僅完成簡單的內部資源分配。

未優化的中間表示

翻譯過程中產生的中間表示,數據格式由綜合工具內部識別,用戶無法也無需了解。

邏輯優化

優化設計邏輯,刪除冗余邏輯。 該過程往往會將 RTL 設計的一些變量刪除,或重新命名,邏輯實現過程往往也會改變,以達到邏輯的最優化實現。 該過程會產生優化的內部表示。

工藝映射和優化

此步驟之前,設計的描述過程是獨立于目標工藝的。 該步驟中,綜合工具將使用工藝庫(標準單元庫)中提供的邏輯單元,實現設計的內部表示。 即設計會被映射到目標工藝。 實現過程中,還必須滿足時序、面積和功耗的約束,執行一些局部的優化。

標準單元庫

如之前所述,標準單元庫對應工藝庫,可以包含簡單的與門、非門等基本邏輯門單元,也可以包含特殊的宏單元,例如乘法器、特殊的觸發器等。

為了更好的映射與優化,每個邏輯單元,應當包含以下信息:

1> 功能描述

2> 版圖面積

3> 時序信息

4> 功耗信息

設計約束

設計約束一般包括時序、面積、功耗等方面的約束。 三者之間往往存在制約關系。 為了優化時序,可能需要增加硬件資源,導致電路面積增大,功耗增加。 為了產生規模更小的電路,又必須在電路速度上進行妥協。 數字電路設計時往往要綜合各種因素進行取舍。

優化的門級表示

工藝映射與優化完成后,最終會生成由目標工藝庫所描述的優化后的門級網表。 如果該網表滿足各種約束要求,則會被制作成最終的版圖。 否則還需要修改設計約束或優化 RTL 描述,以獲得滿足約束要求的門級網表結果。 這個過程是反復的,直至最終網表滿足要求。

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602019 -

時鐘

+關注

關注

10文章

1721瀏覽量

131378 -

觸發器

+關注

關注

14文章

1996瀏覽量

61057 -

邏輯設計

+關注

關注

1文章

41瀏覽量

11569 -

門級電路

+關注

關注

0文章

15瀏覽量

1956

發布評論請先 登錄

相關推薦

淺談IC設計中邏輯綜合

DC邏輯綜合

FPGA中不可綜合語句 相關知識

ASIC邏輯綜合及Synopsys Design Compiler 的使用資料說明

邏輯綜合的相關知識

邏輯綜合的相關知識

評論