4.1 系統核心部分——閃電存儲型器件AT89S52

4.1.1 AT89S52具有下列主要性能:

8KB可改編程序Flash存儲器(可經受1000次的寫入/擦除周期)

全靜態工作:0Hz~24MHz

三級程序存儲器保密

128×8字節內部RAM

32條可編程I/O線

2個16位定時器/計數器

6個中斷源

可編程串行通道

片內時鐘振蕩器

4.1.2 AT89S52的引腳及功能

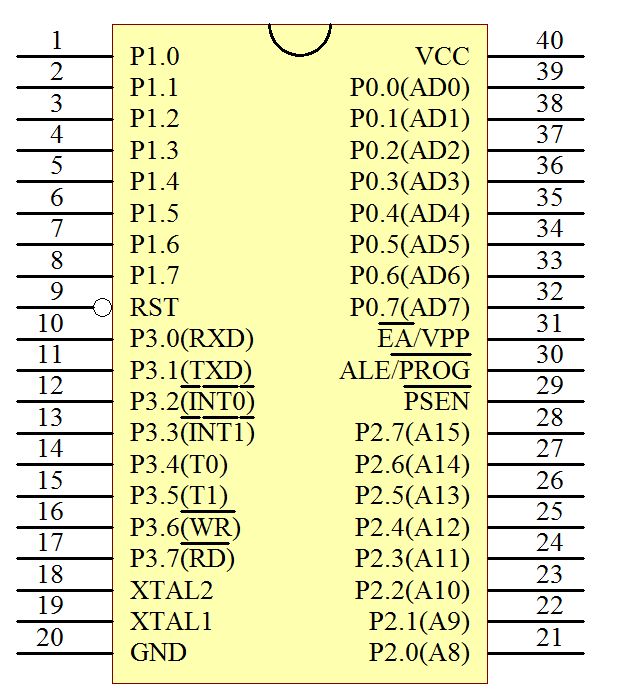

AT89S52單片機的管腳說明如圖4-2所示。

(圖4-2 AT89S52的管腳)

(1) 主要電源引腳

①VCC 電源端

②GND 接地端

(2) 外接晶體引腳XTAL1和XTAL2

①XTAL1 接外部晶體的一個引腳。在單片機內部,它是構成片內振蕩器的反相放大器的輸入端。當采用外部振蕩器時,該引腳接收振蕩器的信號,既把此信號直接接到內部時鐘發生器的輸入端。

②XTAL2 接外部晶體的另一個引腳。在單片機內部,它是上述振蕩器的反相放大器的輸出端。采用外部振蕩器時,此引腳應懸浮不連接。

(3) 控制或與其它電源復用引腳RST、ALE//PROG、/PSEN和/EA/VPP

①RST 復位輸入端。 當振蕩器運行時,在該引腳上出現兩個機器周期的高電平將使單片機復位。

②ALE//PROG 當訪問外部存儲器時,ALE(地址鎖存允許)的輸出用于鎖存地址的低位字節。即使不訪問外部存儲器,ALE端仍以不變的頻率(此頻率為振蕩器頻率的1/6)周期性地出現正脈沖信號。因此,它可用作對外輸出的時鐘,或用于定時目的。然而要注意的是:每當訪問外部數據存儲器時,將跳過一個ALE脈沖。在對Flash存儲器編程期間,該引腳還用于輸入編程脈沖(/PROG)。

③/PSEN 程序存儲允許(/PSEN)輸出是外部程序存儲器的讀選通信號。當AT89S52/LV52由外部程序存儲器取指令(或常數)時,每個機器周期兩次/PSEN有效(既輸出2個脈沖)。但在此期間內,每當訪問外部數據存儲器時,這兩次有效的/PSEN信號將不出現。

④/EA/VPP 外部訪問允許端。要使CPU只訪問外部程序存儲器(地址為0000H~FFFFH),則/EA端必須保持低電平(接到GND端)。當/EA端保持高電平(接VSS端)時,CPU則執行內部程序存儲器中的程序。

(4)輸入/輸出引腳 P0.0~P0.7、P1.0~P1.7、P2.0~P2.7 和P3.0~P3.7

①P0端口(P0.0~ P0.7) P0是一個8位漏極開路型雙向I/O端口。作為輸出口用時,每位能以吸收電流的方式驅動8個TTL輸入,對端口寫1時,又可作高阻抗輸入端用。

②P1端口(P1.0~ P1.7) P1是一個帶有內部上拉電阻的8位雙向I/O端口。P1的輸出緩沖器可驅動(吸收或輸出電流方式)4個TTL輸入。對端口寫1時,通過內部的上拉電阻把端口拉到高電位,這時可用作輸入口。作輸入口時,因為有內部的上拉電阻,那些被外部信號拉低的引腳會輸出一個電流。

③P2端口 (P2.0~P2.7) P2是一個帶有內部上拉電阻的8位雙向I/O端口。P2的輸出緩沖器可驅動(吸收或輸出電流方式)4個TTL輸入。對端口寫1時,通過內部的上拉電阻把端口拉到高電位,這時可用作輸入口。P2作輸入口使用時,因為有內部的上拉電阻,那些被外部信號拉低的引腳會輸出一個電流。 ④P3端口(P3.0~P3.7) P3口管腳是8個帶內部上拉電阻的雙向I/O口,可接收輸出4個TTL門電流。當P3口寫入“1”后,它們被內部上拉為高電平,并用作輸入。作為輸入,由于外部下拉為低電平,P3口將輸出電流,這是由于上拉的緣故。

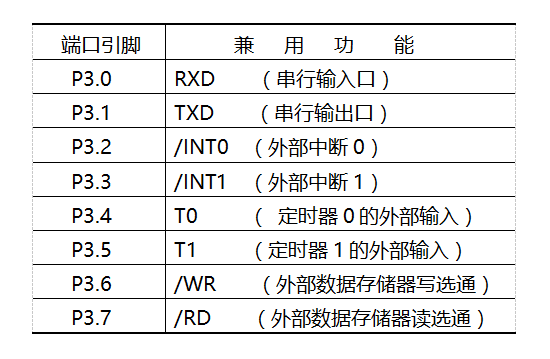

P3口也可作為AT89S52的一些特殊功能,這些特殊功能見表4-1。

(表4-1 P3端口的特殊功能)

-

單片機

+關注

關注

6032文章

44514瀏覽量

632975 -

振蕩器

+關注

關注

28文章

3813瀏覽量

138870 -

存儲器

+關注

關注

38文章

7452瀏覽量

163599 -

計數器

+關注

關注

32文章

2253瀏覽量

94351 -

電子萬年歷

+關注

關注

3文章

38瀏覽量

15922

發布評論請先 登錄

相關推薦

電子萬年歷設計方案(2)

電子萬年歷設計方案(2)

評論