4.3 存儲電路

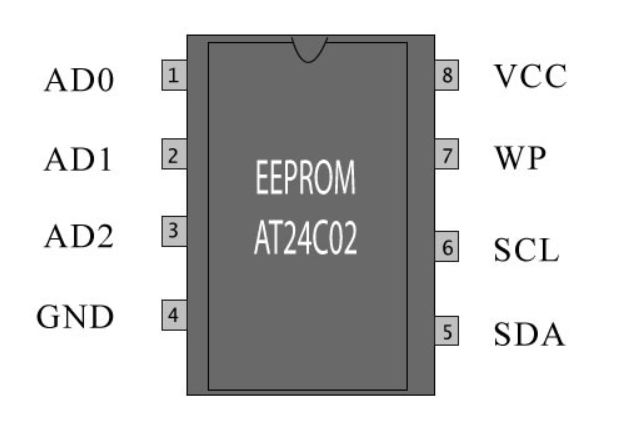

4.3.1 AT24C02管腳介紹

AT24C02是美國ATMEL公司的低功耗CMOS串行EEPROM,它是內含256×8位存儲空間,具有工作電壓寬(2.5~5.5V)、擦寫次數多(大于10000次)、寫入速度快(小于10ms)等特點。

AT24C02的1、2、3腳是三條地址線,用于確定芯片的硬件地址。第8腳和第4腳分別為正、負電源。第5腳SDA為串行數據輸入/輸出,數據通過這條雙向I2C總線串行傳送。第6腳SCL為串行時鐘輸入線。SDA和SCL都需要和正電源間各接一個4.7K的電阻上拉。

I2C總線是一種用于I2C器件之間連接的二線制總線。它通過SDA(串行數據線)及SCL(串行時鐘線)兩根線在連到總線上的器件之間傳送信息,并根據地址識別每個器件:不管是單片機、存儲器、LCD驅動器還是鍵盤接口。

4.3.2 AT24C02的特性

(1) I2C總線的基本結構

采用I2C總線標準的單片機或I2C器件,其內部不僅有I2C接口電路,而且將內部各單元電路按功能劃分為若干相對獨立的模塊,通過軟件尋址實現片選,減少了器件片選線的連接。CPU不僅能通過指令將某個功能單元電路掛靠或摘離總線,還可對該單元的工作狀況進行檢測,從而實現對硬件系統的既簡單又靈活的擴展與控制。

(2) 雙向傳輸的接口特性

傳統的單片機串行接口的發送和接收一般都各用一條線,而I2C總線則根據器件的功能通過軟件程序使其可工作于發送或接收方式。當某個器件向總線上發送信息時,它就是發送器(也叫主器件),而當其從總線上接收信息時,又成為接收器(也叫從器件)。主器件用于啟動總線上傳送數據并產生時鐘以開放傳送的器件,此時任何被尋址的器件均被認為是從器件。I2C總線的控制完全由掛接在總線上的主器件送出的地址和數據決定。

總線上主和從(即發送和接收)的關系不是一成不變的,而是取決于此時數據傳送的方向。SDA和SCL均為雙向I/O線,通過上拉電阻接正電源。當總線空閑時,兩根線都是高電平。連接總線的器件的輸出級必須是集電極或漏極開路,以具有線“與”功能。I2C總線的數據傳送速率在標準工作方式下為100kbit/s,在快速方式下,最高傳送速率可達400kbit/s。

(3) I2C總線上的時鐘信號

在I2C總線上傳送信息時的時鐘同步信號是由掛接在SCL時鐘線上的所有器件的邏輯“與”完成的。SCL線上由高電平到低電平的跳變將影響到這些器件,一旦某個器件的時鐘信號下跳為低電平,將使SCL線一直保持低電平,使SCL線上的所有器件開始低電平期。此時,低電平周期短的器件的時鐘由低至高的跳變并不能影響SCL線的狀態,于是這些器件將進入高電平等待的狀態。

當所有器件的時鐘信號都上跳為高電平時,低電平期結束,SCL線被釋放返回高電平,即所有的器件都同時開始它們的高電平期。其后,第一個結束高電平期的器件又將SCL線拉成低電平。這樣就在SCL線上產生一個同步時鐘。可見,時鐘低電平時間由時鐘低電平期最長的器件確定,而時鐘高電平時間由時鐘高電平期最短的器件確定。

(4) 數據的傳送

在數據傳送過程中,必須確認數據傳送的開始和結束。當時鐘線SCL為高電平時,數據線SDA由高電平跳變為低電平定義為“開始”信號;當SCL線為高電平時,SDA線發生低電平到高電平的跳變為“結束”信號。開始和結束信號都是由主器件產生。在開始信號以后,總線即被認為處于忙狀態;在結束信號以后的一段時間內,總線被認為是空閑的。

I2C總線的數據傳送格式是:在I2C總線開始信號后,送出的第一個字節數據是用來選擇從器件地址的,其中前7位為地址碼,第8位為方向位(R/W)。方向位為“0”表示發送,即主器件把信息寫到所選擇的從器件;方向位為“1”表示主器件將從從器件讀信息。開始信號后,系統中的各個器件將自己的地址和主器件送到總線上的地址進行比較,如果與主器件發送到總線上的地址一致,則該器件即為被主器件尋址的器件,其接收信息還是發送信息則由第8位(R/W)確定。

在I2C總線上每次傳送的數據字節數不限,但每一個字節必須為8位,而且每個傳送的字節后面必須跟一個認可位(第9位),也叫應答位(ACK)。每次都是先傳最高位,通常從器件在接收到每個字節后都會做出響應,即釋放SCL線返回高電平,準備接收下一個數據字節,主器件可繼續傳送。如果從器件正在處理一個實時事件而不能接收數據時(例如正在處理一個內部中斷,在這個中斷處理完之前就不能接收I2C總線上的數據字節),可以使時鐘SCL線保持低電平,從器件必須使SDA保持高電平,此時主器件產生1個結束信號,使傳送異常結束,迫使主器件處于等待狀態。當從器件處理完畢時將釋放SCL線,主器件繼續傳送。

當主器件發送完一個字節的數據后,接著發出對應于SCL線上的一個時鐘(ACK)認可位,在此時鐘內主器件釋放SDA線,一個字節傳送結束,而從器件的響應信號將SDA線拉成低電平,使SDA在該時鐘的高電平期間為穩定的低電平。從器件的響應信號結束后,SDA線返回高電平,進入下一個傳送周期。

(5) 總線競爭的仲裁

總線上可能掛接有多個器件,有時會發生兩個或多個主器件同時想占用總線的情況。例如,多單片機系統中,可能在某一時刻有兩個單片機要同時向總線發送數據,這種情況叫做總線競爭。I2C總線具有多主控能力,可以對發生在SDA線上的總線競爭進行仲裁,其仲裁原則是這樣的:當多個主器件同時想占用總線時,如果某個主器件發送高電平,而另一個主器件發送低電平,則發送電平與此時SDA總線電平不符的那個器件將自動關閉其輸出級。總線競爭的仲裁是在兩個層次上進行的。首先是地址位的比較,如果主器件尋址同一個從器件,則進入數據位的比較,從而確保了競爭仲裁的可靠性。由于是利用I2C總線上的信息進行仲裁,因此不會造成信息的丟失。

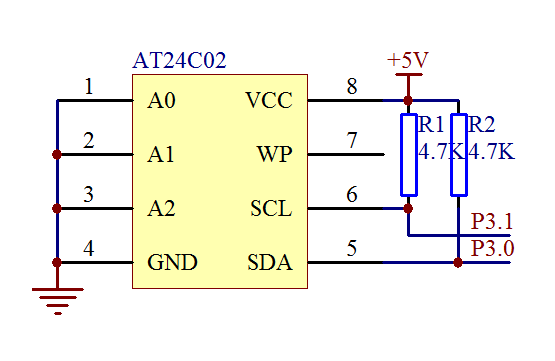

AT24C02與單片機的接口非常簡單,如圖4-8所示。A0,A1,A2為器件地址線,WP為寫保護引腳,SCL,SDA為二線串行接口,符合I2C總線協議。

(圖4-8 24C02存儲電路)

-

EEPROM

+關注

關注

9文章

1010瀏覽量

81404 -

存儲電路

+關注

關注

2文章

11瀏覽量

13099 -

I2C總線

+關注

關注

8文章

388瀏覽量

60826 -

AT24C02

+關注

關注

0文章

79瀏覽量

24248 -

電子萬年歷

+關注

關注

3文章

38瀏覽量

15922

發布評論請先 登錄

相關推薦

電子萬年歷設計方案(4)

電子萬年歷設計方案(4)

評論