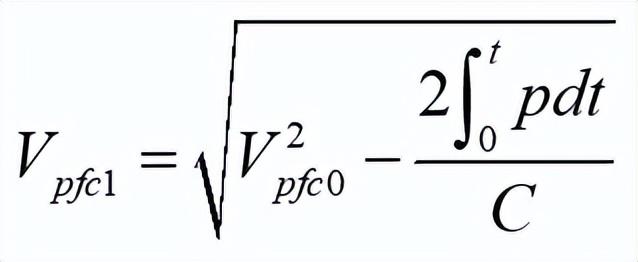

當模塊突加載時,輸入功率來不及變化仍然是原來的功率,因而輸入功率小于輸出功率,從而使得PFC母線電壓下跌。根據能量守恒可知,

式(1)

式中,Vpfc1和Vpfc0分別為PFC母線電壓在突加載下跌過程的終值和初始值,p等于突加載下跌過程中輸出功率減輸入功率(在此過程中p是不斷變化的),t為突加載下跌的時間(也即從動態開始到Ipfc達到輸入功率等于輸出功率時的值),C為母線電容。

從式(1)可以看出,Vpfc下跌值在Vpfc0一定時,取決于電容C、p和下跌時間t,要想減小Vpfc的下跌值可以增大電容C,或者減小功率p,或者減小下跌時間t。但是,在主電路確定以后電容C是一定的;功率p主要取決于突加載增加的功率,這又取決于實際的應用情況,在設計時需要考慮最惡劣的情況(即從空載到滿載),這在確定模塊的功率后一般也是一定的;下跌時間t主要取決于環路控制,是可以通過控制策略來減小的。所以,在突加載情況下,對于改善PFC動態來說,動態控制策略實際上就是想辦法加快環路響應,減小下跌時間t。

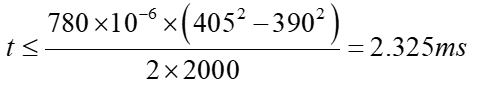

舉個例子,設Vpfc0=405V,電容C=780us,突然從空載加到滿載2000W,那么假如電壓下跌15V到390V的話,時間t應該:

式(2)

PFC控制環路采用的是電壓外環和電流內環組成的雙閉環結構,如圖1所示,下跌時間t可以看成有以下4部分組成:

t = t1 + t2 + t3 + t4 (3)

其中:

t1——從突加載到DSP第一次電壓環計算的時間,可能從0到DSP電壓環計算周期時間不等,如果電壓環是16拍計算一次,那么最大就是177.8us(90kHz計算頻率),如果每拍計算,最大就是11.11us。

t2——Vpfc的采樣和濾波時間,電壓環中有一個30Hz的電壓濾波器,此濾波器的延時是t2的主要組成部分,由于采樣頻率高于計算頻率,所以采樣時間基本可以不考慮。

t3——表征電壓環PI參數的時間,當Kp和Ki越大時,t3就越小。比如說,突加載后期望的電流環給定為Ipfcref,那么t3就是Vpfc下跌產生的電壓偏差Err通過電壓環PI參數累積,使得電流環給定達到Ipfcref的時間。

t4——電流環響應時間。

當然,上述時間的定義只是為了更清楚的分析和設計PFC控制策略,也可以從其他角度來看,實際上也可以將t1 + t2 + t3統稱為電壓環的響應時間。

從構成下跌時間t的幾部分來看,t1取決于電壓環的計算頻率和動態的發生時刻,是不確定的,要減小t1需要提高電壓環的計算頻率,受限于DSP的時間資源提高計算頻率比較困難,而且t1也較小(16拍最大為177.8us,每拍最大為11.11us),可減少的時間有限,所以設計PFC動態控制策略時可以忽略;t4電流環響應時間,一般電流環帶寬為2~3kHz,大概估算應該小于200us,想進一步提高帶寬也比較困難,而且t4本身也較小,再怎么提高帶寬時間減少也很小,所以一般也不太考慮;剩下的t2和t3是下跌時間的主要部分,其中t2的30Hz濾波的延時就有十幾ms,所以PFC動態控制策略主要就是基于減小t2和t3來設計的。

PFC動態控制新算法在源跳變或負載跳變時快速的將期望值賦給電流環給定來改善PFC動態特性,實際上也是通過減小t2和t3來加快電壓環改善動態特性。

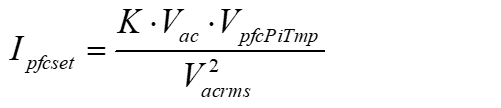

PFC電流環給定為:

式(4)

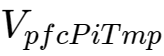

式中,

是電壓環PI調節器輸出。

源跳變控制實現

采用原來的動態控制方案時,在輸入交流電壓跳變時,

不能及時的更新,使得Ipfcset不能及時更新,從而造成輸入功率和輸出功率不平衡,使得Vpfc產生上沖或下跌。只有在Vpfc已上沖或下跌了18V后才進入動態處理程序,所以Vpfc會有較大的上沖或下跌。

新控制算法實時計算Vac有效值,快速的更新Ipfcset到期望值,從而減小Vpfc的波動。

負載跳變控制實現

采用原來的動態控制方案時,當發生負載跳變時,由于電壓環很慢,不能及時更新

,導致功率不平衡,從而造成Vpfc的上沖或下跌。

采用新算法后,根據PFC輸出功率迅速更新

到穩定值,減少功率不平衡的時間,從而減小Vpfc的上沖或下跌。

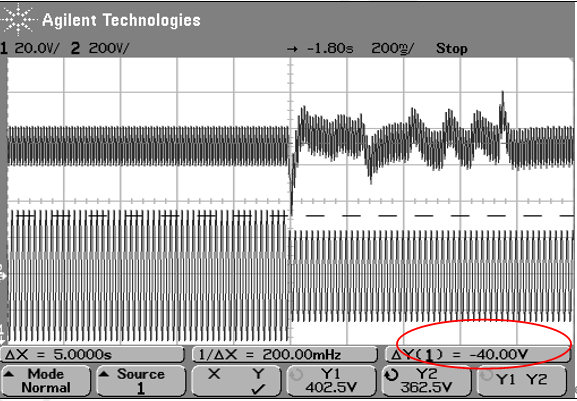

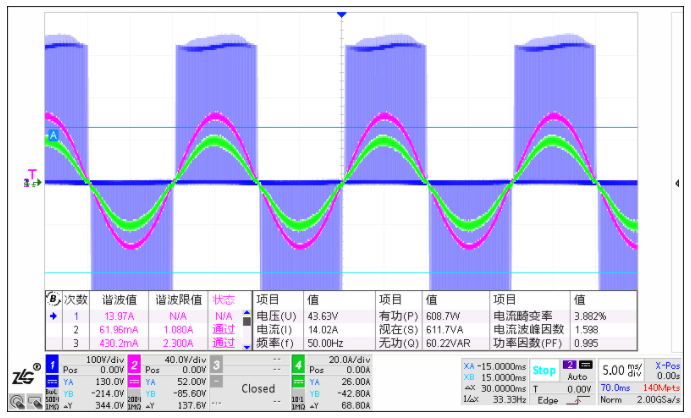

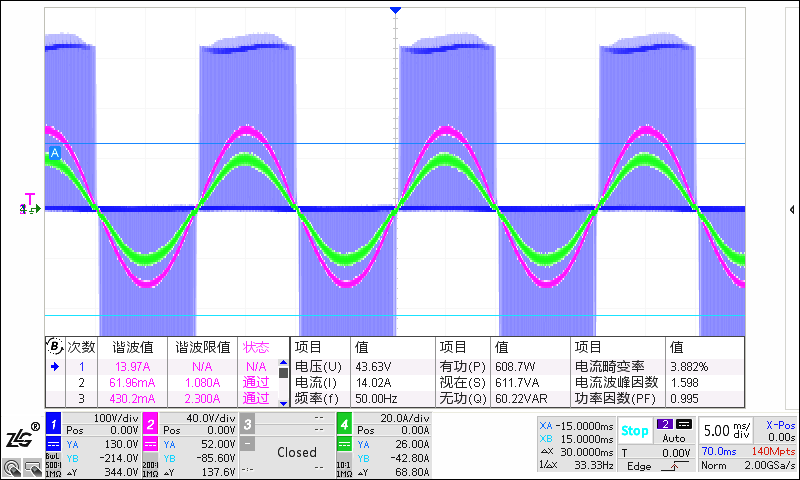

舊策略,輸入電壓180---260V跳變,60Hz,滿載(37.5A),Vpfc和Vac

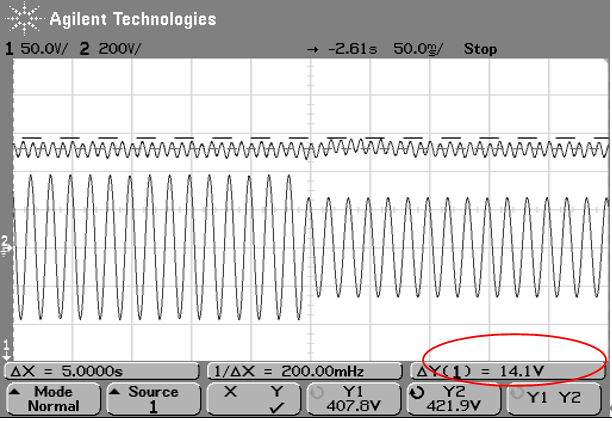

新策略,輸入電壓180---260V跳變,60Hz,滿載(37.5A),Vpfc和Vac

-

dsp

+關注

關注

552文章

7962瀏覽量

348252 -

濾波器

+關注

關注

160文章

7727瀏覽量

177670 -

PFC

+關注

關注

47文章

950瀏覽量

105859 -

輸入功率

+關注

關注

0文章

11瀏覽量

7779 -

母線

+關注

關注

0文章

169瀏覽量

16609

發布評論請先 登錄

相關推薦

數字控制提高了無橋接PFC性能

在數字控制電源中高效調節動態電壓的案例

數字控制真的會取代模擬控制,而成為PFC中的主流控制方式嗎?

數字控制的無橋300W功率因數校正轉換器參考設計

用數字控制提高無橋PFC性能

基于TMS320LF2407的全數字PFC控制技術

單相Boost功率因數校正器的PFC數字控制策略

使用C2000 MCU的數字控制無橋式功率因數校正(BL PFC)

數字控制PFC動態策略

數字控制PFC動態策略

評論