現(xiàn)場(chǎng)可編程門(mén)陣列 (FPGA) 是許多原型和中小批量產(chǎn)品的核心。FPGA 的主要優(yōu)勢(shì)是開(kāi)發(fā)過(guò)程中的靈活性、簡(jiǎn)單的升級(jí)路徑、更快的上市時(shí)間和相對(duì)較低的成本。一個(gè)關(guān)鍵的缺點(diǎn)是復(fù)雜性,F(xiàn)PGA 通常包含復(fù)雜的片上系統(tǒng) (SoC)。

這種復(fù)雜性對(duì)電源提出了苛刻的要求。為應(yīng)對(duì)這些挑戰(zhàn),電源需要多個(gè)輸出以及開(kāi)關(guān)穩(wěn)壓器的組合以提高效率和線性穩(wěn)壓器以實(shí)現(xiàn)清潔電源。

本文描述了 FPGA 的特殊電源要求,解釋了如何為這些智能芯片設(shè)計(jì)電源,然后回顧了針對(duì) FPGA 應(yīng)用的電源模塊的選擇。

計(jì)算系統(tǒng)功率

為FPGA供電似乎為整個(gè)系統(tǒng)供電。電源設(shè)計(jì)工程師面臨著提供 3 到 15 個(gè)電壓軌(有時(shí)甚至更多)的挑戰(zhàn);而這僅僅是開(kāi)始。FPGA 通常使用需要低核心電壓的最新晶圓制造技術(shù)制造,但電源還必須為特殊模塊和電路的多個(gè)軌道供電,提供多個(gè)電壓電平,為高功率模塊提供額外電流,并滿(mǎn)足對(duì)噪聲敏感元件的要求。

只是讓事情變得更復(fù)雜一些,即使是來(lái)自同一制造商的 FPGA 也可能會(huì)有很大差異,因此工程師為每個(gè)芯片選擇最佳電源至關(guān)重要。該選擇取決于諸如每個(gè)電源軌的電壓和功率需求、電源軌的排序要求和系統(tǒng)電源管理需求等因素。

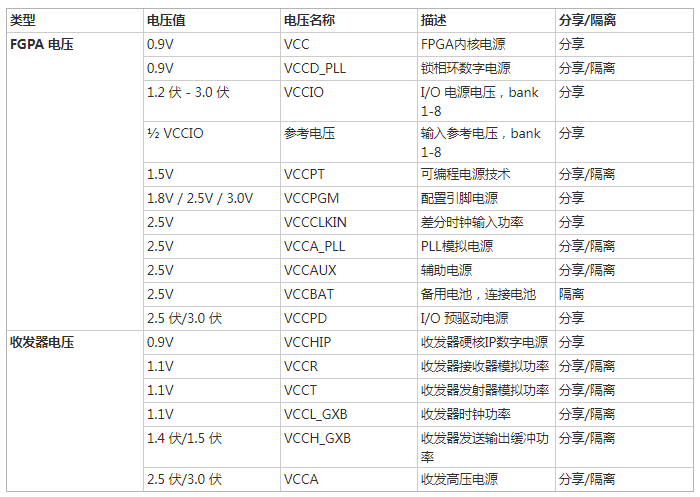

設(shè)計(jì) FPGA 電源的第一步是確定各個(gè)電壓軌及其要求。FPGA 供應(yīng)商通常會(huì)提供一個(gè)“引腳列表”,指定連接到設(shè)備電壓軌的每個(gè)供電引腳的電壓電平。例如,表 1顯示了Altera 的Stratix IV GX FPGA的 一些電壓軌。

表 1:Altera Stratix IV GX 的電壓軌子集。(Altera 提供)

從表 1 可以看出,F(xiàn)PGA 的電源軌運(yùn)行在幾個(gè)不同的電壓下,具體取決于供電的模塊。要求通常包括內(nèi)核(為內(nèi)部邏輯陣列供電)、I/O(驅(qū)動(dòng) I/O 緩沖器,這些緩沖器可以分組在不同的電壓下運(yùn)行)、鎖相環(huán) (PLL)(為 PLL 供電)核)和收發(fā)器(為收發(fā)器、接收器和發(fā)射器提供數(shù)字和模擬電路)。

一旦確定了各個(gè)電壓軌,下一步就是依次計(jì)算每個(gè)軌的電流消耗。應(yīng)將共享鐵軌的電流消耗添加到正在分析的鐵軌中,以得出該鐵軌的總數(shù)。FPGA 制造商經(jīng)常為此提供在線計(jì)算器。接下來(lái),工程師應(yīng)將構(gòu)成 FPGA 的所有元件的功耗相加,以準(zhǔn)確估算整個(gè)芯片的功耗。

計(jì)算完功耗后,下一步是檢查每個(gè)電源軌的電壓變化容限和最大電壓紋波規(guī)范。這些參數(shù)通常可以在 FPGA 的數(shù)據(jù)表中找到。

負(fù)載調(diào)節(jié)規(guī)范確定了電壓調(diào)節(jié)器輸出可能因負(fù)載變化而偏離的范圍(以 mV 為單位)。如果電源來(lái)自開(kāi)關(guān) DC-DC 電壓轉(zhuǎn)換器(“開(kāi)關(guān)穩(wěn)壓器”),則負(fù)載調(diào)節(jié)的典型規(guī)格為 ±5 mV。如果電壓軌指定為 1.2 V,這只是 0.4% 的偏差。

電壓紋波以 mV 為單位從峰到峰測(cè)量,其幅度取決于為所分析的特定軌供電的穩(wěn)壓器的設(shè)計(jì)。輸出濾波嚴(yán)重影響電壓(和電流)紋波性能。(請(qǐng)參閱 TechZone 文章“電容器選擇是良好穩(wěn)壓器設(shè)計(jì)的關(guān)鍵”。)大多數(shù) FPGA 可承受高達(dá) 2% 或更高的電壓紋波,這完全在現(xiàn)代開(kāi)關(guān)穩(wěn)壓器的能力范圍內(nèi)。

開(kāi)關(guān)穩(wěn)壓器還是線性穩(wěn)壓器?

FPGA 電源設(shè)計(jì)過(guò)程的下一步是決定一個(gè)特定的電源軌應(yīng)該由開(kāi)關(guān)穩(wěn)壓器還是線性穩(wěn)壓器供電。需要特別注意為 PLL 和收發(fā)器電路等噪聲敏感電路供電的模擬電源軌。這些軌道上的過(guò)多噪聲可能會(huì)影響電路性能。

線性穩(wěn)壓器提供無(wú)紋波電源,響應(yīng)速度快,使用更簡(jiǎn)單,并且比開(kāi)關(guān)器件占用更少的空間。它們是噪聲敏感型 PLL 和收發(fā)器軌的不錯(cuò)選擇。主要缺點(diǎn)是效率低下,尤其是在輸出電壓遠(yuǎn)低于輸入電壓的情況下。

開(kāi)關(guān)穩(wěn)壓器是更高功率軌的更好選擇,因?yàn)槠涓叩男时雀偷脑肼暩匾K鼈兪菫?FPGA 的數(shù)字內(nèi)核邏輯和 I/O 供電的理想選擇,其中電流要求很容易達(dá)到數(shù)十安培。開(kāi)關(guān)穩(wěn)壓器的缺點(diǎn)是它更復(fù)雜、更大,并且需要更多的外部元件。

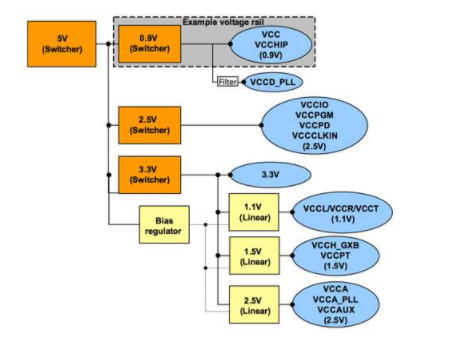

由此產(chǎn)生的電源可能有些復(fù)雜,包括“電源樹(shù)”中的多個(gè)開(kāi)關(guān)穩(wěn)壓器和線性穩(wěn)壓器(圖 2)。

圖 2:由開(kāi)關(guān)和線性穩(wěn)壓器組成的 FPGA 電源。(Altera 提供)

FPGA電源模塊

FPGA的電源 通常包括開(kāi)關(guān)穩(wěn)壓器和線性穩(wěn)壓器的組合,以合理的效率提供不同的電壓和穩(wěn)定的電源。設(shè)計(jì)這樣的電源并非易事,但通過(guò)將電路基于將多個(gè)開(kāi)關(guān)和線性穩(wěn)壓器集成到單個(gè)芯片中的電源模塊,事情可以變得更加簡(jiǎn)單。

例如, Maxim 的 MAX8660電源模塊包含四個(gè)開(kāi)關(guān)穩(wěn)壓器(以 2 MHz 運(yùn)行,因此鼓勵(lì)使用小電感器)和四個(gè)線性穩(wěn)壓器。開(kāi)關(guān)穩(wěn)壓器自動(dòng)從脈沖寬度調(diào)制 (PWM) 切換到輕負(fù)載操作,以降低工作電流并延長(zhǎng)電池壽命。

該器件為開(kāi)關(guān)穩(wěn)壓器提供 0.725-3.3 V (0.4-1.6 A) 的輸出電壓,為低壓差 (LDO) 線性穩(wěn)壓器提供 1.7-3.3 V (30-500 mA) 的輸出電壓,所有電壓均在 2.6 至6 V 輸入。

該芯片還集成了電源管理能力和功能,例如輸出開(kāi)/關(guān)控制、低電量檢測(cè)、復(fù)位輸出和兩線 I 2 C 串行接口。

Intersil為小型 FPGA 應(yīng)用提供ISL9440 。該芯片結(jié)合了三個(gè)開(kāi)關(guān)穩(wěn)壓器和一個(gè) LDO 線性穩(wěn)壓器。每個(gè)輸出可調(diào)低至 0.8 V,該器件采用 4.5-24 V 電源供電。

ISL9440 在緊湊的 5 x 5 mm QFN 封裝中提供內(nèi)部軟啟動(dòng)和獨(dú)立使能輸入,以簡(jiǎn)化電源軌排序。該芯片采用內(nèi)部環(huán)路補(bǔ)償來(lái)最大限度地減少外圍組件,從而實(shí)現(xiàn)緊湊的設(shè)計(jì)和較低的總體解決方案成本。

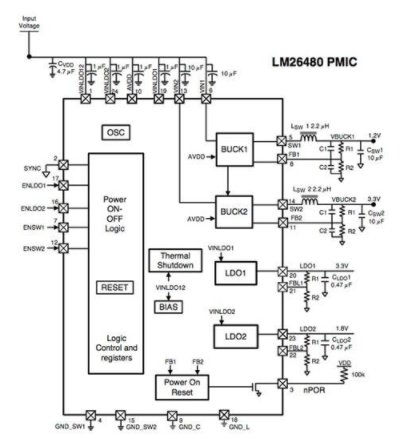

德州儀器(TI) 還提供將開(kāi)關(guān)穩(wěn)壓器的效率與線性穩(wěn)壓器的無(wú)噪聲電源相結(jié)合的電源模塊。例如,LM26480(圖 3)集成了兩個(gè) 1.5 A 降壓(“降壓”)開(kāi)關(guān)穩(wěn)壓器和兩個(gè) 300 mA 線性穩(wěn)壓器。該器件采用 2.8 至 5.5 V 電源供電,第一個(gè)開(kāi)關(guān)穩(wěn)壓器在 1.5 A 時(shí)提供 0.8-2 V,而第二個(gè)在 1.5 A 時(shí)提供 1.0-3.3 V。2 MHz 開(kāi)關(guān)穩(wěn)壓器的工作效率高達(dá) 96%。線性穩(wěn)壓器在高達(dá) 300 mA 時(shí)提供 1-3.5 V。

圖 3:Texas Instruments 的 LM26480 集成了兩個(gè)開(kāi)關(guān)穩(wěn)壓器和兩個(gè)線性穩(wěn)壓器。

-

FPGA

+關(guān)注

關(guān)注

1626文章

21665瀏覽量

601801 -

開(kāi)關(guān)穩(wěn)壓器

+關(guān)注

關(guān)注

4文章

790瀏覽量

73408 -

線性穩(wěn)壓器

+關(guān)注

關(guān)注

5文章

757瀏覽量

66588 -

Altera

+關(guān)注

關(guān)注

37文章

777瀏覽量

153849 -

電源模塊

+關(guān)注

關(guān)注

32文章

1683瀏覽量

92710

原文標(biāo)題:FPGA 應(yīng)用的電源模塊的選擇案

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA 應(yīng)用的電源模塊的選擇

電源模塊的選擇、國(guó)內(nèi)外知名電源模塊廠家排名及廠家優(yōu)勢(shì)特點(diǎn)匯總

如何選擇合適的電源模塊

如何選擇合適的電源模塊?

如何選擇合適的電源模塊?

了解DC電源模塊的基本參數(shù)及選擇方法

如何選擇適合自己應(yīng)用的AC/DC電源模塊?

如何選擇合適的電源模塊?你了解電源模塊可靠性測(cè)試嗎?

FPGA應(yīng)用的電源模塊的選擇案例

FPGA應(yīng)用的電源模塊的選擇案例

評(píng)論