埋入式互連裝置將幫助拯救摩爾定律。

一段時間以來,每種新處理器產生的廢熱都比原先的要多。如果芯片還是按2000年代早期的軌跡發展,它們的熱功率很快將達到每平方厘米6400瓦,相當于太陽表面的功率通量。

但事情沒有變得那么糟糕,工程師們在努力控制芯片功耗。在性能方面,數據中心的片上系統(SoC)設計一直僅次于超級計算機處理器,它們的功耗通常為200至400瓦/平方厘米。智能手機芯片的典型功耗為5瓦左右。

不過,雖然計算機芯片不會真的把口袋燒一個洞(盡管它們產生的熱量的確足以煎雞蛋),但要運行日常的應用程序,它們仍然需要大量的電流。以數據中心的片上系統為例:平均來說,它內部的晶體管功耗大約為200瓦,在約1到2伏的電壓環境下,這意味著芯片需要從穩壓電源中汲取100到200安的電流。冰箱的電流一般僅為6安。高端手機的功耗是數據中心片上系統的1/10,但即便如此,電流仍然達到了10至20安。也就是說,你的口袋里可能裝著3臺冰箱!

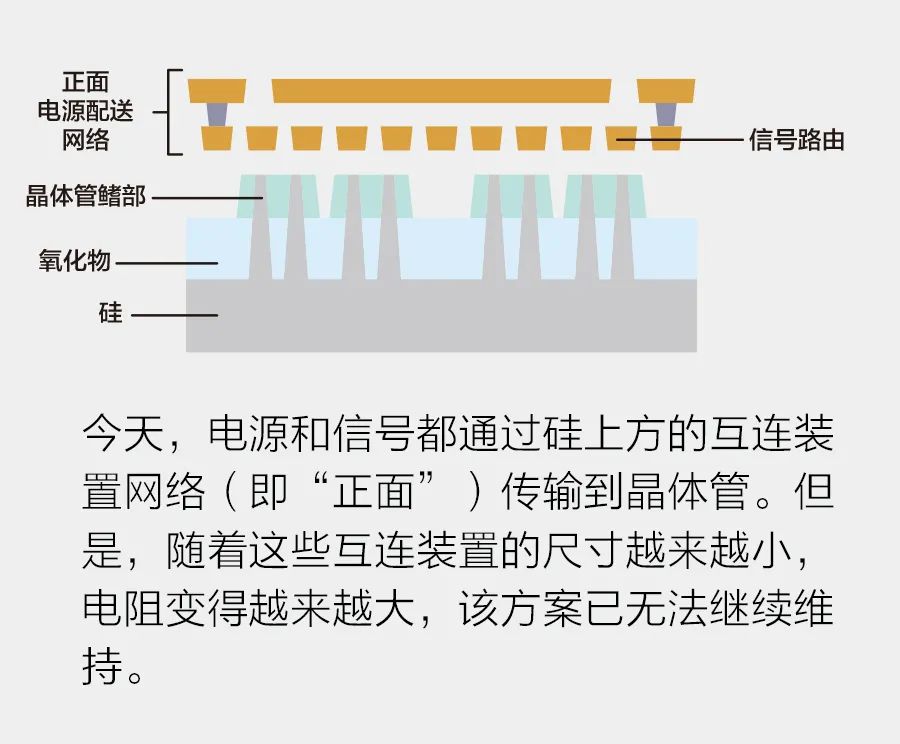

將電流傳送至數十億個晶體管正迅速成為高性能片上系統設計的主要瓶頸之一。隨著晶體管不斷變小,為其提供電流的互連裝置必須封裝得越來越緊密,做得越來越小巧,但這會增加電阻和衰減電源。這條路已走不下去:如果不對芯片器件的電子進出方式進行大的改變,無論我們制造多小的晶體管都無濟于事。

幸運的是,我們有一個很有希望的解決方案:可以使用長期被忽視的硅的另一面。

從產生電子的電源到用電子進行計算的晶體管,電子要走很長的一段路。在大多數電子設備中,電子沿著印刷電路板的銅線到達片上系統的封裝,經過連接芯片與封裝的焊錫球進入芯片,然后通過芯片上的互連裝置連接到內部晶體管。最后這一步才是真正最重要的。

想知道為什么,最好先了解芯片的制造過程。片上系統從一塊高質量的晶體硅開始。我們首先在這塊硅的最上面做一層晶體管。接下來,用金屬的互連裝置將晶體管連接起來,形成有計算功能的電路。這些互連裝置是一層一層疊起來的,被稱為堆棧,要為當今芯片上的數十億個晶體管提供電源和數據傳輸,堆棧需要達到10到20層。

為了連接微小的晶體管,最靠近硅晶體管的那幾層又薄又小,但隨著堆棧高度的上升,它們的尺寸會變大。這些互連裝置層越寬,電阻越小,越有利于電源供電。 然后,可以看到,為電路——電源配送網絡(PDN)——供電的金屬位于晶體管的頂部。我們稱之為正面電源。我們還看到,電源配送網絡會不可避免地與信號傳輸網絡爭奪空間,因為它們共享同一組銅資源。

為了使片上系統獲取電源和傳輸信號,我們通常將最上面(離晶體管最遠)的金屬層連接到芯片封裝的焊錫球(也稱為“凸點”)。因此,電子要到達任意一個晶體管做有用功,必需穿過10到20層越來越窄且彎彎曲曲的金屬層,直至最終到達最后一層的本地連接。

這種電源配送方式肯定是有損耗的。在這條路徑的每一階段,有些電能損失了,還有一些用于控制配送本身。對于今天的片上系統,設計者通常有一個損耗預算,允許封裝和晶體管之間的電壓降低10%。因此,如果電源配送網絡的總效率達到90%及以上,那么我們的設計就是正確的。

從歷史上看,這種效率可以通過良好的工程設計實現,有些人甚至可能說,與我們今天面臨的挑戰相比,這很容易解決。對于今天的電子設備,片上系統設計者不僅要管理不斷增加的功率密度,而且要管理每一代的功率損失都在急劇增加的互連裝置。

不斷增加的損耗與制造納米級導線的工藝有關。這一工藝及其使用的材料可以追溯到1997年左右,當時IBM開始用銅代替鋁制造互連裝置,整個行業也隨之轉變。在那之前,鋁線一直是良好的導體,但隨著摩爾定律曲線向前發展,它們的電阻很快變得太高、不可靠。在現代集成電路規模下,銅的導電性更好。但一旦互連裝置的寬度縮小到100納米以下,銅的電阻也開始出現問題。

如今,已制成的最小互連裝置約為20納米,電阻已成為一個亟待解決的問題。 為了描繪互連裝置中的電子,可將它比喻成臺球桌上的一副臺球。現在想象一下把它們從桌子的一端推到另一端。少數幾個球會在途中發生相互碰撞和反彈,但大多數會沿著直線行進。現在再設想一下把球桌縮小一半,那么你會看到更多的碰撞,球的移動也會變慢。

接下來,再次縮小球桌,并將臺球的數量增加10倍,這就是芯片制造商現在面臨的情況。真正的電子不一定會發生碰撞,但它們相互距離足夠近時,產生的分散的力會干擾其在導線中的流動。在納米尺寸下,這會導致導線中的電阻大大增加,引發嚴重的電源損耗。

電阻增大不是一個新挑戰,但現在每個后續工藝節點的電阻增大幅度卻是前所未有的。此外,管理這種增長的傳統方法已不再適用,因為納米級的制造規則強加了許多限制。為了防止電阻增加,可以任意增加某段導線寬度的日子已經過去了。現在,設計者必須嚴格遵守導線寬度的特定規范,否則芯片可能無法制造。因此,行業面臨雙重問題,即互連裝置的電阻升高以及在芯片空間的縮小。

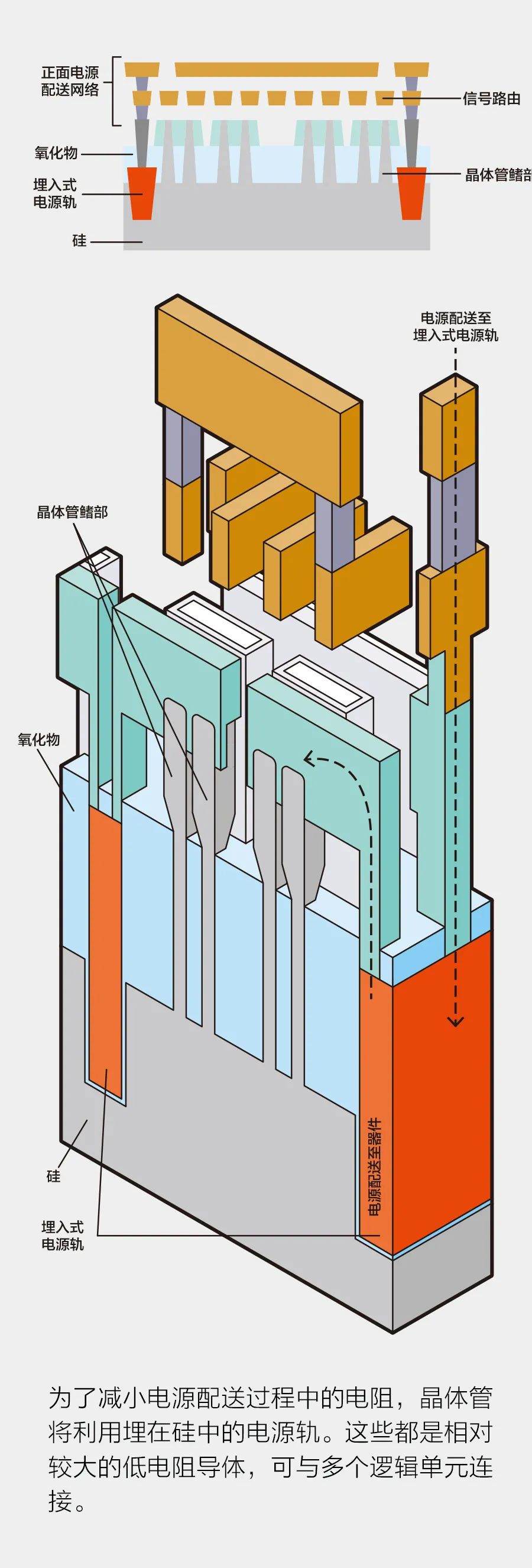

還有一種方法:可以利用晶體管下面的“空”硅。在作者貝恩(Beyne)和佐格拉福斯(Zografos)工作的微電子研究中心(Imec),我們率先提出了一種“埋入式電源軌”(BPR)制造概念。這項技術不是在晶體管上面而是下面建立電源連接,目的是建造更豐滿、電阻更小的電源軌道,并為晶體管層上面的信號傳輸互連裝置騰出空間。

要制作BPR,我們首先需要在晶體管下面挖出深槽,然后用金屬填充,而且要在制造晶體管之前做這件事。金屬的選擇也很重要。這種金屬需要承受制造高質量晶體管工藝步驟的溫度,可達1000℃左右。在這個溫度下,銅會熔化,進而污染整塊芯片。因此,我們選用熔點更高的釕和鎢進行試驗。

因為晶體管下方有許多未使用的空間,我們可以把BPR溝槽做得又寬又深,非常適合電源配送。與位于晶體管頂部的金屬薄層相比,BPR的電阻是前者的1/20到1/30。這意味著BPR能有效地向晶體管配送更多的電源。

此外,將電源軌從晶體管頂部移開,可為信號傳輸互連裝置騰出空間。這些互連裝置形成了基本的電路“單元”——最小的電路單位,如SRAM內存位單元或者用來構成復雜電路的簡單邏輯單元。利用釋放出來的空間,我們可以將這些單元縮小16%或更多,最終轉化為每塊芯片上更多的晶體管。即使特征尺寸保持不變,我們仍然可將摩爾定律推進一步。

遺憾的是,僅埋設局部的電源軌是不夠的。我們仍然需要將電源從芯片頂部向下傳輸到這些電源軌,這會降低效率和損失部分電壓。

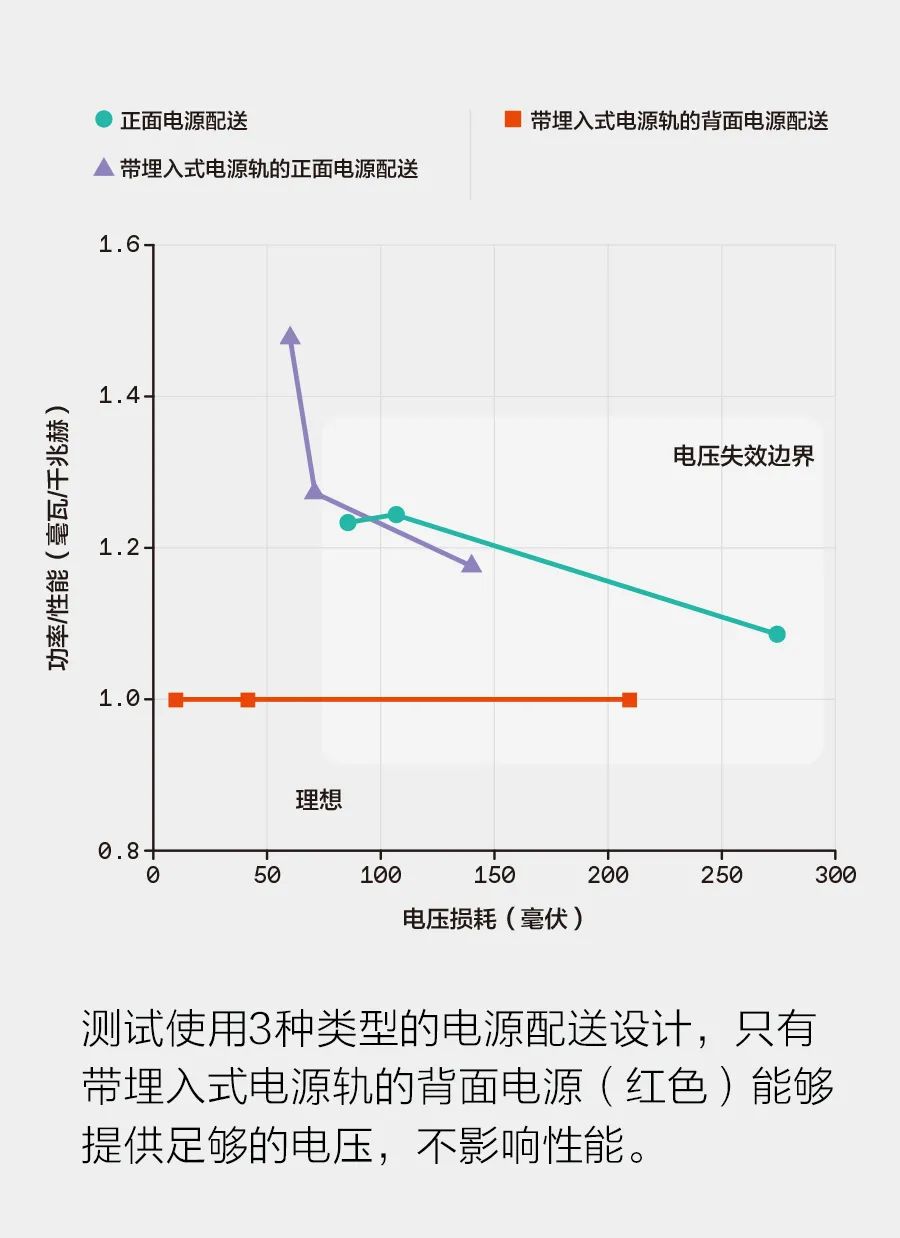

英國ARM公司的研究人員,包括作者克萊恩(Cline)和普拉薩德(Prasad),在他們的一個CPU上進行了模擬,發現BPR構建的電源網絡比普通正面電源網絡效率高40%。但他們也發現,即使使用正面輸電的BPR,傳輸到晶體管的總電壓也不足以維持CPU的高性能運行。

幸好,Imec同步制定了一個可進一步改進電源配送的補充方案:將整個電源配送網絡從芯片的正面移到背面。這種解決方案被稱為“背面電源輸送”,或者籠統地說是“背面金屬化”。它將晶體管下方的硅減薄至500納米以下,以打出納米尺寸的“硅通孔”(TSV)。這些納米硅通孔是垂直互連裝置,可以通過硅的背面連接到埋入式電源軌的底部,就像數百個小型礦井一樣。在晶體管和BPR下方創建納米TSV后,就可以在芯片背面放置更多的金屬層,形成完整的電源配送網絡。

我們在Arm對之前的模擬進行擴展時發現,只需兩層厚的背面金屬就足以完成這項工作。只要能將納米TSV的間距小于2微米,我們就可以設計一種背面電源配送網絡,其效率是帶有埋入式電源軌的正面電源配送網絡的4倍,是傳統正面電源配送網絡的7倍。

背面電源配送網絡的額外優勢是與信號網絡物理分離,這兩個網絡不再爭奪同一金屬層資源。每個網絡都有更多的空間。這也意味著,金屬層特性不再需要在電源路由的偏好(又厚又寬,以獲得低電阻)和信號線路的路由(又薄又窄,可連接密集的晶體管)之間尋求折衷。我們可以同時為電源路由調整背面金屬層,為信號路由調整正面金屬層,兩全其美。

在Arm的設計中,我們發現無論是傳統的正面電源配送網絡,還是帶有埋入式電源軌的正面電源配送網絡,我們都需要犧牲設計性能。但用背面電源配送網絡,CPU就能夠實現高頻,并實現高效的電源配送。

當然,你可能想知道這個方案如何將信號和電源從封裝傳輸到芯片。在這里,納米TSV也是關鍵。可以用它們將所有輸入和輸出信號從芯片的正面傳輸到背面。這樣,電源和I/O信號都可以連接到放置在背面的焊錫球上。

仿真研究是一個很好的開端,它們展示了采用BPR背面電源配送網絡的CPU設計水平潛力。但將這些技術應用于大批量制造還有很長的路要走。還有重大的材料和制造挑戰需要解決。選擇最佳的BPR和納米TSV金屬材料對可制造性和電效率至關重要。此外,制造BPR和納米TSV都需要的高深寬比(深而窄)溝槽非常難。在硅襯底上可靠地蝕刻間距緊密、深而窄的溝槽,并用金屬填充,對于芯片制造業來說是一種相對較新的方法,也是業界需要認真解決的問題。對于開啟納米TSV的廣泛應用,開發可靠且可重復的制造工具和方法是必不可少的。

另外,采用電池供電的片上系統,如手機和其他功率受限的設計,已經擁有比我們目前討論的更為復雜的電源配送網絡。現代電源配送將芯片分成了多個電源域,可以在不同的電壓下工作,甚至為了省電可以完全關閉(參見可延長電池壽命的電路)。

因此,背面電源配送網絡和BPR最終必須做更多工作,而不僅僅是有效傳輸電子。它們要精確地控制電子的去向和到達目的地的電子數量。芯片設計師在芯片級電源設計方面,不希望倒退好幾步。因此,我們必須同時優化設計和制造,以確保BPR和背面電源配送網絡優于今天的節能集成電路技術,或者至少與之相當。

未來的計算取決于這些新的制造技術。無論你擔憂數據中心的冷卻費用還是智能手機每天的充電次數,耗電量都至關重要。隨著我們不斷縮小晶體管和集成電路的尺寸,電源配送成為一項重要的芯片挑戰。如果工程師能夠克服隨之而來的復雜性,BPR和背面電源配送網絡可能會很好地應對這一挑戰。

審核編輯:劉清

-

處理器

+關注

關注

68文章

19165瀏覽量

229128 -

穩壓電源

+關注

關注

61文章

1360瀏覽量

99906 -

SoC設計

+關注

關注

1文章

148瀏覽量

18762 -

晶體管

+關注

關注

77文章

9634瀏覽量

137848

原文標題:來自下方的電源,?埋入式互連裝置將幫助拯救摩爾定律

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

晶圓和摩爾定律有什么關系?

摩爾定律也適用于EPON芯片商用之路?

半導體行業的里程碑“摩爾定律”竟是這樣來的

摩爾定律推動了整個半導體行業的變革

摩爾定律,摩爾定律是什么意思

摩爾定律定義與發展

摩爾定律的歷程

SiP回歸“拯救”摩爾定律

埋入式互連裝置將幫助拯救摩爾定律

埋入式互連裝置將幫助拯救摩爾定律

評論