旁路電容在數(shù)字電路系統(tǒng)中所起的基本且重要作用,即儲能與為高頻噪聲電流提供低阻抗路徑,盡管還并未給旁路電容的這些功能概括一個“高大上”的名字,然而旁路電容所起的終極作用就是為了電源完整性(Power Integrity, PI),它與信號完整性(Signal Integrity, SI)均為高速數(shù)字PCB設(shè)計中的重要組成部分,后續(xù)有機(jī)會我們將會進(jìn)行詳細(xì)講解。

事實上,旁路電容的這兩個基本功能在某種意義上來講是完全統(tǒng)一的:你可以認(rèn)為旁路電容的儲能為高頻開關(guān)切換(充電)提供瞬間電荷,從而避免開關(guān)產(chǎn)生的高頻噪聲向距離芯片更遠(yuǎn)的方向擴(kuò)散,因為開關(guān)切換需要的能量已經(jīng)在靠近芯片的旁路電容中獲取到了,你也可以認(rèn)為旁路電容提供了高頻噪聲電流的低阻抗路徑,從而避免了高頻開關(guān)時需要向更遠(yuǎn)的電源索取瞬間電荷能量。

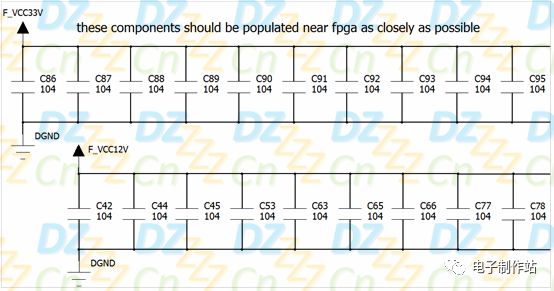

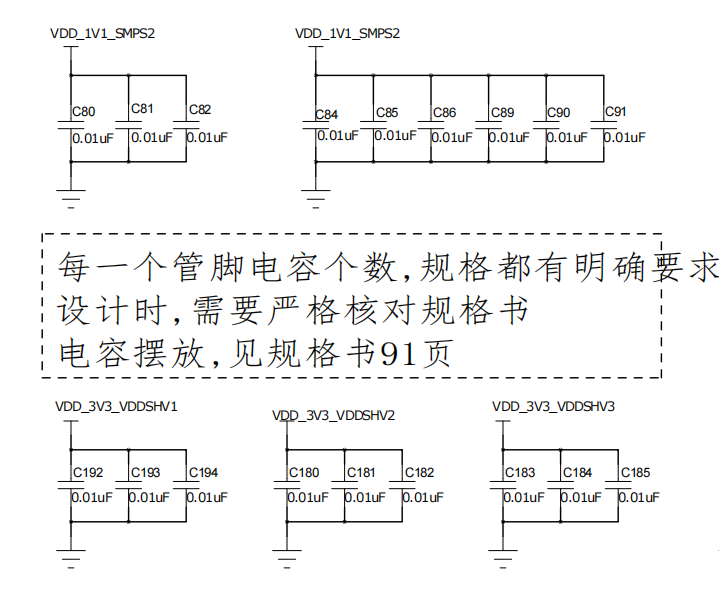

有一定經(jīng)驗的工程師都會發(fā)現(xiàn):旁路電容的容值大多數(shù)為0.1uF(100nF),這也是數(shù)字電路中最常見的,如下圖所示為FPGA芯片的旁路電容:

那這個值是怎么來的呢?這一節(jié)我們就來討論一下這個問題。

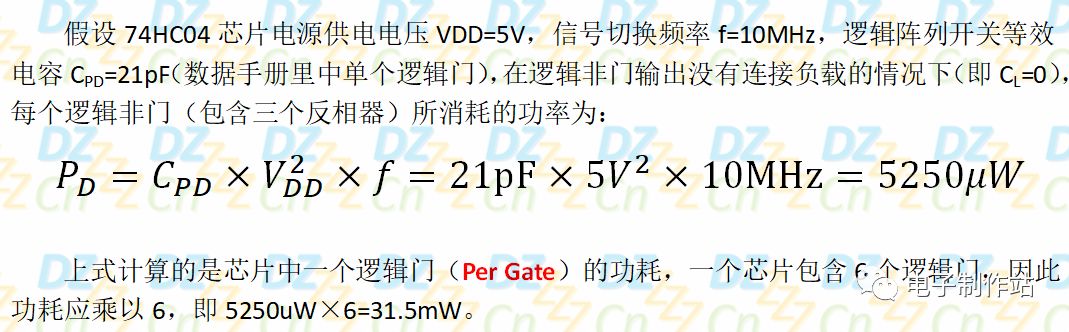

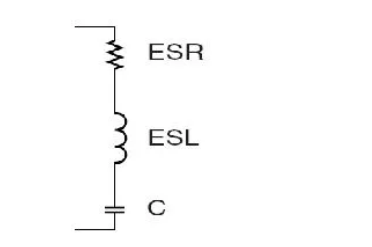

前面已經(jīng)提到過,實際的電容器都有自諧振頻率,考慮到這個因素,作為數(shù)字電路旁路電容的容量一般不超過 1uF,當(dāng)然,容量太小也不行,因為儲存的電荷無法滿足開關(guān)切換時瞬間要求的電荷,那旁路電容的容量到底應(yīng)該至少需要多大呢?我們用最簡單的反相器邏輯芯片(74HC04)實例計算一下就知道了。

實際芯片的每個邏輯門基本結(jié)構(gòu)如下圖所示(以下均來自Philips 74HC04數(shù)據(jù)手冊)

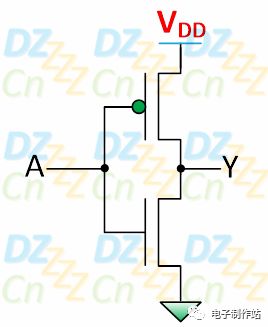

而每個CMOS反相器的基本結(jié)構(gòu)如下圖所示(具體參考文章【邏輯門(1)】):

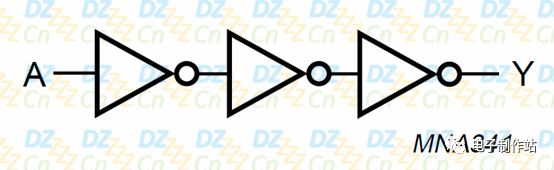

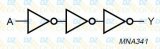

每個邏輯非門(Gate)由三個反相器串聯(lián)組成,如下圖所示(芯片為什么會這樣設(shè)計可參考文章“邏輯門”):

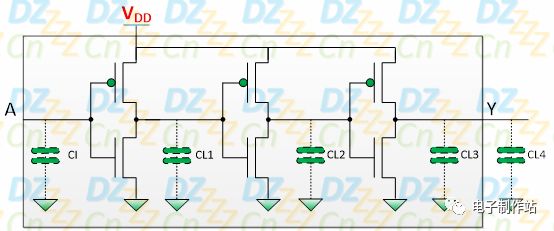

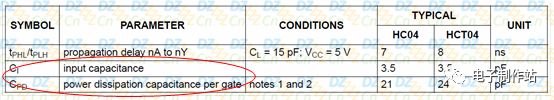

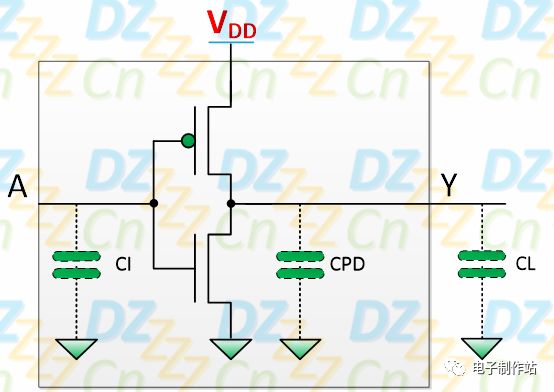

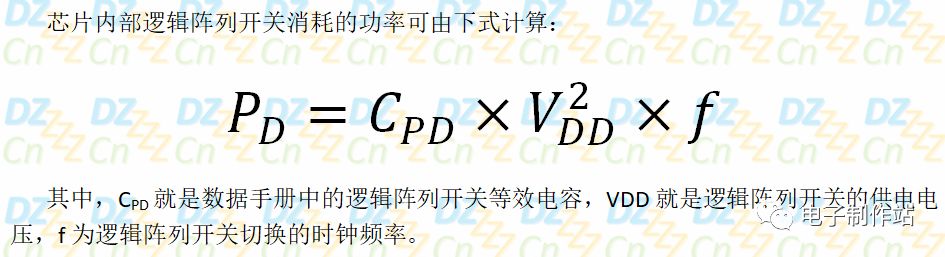

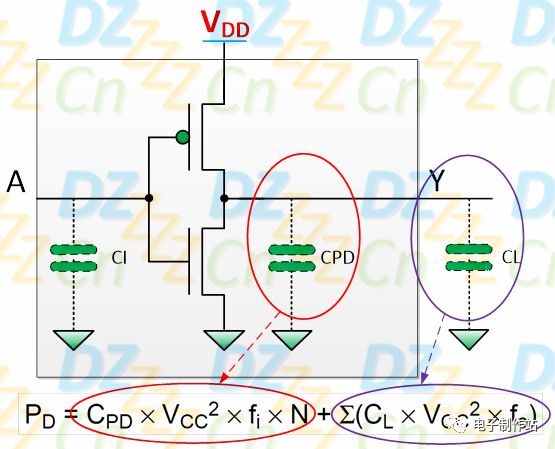

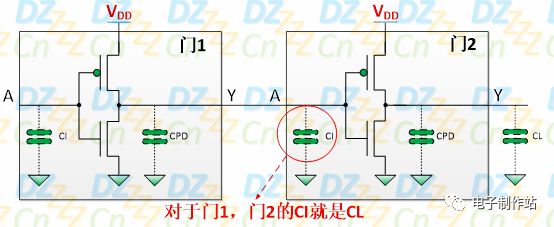

上圖中,CI表示芯片信號引腳的輸入電容(Input capacitance),CL表示輸出負(fù)載電容(OutputLoad capacitance)。對于每一級反相器,后一級反相器的輸入電容CI即作為前一級開關(guān)的輸出負(fù)載電容,當(dāng)然,反相器開關(guān)本身也會有一定的輸出寄生電容,它們也包含在CL內(nèi),一個邏輯非門(包含三個反相器)的所有等效負(fù)載電容就是內(nèi)部邏輯陣列開關(guān)在切換時需要向電源VDD索取能量的來源(換言之,開關(guān)切換時需要對這個等效負(fù)載電容進(jìn)行充放電操作),這個邏輯陣列開關(guān)等效電容在數(shù)據(jù)手冊中通常用CPD(power dissipation capacitance per gate)表示,如下圖所示:

注意:在這個數(shù)據(jù)手冊中,CPD是一個邏輯非門(Per Gate)的開關(guān)等效電容。

在74HC04芯片中,CPD就相當(dāng)于是CL1、CL2、CL3的等效電容(不一定是簡單的相加),而CL4取決于芯片外接負(fù)載,因此,我們也可以將電路等效如下圖所示:

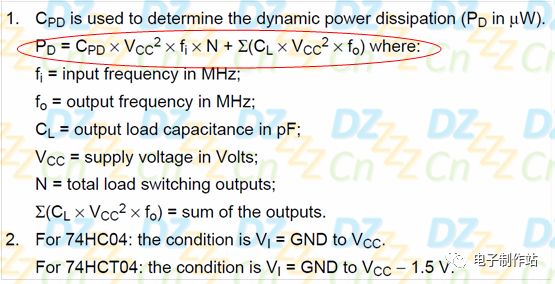

有人問:這個公式怎么來的?權(quán)威么?我書讀得少,不要騙我!數(shù)據(jù)手冊中有呀,如下圖所示:

上圖中的公式分成了兩個部分,但結(jié)構(gòu)是一模一樣的,前面一部分與我們給出的公式是相同的,表示芯片內(nèi)部邏輯陣列開關(guān)等效負(fù)載電容CPD的功耗,而后一部分與芯片外接負(fù)載CL有關(guān)(也稱之為等效IO開關(guān)電容),輸出引腳IO連接有多少個負(fù)載,就將相應(yīng)負(fù)載電容CL的功耗全部計算起來,如下圖所示:

有人問:輸入電容CI就不計算進(jìn)去嗎?乖乖,對于芯片輸出引腳連接的負(fù)載而言,負(fù)載的輸入電容CI就是引腳的等效負(fù)載電容CL呀,輸出負(fù)載連接(并聯(lián))越多,則等效負(fù)載電容CL就越大,消耗的功率也就越大,如下圖所示:

一般而言,CL(CI)值是總是相對容易找到的,數(shù)據(jù)手冊中通常都會有,因為輸出連接什么負(fù)載你肯定是知道的,但CPD卻不一定在數(shù)據(jù)手冊能查得到,因此,我們在計算芯片的功耗時可能會分為芯片內(nèi)與芯片外兩個部分。

最基礎(chǔ)的數(shù)據(jù)計算方法我們已經(jīng)知道了,有兩種方法可以估算旁路電容的最小容量:

第一種計算方法思路:邏輯陣列開關(guān)等效電容(CPD)需要獲取足夠的電荷能量,那芯片的旁路電容的容量必定不能比芯片總CPD更小,通常旁路電容的容量比芯片總CPD大25~100倍,我們稱其為旁路電容倍乘系數(shù)(bypass capacitor multiplier,這里取個中間數(shù)50),由于74HC04包含六個邏輯非門,從數(shù)據(jù)手冊上也可以查到CPD約為21pF,因此,芯片總CPD應(yīng)為21pF×6=126pF,再考慮到50倍的旁路電容系數(shù),旁路電容的容量必須要大于126pF×50=6.3nF。

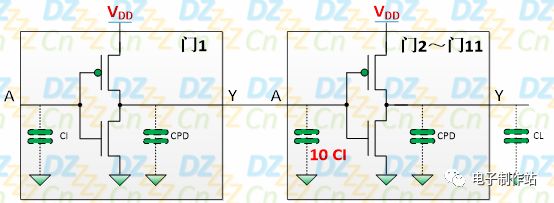

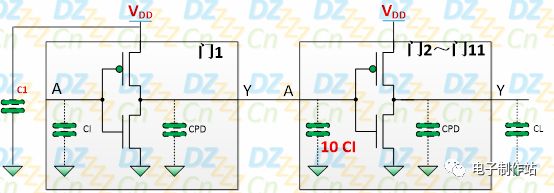

以上計算的是芯片輸出未連接負(fù)載的情況,假設(shè)反相器后面并接了10個邏輯非門(CMOS門電路的扇出系數(shù)一般為20~25),則此時等效電路如下圖所示:

對于門1來說,此時芯片的輸出負(fù)載電容CL=10×CI=10×7pF=70pF,對于整個系統(tǒng)而言,這個CL也可以算是門1的邏輯陣列開關(guān)等效電容,因為從圖上可以看出,它消耗的是門1的電源能量(而不是門2~門11),這樣根據(jù)上述同樣的算法,門1外接旁路電容的容量至少應(yīng)為(21pF+70pF)×50=4.55nF,當(dāng)然,這只是一個邏輯非門的計算結(jié)果,如果芯片中其它5個非門也是同樣的負(fù)載連接,則需要的旁路電容容量至少應(yīng)為4.55nF×6=27.3nF,在考慮到電路設(shè)計裕量情況下,我們可以直接選擇100nF的旁路電容。

那功耗PD計算的意義在哪里?前面我們是走了狗屎運(yùn),芯片夠簡單,所以數(shù)據(jù)手冊里提供了CPD的具體值,但更多的應(yīng)用場合下是沒有辦法直接獲取這個值的,我們看看更大規(guī)模集成芯片的情況。

大規(guī)模邏輯芯片的旁路電容容量的計算原理也是大體一致的,邏輯陣列開關(guān)每秒鐘轉(zhuǎn)換的次數(shù)至少會以百方來計算(MHz),我們以ALTERA公司FPGA CYCLONE IV芯片來計算一下外接負(fù)載時負(fù)載電容(不包括內(nèi)部邏輯開關(guān)陣列等效電容CPD,為什么?下面會提到)所消耗的功率。

假設(shè)IO供電電源電壓VCCIO為3.3V,時鐘頻率為100MHz,負(fù)載數(shù)量為30個(也就是輸出外接了負(fù)載的IO引腳),輸出引腳的平均負(fù)載電容為10pF,則旁路電容的容量至少應(yīng)為:10pF×30×50=15000pF=15nF。

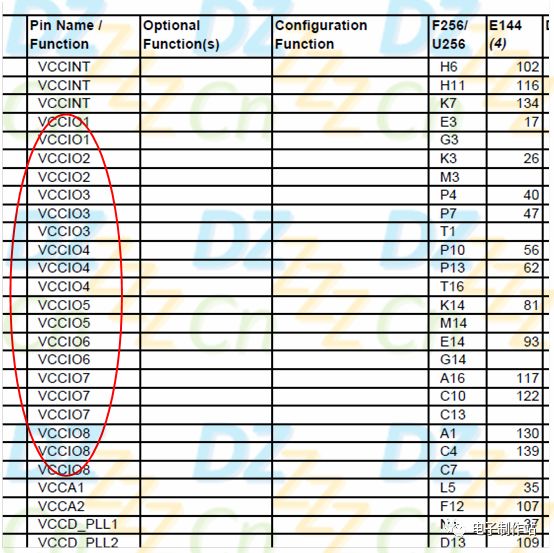

對于FPGA之類的大規(guī)模集成芯片,內(nèi)核電壓VCCINT或IO電壓VCCIO都會有多個,如果計算某一個電源引腳所需的旁路電容的容量,還需要除以這些電源引腳的個數(shù),如下圖所示:

不同封裝芯片的VCCIO數(shù)量是不一樣的,F(xiàn)256/U256(BGA)封裝有20個,而E144(QFP)封裝只有12個,但是FPGA的VCCIO是按BANK來供電的(就是VCCIO后面帶的那個數(shù)字,數(shù)字相同表示BANK相同,不了解FPGA的讀者不必深究),不應(yīng)該直接除了這個總數(shù),如果這30個連接的負(fù)載分布在2個BANK,對于E144封裝每個BANK約有2個VCCIO電源,僅需要除以數(shù)量4就行了,因此,單個電源引腳所需要的旁路電容容量應(yīng)至少約為3.75nF。

我們可以用滅火的水龍頭來理解:當(dāng)芯片只有一個電源引腳時,相當(dāng)于滅火的水龍頭只有一個,而芯片有多個電源引腳時,相當(dāng)于滅火的水龍頭有多個,在火災(zāi)危害程度相同的情況下,需要滅火的用水量是一定的,因此,對于有多個水龍頭的情形而言,單個水龍頭需要的用水量需求就少了,當(dāng)然,總的用水量肯定是一樣的,亦即總的旁路電容值是不會變化的。

上面只是計算芯片外接負(fù)載時需要的旁路電容容量,那如何計算內(nèi)部邏輯陣列等效電容呢?沒辦法直接去計算,除非知道具體的CPD的值(前面我們是走運(yùn)),但是這個值通常是不提供的,因為這個值會隨實際電路邏輯規(guī)模的大小與功能而有很大的不同,那就沒有辦法了嗎?NO!

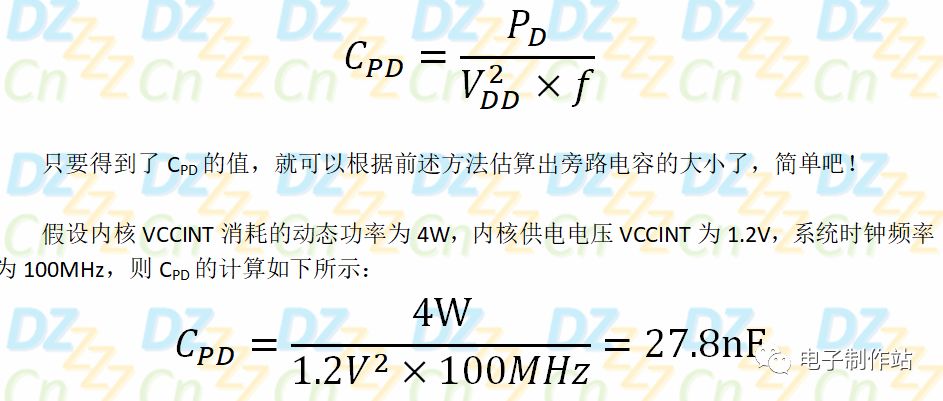

我們可以用測量儀器實際測量出FPGA芯片在具體邏輯功能應(yīng)用時所消耗的動態(tài)功率PD,或使用配套的功耗分析軟件進(jìn)行功耗的計算,總而言之,芯片邏輯陣開關(guān)等效電容的功耗PD的值總是可以獲取出來的,再根據(jù)之前的功耗計算公式反推出CPD,如下所示:

27.8nF已經(jīng)不小了,再乘上50倍旁路電容的倍數(shù),則旁路電容的總?cè)萘恐辽賾?yīng)為27.8nF×50=1390nF=1.39uF,因此,動態(tài)功耗越大的芯片需要在旁邊放置更多的旁路電容就是這個道理。

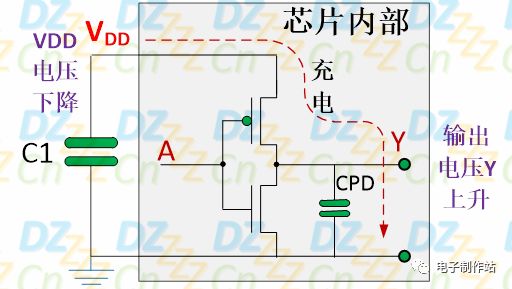

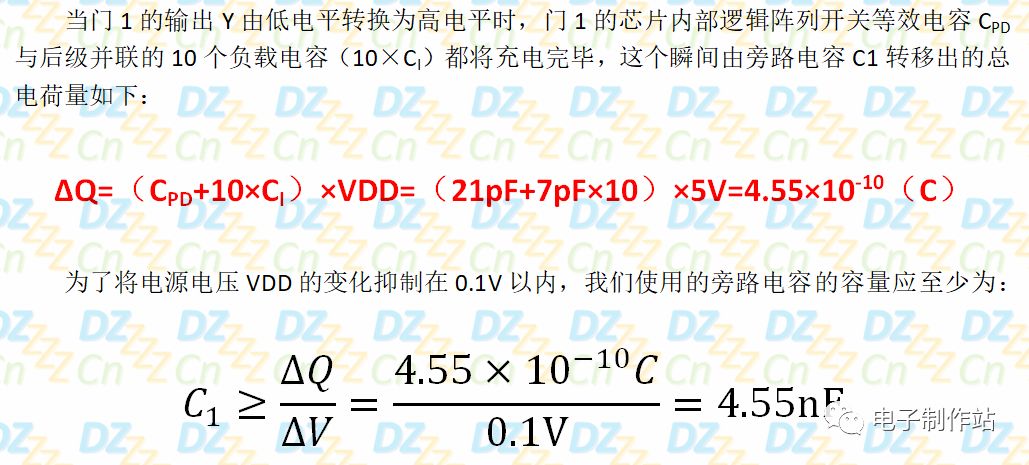

另外一個計算方法是:假定旁路電容的電荷量能將VDD變化量維持在某一特定范圍內(nèi)(比如VDD僅變化0.1V),我們根據(jù)邏輯陣列開關(guān)等效電容CPD的電荷消耗需求來估算旁路電容的容值,如下圖所示:

當(dāng)PMOS管(上側(cè)帶圈圈)開關(guān)打開時,VDD電源對芯片邏輯陣列開關(guān)等效電容CPD充電,CPD電容兩端的電壓會上升,旁路電容C1兩端的電壓(VDD)將會下降,因為旁路電容C1的部分電荷已經(jīng)轉(zhuǎn)移到了CPD中,為了維持電壓VDD變化不超過0.1V,我們可以根據(jù)需要轉(zhuǎn)移的電荷量與VDD電壓的允許變化量求出旁路電容的最小容量。

我們還是以一個邏輯非門驅(qū)動10個邏輯非門的情況來計算CPD的大小,如下圖所示:

如果芯片中的其它5個邏輯非門也是同樣的負(fù)載連接,則旁路電容的最小容量至少應(yīng)為4.55nF×6=27.3nF,這個計算結(jié)果與前一種方法相差無幾。在考慮設(shè)計裕量的情況下,我們也會使用100nF(0.1uF)的旁路電容。

事實上,以上兩者估算的本質(zhì)是完全相同的,我們同樣可以用水龍頭的比喻來理解旁路電容容量的計算原理,但同一道菜上得太多就沒意思了,我們換另做一道菜來吃:

假設(shè)芯片邏輯開關(guān)總等效電容CPD(不僅包括芯片本身的CPD,也包括負(fù)載總電容CL)相當(dāng)于一個取水的杯子,而旁路電容C1相當(dāng)于儲藏水源的地方,我們認(rèn)為儲水之地的水位相當(dāng)于電源電壓VDD,如果儲水之地是一只盛滿水的小碗,那么CPD這只杯子從小碗中取一杯水(也就是CPD充滿電的總電荷)后,小碗中的水位就會下降(相當(dāng)于電源VDD下降),因為兩者儲水的空間相差并不大,而如果儲水之地是一大缸水,則從中取同樣CPD一杯水對這缸水的水位影響非常小,因此,如果你想要這個水位(VDD)變化越小,則儲水之地(旁路電容的容量)就必須比CPD要大得多。

審核編輯:劉清

-

旁路電容

+關(guān)注

關(guān)注

7文章

178瀏覽量

24788 -

PCB設(shè)計

+關(guān)注

關(guān)注

394文章

4671瀏覽量

85319 -

電源完整性

+關(guān)注

關(guān)注

9文章

209瀏覽量

20709 -

數(shù)字電路系統(tǒng)

+關(guān)注

關(guān)注

0文章

4瀏覽量

5597 -

FPGA芯片

+關(guān)注

關(guān)注

3文章

246瀏覽量

39784

原文標(biāo)題:旁路電容0.1uF,是怎么來的?詳解!

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

max232能用0.1uf電容嗎

芯片附近為什么要放置0.1uF電容

為什么旁路電容緊盯著IC不放?為什么旁路電容總是0.1uF?

電容10uf和0.1uf并聯(lián)使用,這大小和個數(shù)是怎么算的?資料下載

電路中0.1UF和10UF電容有什么用?怎么用?資料下載

揭秘0.1uF容量的旁路電容的由來

芯片電源腳放0.1uF的電容的作用

芯片IC0.1uF的電容,這些參數(shù)是如何確定

電源端加旁路電容的作用 電源旁路電容為何選擇0.1uF 10uF?

資深詳解:旁路電容0.1uF是這樣來的

旁路電容0.1uF是怎么來的?

旁路電容0.1uF是怎么來的?

評論