很多同學(xué)向我提過一個疑問:PCB設(shè)計中GND是整面覆銅和用線連起來,這種方式哪種效果好?

很多老EDA工程師做兩層電源板都不習(xí)慣覆銅,具體什么原因也很難說清楚,這種方式GND的連接效率很低,反而會被新手嘲笑。直接鋪個銅箔,表層上幾百個GND的焊盤就自動連接起來了,還用一根根的手動去連,太搞笑了。搞的很多老EDA工程師在新手面前都不知道怎么布線了。

其實,小易覺得沒有絕對的對和錯,GND整體覆銅和用線連起來,不能太絕對說哪種好,哪種壞,而是要看具體的布線環(huán)境,比如線路板的層數(shù)、層疊和電源的種類多少都有關(guān)系的。從PDN電源仿真角度來看,是有一個標(biāo)準(zhǔn)的,那就是:保****證電源的回路電感最小。

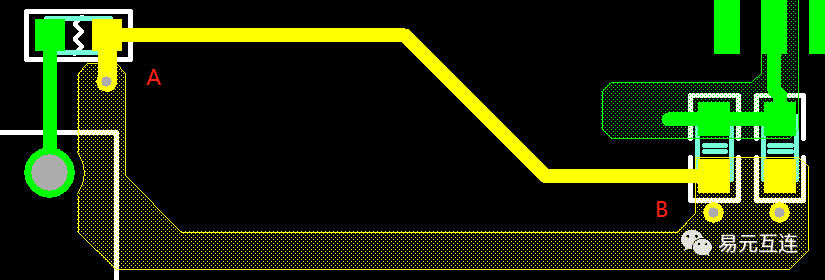

我們根據(jù)PDN仿真的思路來尋求電源回路電感的最小方式,大家知道電源的回路就是GND的流向,在PCB設(shè)計中有很多的GND屬性的焊盤,GND是1對多的情況,一個GND焊盤同時和很多GND焊盤、線和通孔保持了物理屬性的連接,如下圖這種情況,A-B兩點的連接就有直接線連、銅箔連接和打孔內(nèi)部連接這3種方式,那這3種方式電源回路都是平均分的嗎?

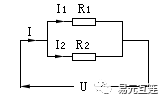

電源回路怎么走?它當(dāng)然不會像我們想象中的那么聽話,在高中物理也講到過一個并聯(lián)電阻的模型,如下圖,當(dāng)R1遠小于R2時,電流會選擇走R1的,R2

幾乎可以看做一個斷路。在A-B兩點也存在類似的問題,線連接、銅箔連接和打孔內(nèi)層連接可以看做是R1、R2和R3這3路并聯(lián)在一起,要使電源回路電感最小,就要看R1、R2和R3哪一路的阻抗最小。

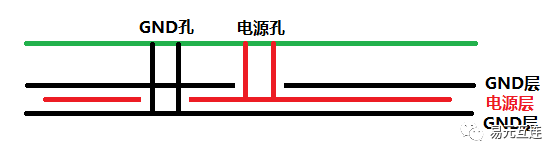

阻抗最小就要保證回流的路徑最短,上圖中可以看到A處直接在GND焊盤處打孔,這樣電源和GND的回流路徑最短。因為有GND和電源層,表層和電源和GND屬性的焊盤連接都會直接在焊盤旁邊打孔,然后將電源和GND層引入內(nèi)層統(tǒng)一連接起來。如下圖所示,這樣電源層和GND層兩層間組成一個大的回路,同時考慮到20h原則,會在板邊打一些GND孔,這樣讓GND的銅箔面積大于電源層的面積。

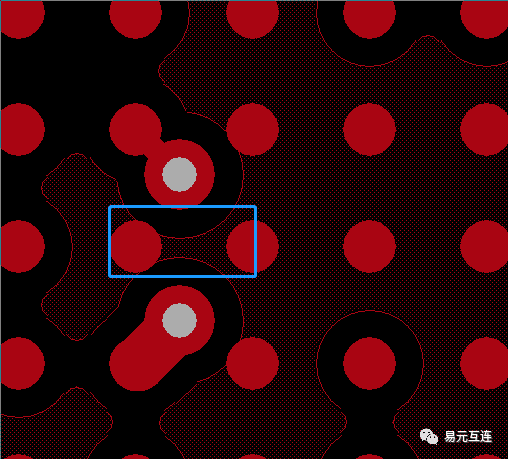

這樣做嚴(yán)格上說不需要TOP和BOTTOM層也覆GND銅箔,因為GND屬性的焊盤不會在表層連起來,表層覆GND銅箔會帶來一些意想不到的雜銅問題, 比如下圖BGA區(qū),會碰到GND的焊盤通過很細的銅箔勉強連起來,這個寬度可能超出了板廠的最小工藝。

為了防止這種情況,一般的處理方法是BGA區(qū)域禁止覆GND銅箔,或者TOP和BOTTOM層不覆蓋GND銅箔。GND焊盤要連接到GND,必須從焊盤拉出一段線,然后打孔連接到GND層。

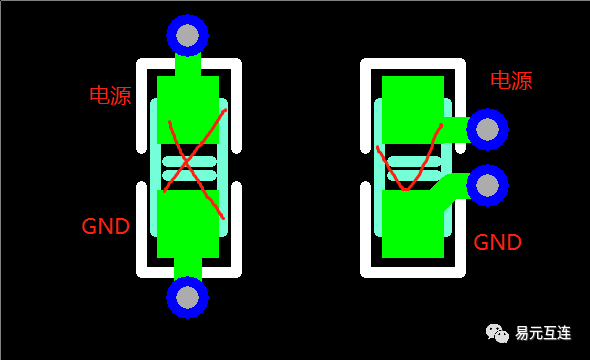

如下圖所示,電源和GND焊盤都滿足拉出線打孔連接到內(nèi)層,但左邊電源和GND的在電源和GND層間的通孔之間回流路徑很大,右邊的處理方法就很好,保證電源和GND地在同層間路徑最短,是最好的處理方法。

通過以上的研究,大家知道了:有電源層和GND層的多層板,整體覆GND銅箔是最佳選擇。那如果沒有電源層和GND層呢?比如只有兩層的電源板,是不是也要覆GND銅箔呢?

兩層板的情況就不同了,首先沒有GND層,也就預(yù)示著在GND焊盤旁直接打孔到另外一層,下方不一定正好是GND的網(wǎng)絡(luò)。再者,EDA工程師在拉線的時候,知道GND焊盤最后是整體覆銅解決的,走線的時候就不會拉GND的線;在最后看到只剩下GND的焊盤沒連起來,就直接兩層全部覆GND銅箔,然后再通過EDA軟件去查還有哪些焊盤是open的。

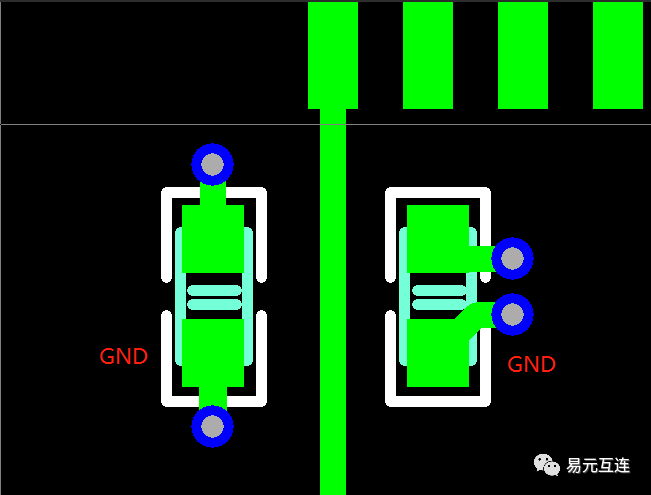

這樣造成的問題是,只關(guān)心到GND是否都連起來,不會去關(guān)心回流路徑是否最短,比如下圖中,如果手動連線,兩個GND焊盤可以表層連起來的,但覆銅后,雖然可以打孔通過另外一層連起來,但路徑長了很多。而且有時候,為了把GND孔要拉出焊盤好遠,才能找到另外一層的GND銅箔連起來。

-

eda

+關(guān)注

關(guān)注

71文章

2712瀏覽量

172937 -

電源板

+關(guān)注

關(guān)注

27文章

92瀏覽量

24154 -

覆銅

+關(guān)注

關(guān)注

0文章

56瀏覽量

12070

發(fā)布評論請先 登錄

相關(guān)推薦

PCB設(shè)計中GND是整體覆銅還是用線連起來

PCB設(shè)計中GND是整體覆銅還是用線連起來

評論