簡(jiǎn)介

小功率DCDC芯片及其應(yīng)用電路已廣泛應(yīng)用于工業(yè)和消費(fèi)等電子類產(chǎn)品中,由于系統(tǒng)中的濾波電路和去耦電容等使系統(tǒng)具有一定的抗高頻紋波干擾能力,因此在測(cè)量DCDC的輸出電壓紋波時(shí),示波器的帶寬限制通常選擇20MHz。但是在某些高精密測(cè)量系統(tǒng)和射頻應(yīng)用系統(tǒng)中,高頻紋波會(huì)給系統(tǒng)帶來一系列干擾問題,因此,為了驗(yàn)證DCDC輸出電壓紋波是否滿足系統(tǒng)對(duì)于高頻紋波的限制,測(cè)量電壓紋波時(shí)示波器帶寬限制會(huì)選擇500MHz,稱為DCDC的輸出電壓噪聲測(cè)試。由于高頻信號(hào)易于通過寄生參數(shù)進(jìn)行耦合,所以對(duì)于DCDC電路的設(shè)計(jì)提出了很大挑戰(zhàn)。以下通過PCB layout優(yōu)化,輸入輸出去耦電容設(shè)計(jì),示波器測(cè)量方法優(yōu)化等三方面來有效抑制DCDC輸出電壓紋波中的高頻成分。本文以TPS563209為例進(jìn)行詳細(xì)的論述和實(shí)驗(yàn)驗(yàn)證。

PCB layout優(yōu)化

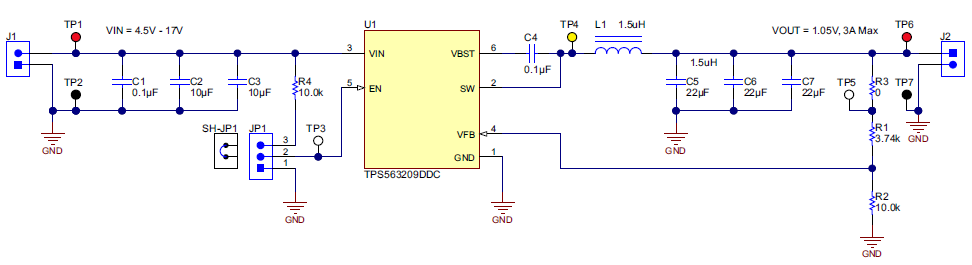

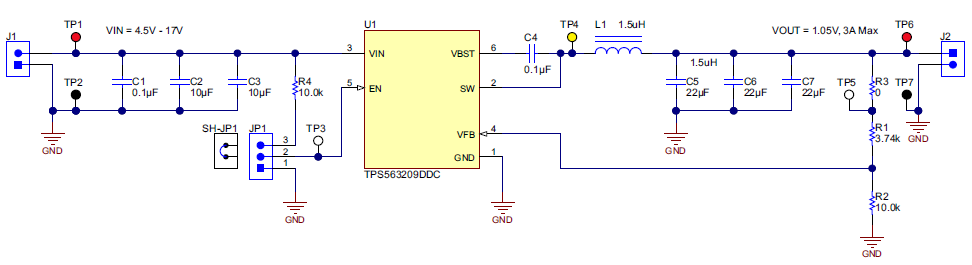

圖1是TPS563209EVM-652的原理圖,在這個(gè)功率電路中,核心的功率回路包含輸入電容,芯片內(nèi)置的高邊和低邊MOSFET,功率電感和輸出電容,因此,在PCB layout的過程中,盡量減小功率回路的走線距離和增加功率回路的走線寬度,可以有效減小功率功率回路的寄生參數(shù),從而有效降低TPS563209工作時(shí)產(chǎn)生的高頻噪聲。

圖1 TPS563209EVM-652原理圖

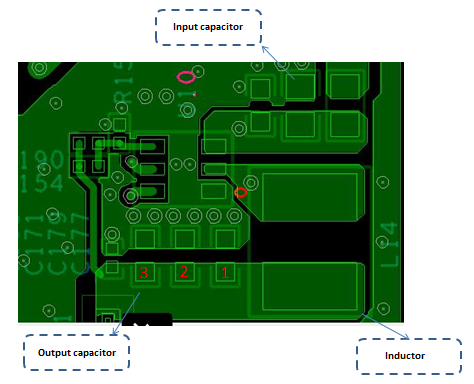

圖2是推薦的TPS563209 PCB layout,所有器件均在同一層,GND通過芯片底部走線將輸入電容地,芯片地和輸出電容地直接連接,輸入電容,芯片,電感和輸出電容的回路最小,輸入端和輸出端都有100nF去耦電容,由于開關(guān)噪聲從開關(guān)電路內(nèi)部產(chǎn)生,所以輸入去耦電容靠近芯片VIN腳,輸出去耦電容靠近最后一個(gè)輸出電容,電壓采樣點(diǎn)選取輸出去耦電容的正端。

圖2 TPS563209推薦PCB Layout

輸入輸出去耦電容設(shè)計(jì)

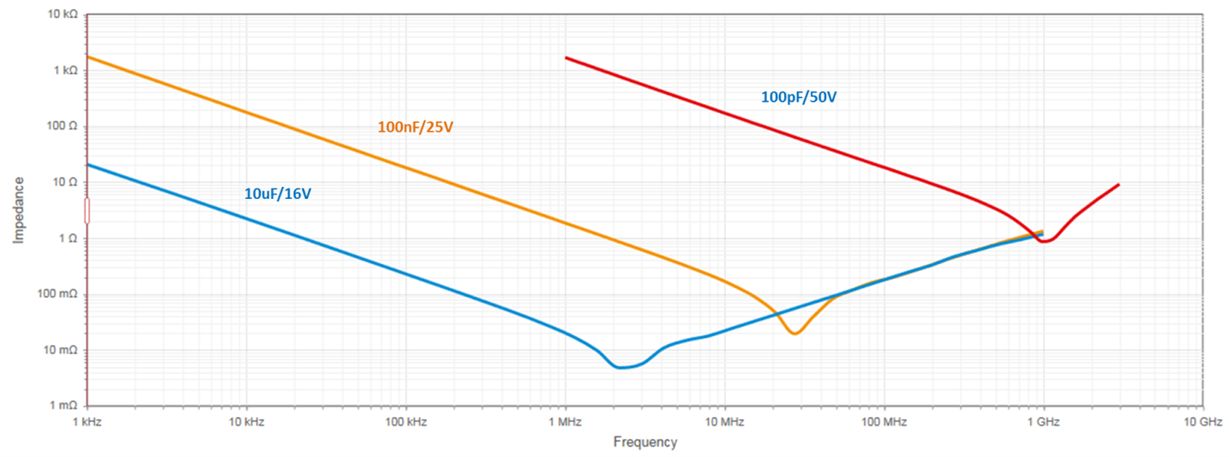

圖3是陶瓷電容的頻率響應(yīng)曲線。

在低頻時(shí),電容的容抗起主導(dǎo)作用,所以隨著頻率的增加等效阻抗降低,在高頻時(shí),電容的感抗起主導(dǎo)作用,所以隨著頻率的增加等效阻抗升高。

不同容值的電容對(duì)頻率的響應(yīng)曲線不同,如圖3,在3種陶瓷電容中,10uF/16V電容容值最大,所以低頻時(shí)等效阻抗較低,因此在開關(guān)電源設(shè)計(jì)中適合用來做儲(chǔ)能電容,例如TPS563209的輸入和輸出均放置了uF級(jí)的陶瓷電容。

100nF/25V電容容值居中,圖3中等效阻抗曲線顯示轉(zhuǎn)折頻率為28MHz,在MHz頻率范圍的等效阻抗較低,在測(cè)試DCDC輸出電壓噪聲時(shí),示波器帶寬為500MHz,所以nF級(jí)電容在對(duì)于DCDC輸出噪聲的濾波作用較好。本文測(cè)試中選擇100nF/25V陶瓷電容作為去耦電容。

100pF/50V電容容值最小,等效阻抗曲線顯示轉(zhuǎn)折頻率為1GHz,所以100pF電容對(duì)高頻信號(hào)的濾波作用較好,一般pF級(jí)電容在高頻通信中使用較多。

示波器測(cè)量方法優(yōu)化

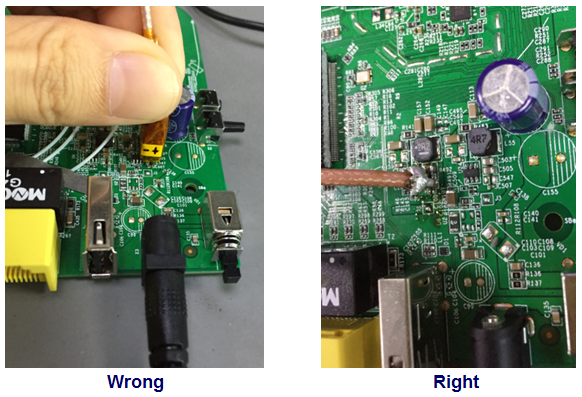

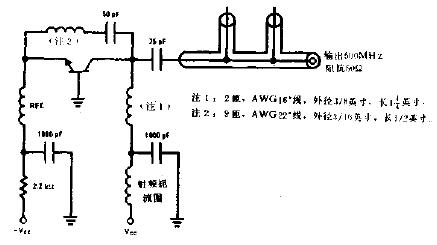

在輸出電壓紋波的測(cè)試中,工程師通常選擇圖4中左圖的測(cè)試方式,將同軸線的信號(hào)線和地線分別焊接金屬探針,然后用手將兩個(gè)金屬探針分別按壓在輸出去耦電容的正負(fù)兩端。這種測(cè)試方法中金屬探針和電容的接觸點(diǎn)不牢靠,容易引入高頻噪聲,但是在輸出電壓紋波的測(cè)試中,示波器帶寬通常設(shè)置為20MHz,高頻噪聲可以被有效濾除,所以從示波器顯示的信號(hào)波形中觀測(cè)不到高頻噪聲。

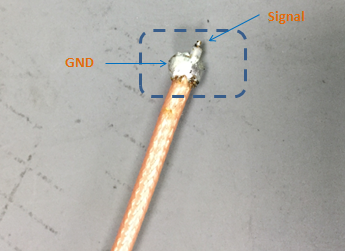

但是在輸出電壓噪聲的測(cè)試中,示波器帶寬設(shè)置為500MHz,高頻噪聲沒有被有效濾除,而是被直接顯示在示波器的信號(hào)波形中。因此在輸出電壓噪聲的測(cè)試中,同軸線需要經(jīng)過仔細(xì)處理,如圖5所示,地線和信號(hào)線的距離盡量小,以減小高頻噪聲的耦合回路。然后將同軸線焊接在100nF去耦電容上,如圖4中右圖所示。

圖4 輸出電壓噪聲測(cè)試方法

圖5 測(cè)試同軸線

實(shí)驗(yàn)結(jié)果

實(shí)驗(yàn)條件:

DCDC變換器:TPS563209

輸入電壓:12V

輸出電壓電流:1V/3A

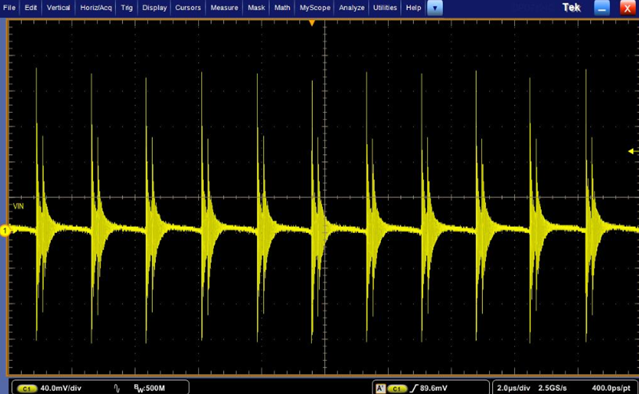

圖6是基于較差的PCB layout和錯(cuò)誤的測(cè)試方法的測(cè)試結(jié)果,顯示輸出電壓噪聲為310mV。

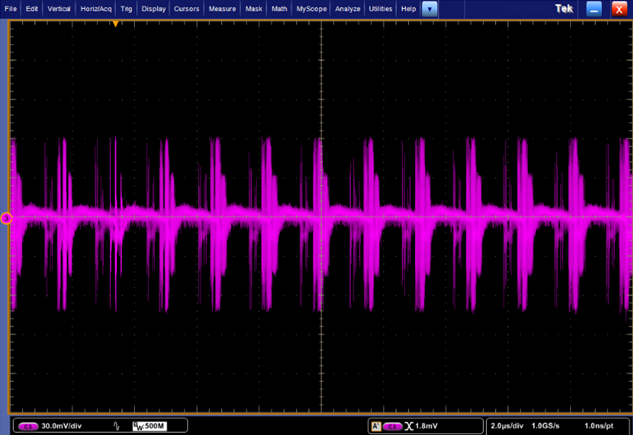

圖7是基于良好的PCB layout和錯(cuò)誤的測(cè)試方法的測(cè)試結(jié)果,顯示輸出電壓噪聲為140mV。

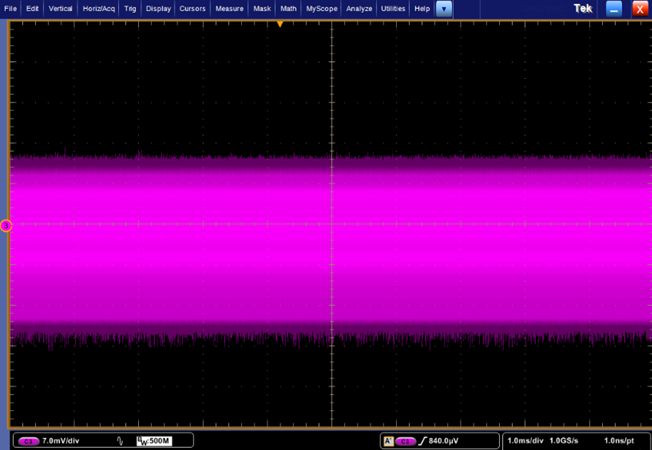

圖8是基于良好的PCB layout和正確的測(cè)試方法的測(cè)試結(jié)果,顯示輸出電壓噪聲為34mV。

從實(shí)驗(yàn)結(jié)果可以看出,良好的PCB layout和正確的測(cè)試方法對(duì)輸出電壓噪聲的測(cè)試至關(guān)重要。

圖6 Bad PCB layout and Bad test method

圖7 Good PCB layout and Bad test method

圖8 Good PCB layout and Good test method

結(jié)論

TPS563209是一款性能優(yōu)良的DCDC變換器,可以滿足對(duì)輸出電壓噪聲的嚴(yán)苛要求。

為了獲得較低的TPS563209輸出電壓噪聲,在DCDC設(shè)計(jì)和輸出電壓噪聲測(cè)量時(shí)需要注意以下3點(diǎn)。

良好的PCB layout。

合適的去耦電容選擇。

合理的測(cè)試方式。

審核編輯:郭婷

-

芯片

+關(guān)注

關(guān)注

453文章

50387瀏覽量

421784 -

示波器

+關(guān)注

關(guān)注

113文章

6190瀏覽量

184512 -

變換器

+關(guān)注

關(guān)注

17文章

2087瀏覽量

109135

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

如何產(chǎn)生500MHz的時(shí)鐘信號(hào)?

DCDC變換器TPS563209在DCDC設(shè)計(jì)和輸出電壓噪聲測(cè)量的應(yīng)用

500MHz單位增益帶寬的OPA656運(yùn)算放大器

DCDC變換器輸出電壓噪聲優(yōu)化和測(cè)試

基于TPS563209輸出電壓噪聲優(yōu)化和測(cè)試

TPS563209 采用 SOT-23-6 封裝的 4.5V 至 16V 輸入、3A 同步降壓轉(zhuǎn)換器

MSO/DS4000系列數(shù)字示波器帶寬100MHz ~ 500MHz

純電動(dòng)汽車電機(jī)嘯叫噪聲優(yōu)化

DC696A LT5546EUF | 具有VGA和I/Q解調(diào)器和寬基帶帶寬的500MHz IF接收器

以TPS563209為例進(jìn)行詳細(xì)的論述和實(shí)驗(yàn)驗(yàn)證

基于500MHz帶寬的TPS563209輸出電壓噪聲優(yōu)化和測(cè)試

Tektronix DPO5054數(shù)字示波器500MHz

Tektronix DPO5054數(shù)字示波器500MHz

基于500MHz帶寬的TPS563209輸出電壓噪聲優(yōu)化和測(cè)試

基于500MHz帶寬的TPS563209輸出電壓噪聲優(yōu)化和測(cè)試

評(píng)論