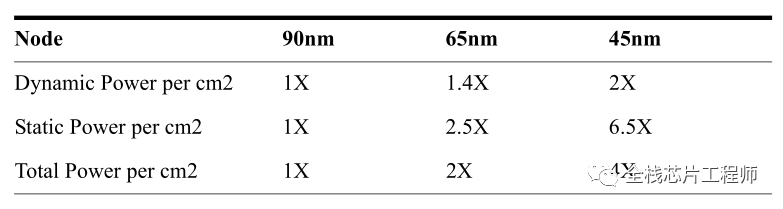

低功耗設計的重要性,從下圖可窺一斑,隨著工藝節點的推進演化,45nm工藝的動態功耗、靜態功耗相比90nm工藝分別增加到了2倍、6.5倍。隨著工藝節點演進到14nm、7nm等先進節點,Leakage Power的占比越來越高,Power gating的低功耗設計則十分關鍵。

功耗與IR分析密不可分,本文先講芯片功耗類型,再講Voltus IR分析。

降低功耗優勢:

避免移動電子設備頻繁充電; 避免芯片過熱,延長芯片壽命; 避免高成本封裝(陶封),若芯片功耗低,使用塑封即可; 避免芯片封裝散熱裝置(水冷、加銅片)的成本;

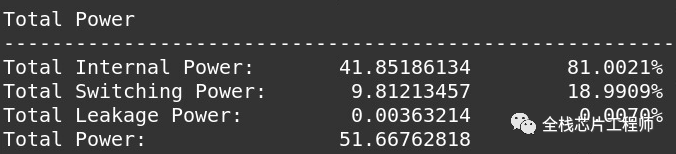

通常功耗分析完成后,工作目錄下將得到power.rpt、power.db和*.ptiavg文件,其中*.ptiavg、power.db文件將用于IR分析,而power.rpt則會列出詳細功耗組成部分,包括以下三個部分:短路功耗(Internal Power),翻轉功耗(Switching power),漏電流功耗(Leakage Power)。

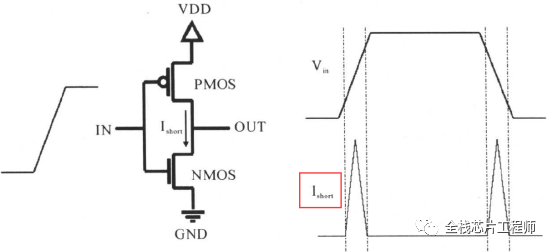

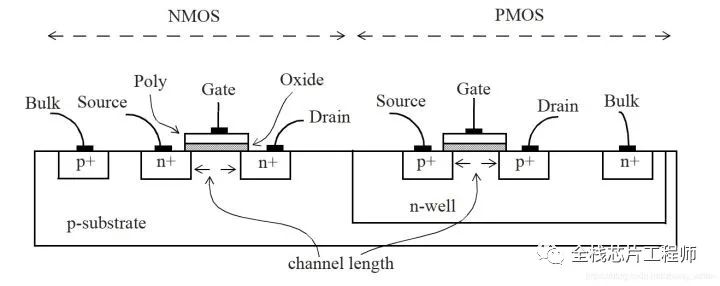

短路功耗(Internal Power)

內部功耗又稱短路功耗,在輸入信號翻轉時,信號的翻轉不可能瞬時完成,因此PMOS和NMOS不可能總是一個截止另外一個導通,總有那么一小段時間是PMOS和NMOS同時導通,那么從電源VDD到地VSS之間就有了通路,就形成了短路電流。

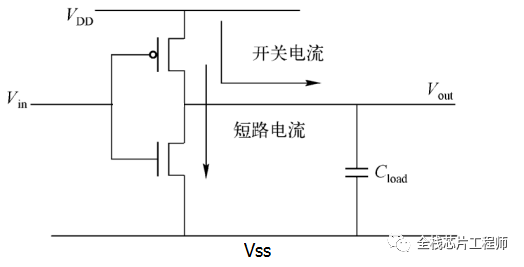

翻轉功耗(Switching power)

顧名思義,Switching power 就是對輸出電容進行充放電產生的功耗,其大小由電壓、翻轉率、負載電容決定。

漏電流功耗(Leakage Power)

即靜態功耗,隨著工藝節點演進到14nm、10nm、7nm等先進節點,Leakage Power的占比越來越高,Power gating的低功耗設計則十分關鍵。

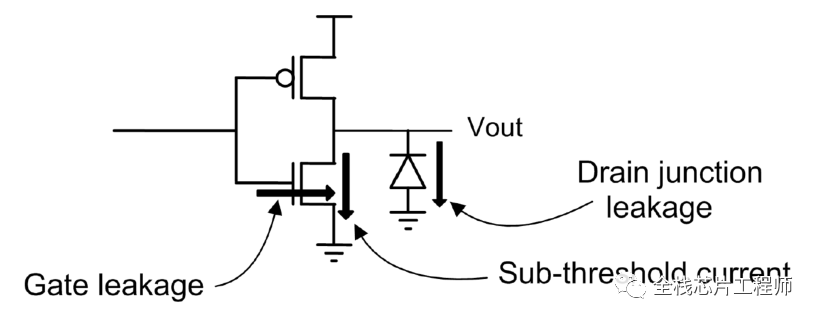

Leakage Power由以下幾個部分組成:

1. 亞閾值漏電流(Sub-threshold Leakage, ISUB)

晶體管邏輯關斷時,但溝道并沒完全截止,導致channel中仍存在少量導通電流。那么,可提高閾值電壓Vt,從而完全截止電流,但Vt越高,器件翻轉速度就降低,PPA中,Power變好了,Performance就變差了。

2. 柵極漏電流(Gate Leakage, Igate)

由于柵極氧化物隧穿和熱載流子注入,存在著通過氧化物流到襯底的電流。在65nm及以下節點工藝,柵極漏電流逐步增大到了亞閾值漏電流大小,因此,high-k高介電材料必須用以阻斷柵極漏電流。

3. 柵極感應漏電流(Gate Induced Drain Leakage, IGIDL)

Gate引入的結泄漏電流與其他泄漏電流相比通常都很小。

4. 反向偏置結泄漏(Reverse Bias Junction Leakage ,IREV)

由少數載流子漂移、耗盡區產生電子/空穴對引起,通常也很小。

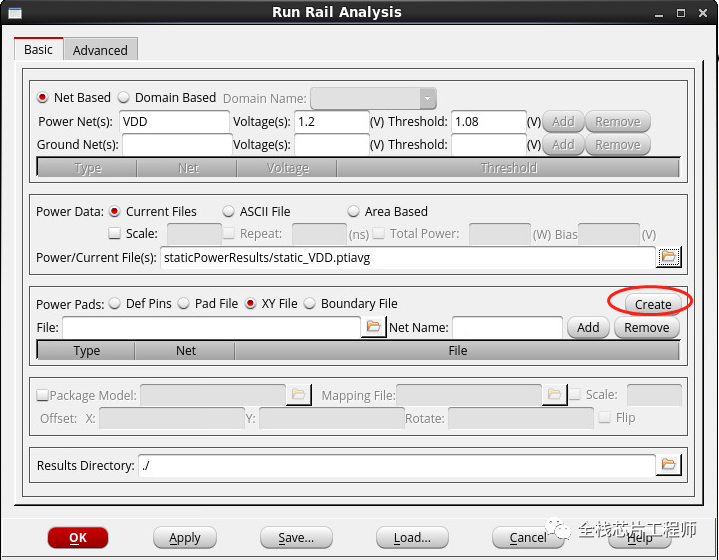

功耗分析完成后,工作目錄下將得到power.rpt、power.db和*.ptiavg文件,其中*.ptiavg、power.db文件將用于IR分析,此外還需要指定voltage source location來提供電源源點的位置。

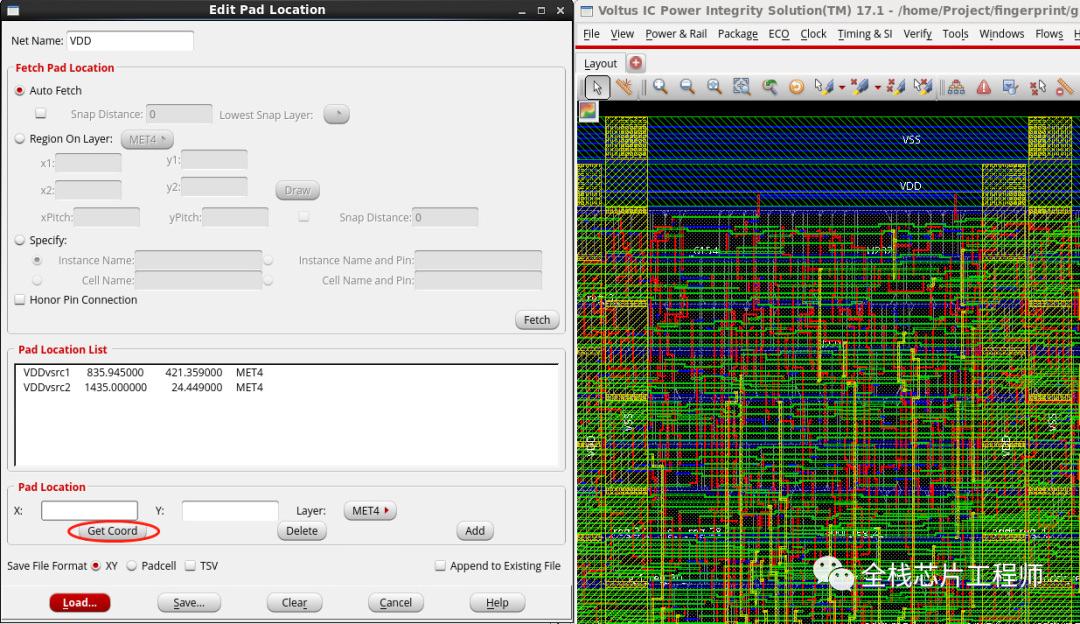

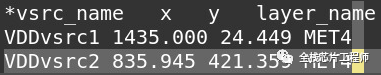

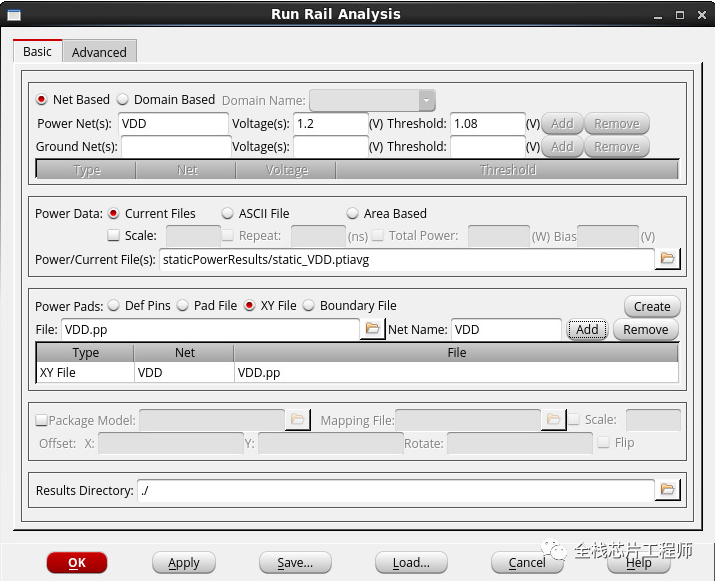

創建 Power Pads - XY File:

生成的 Power Pads - XY File如下:

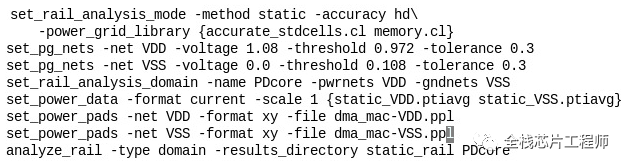

腳本流程參考如下:

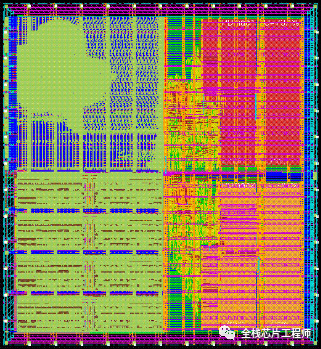

運行IR分析后,可得到相應報告及Rail analysis Plot:

審核編輯:劉清

-

NMOS

+關注

關注

3文章

283瀏覽量

34107 -

低功耗設計

+關注

關注

0文章

80瀏覽量

16120 -

漏電流

+關注

關注

0文章

252瀏覽量

16898 -

VDD

+關注

關注

1文章

310瀏覽量

32602 -

PMOS管

+關注

關注

0文章

82瀏覽量

6565

原文標題:芯片功耗的構成/IR分析

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

IR推出IR3588 ChiL數字控制IC及IR3552、IR3546

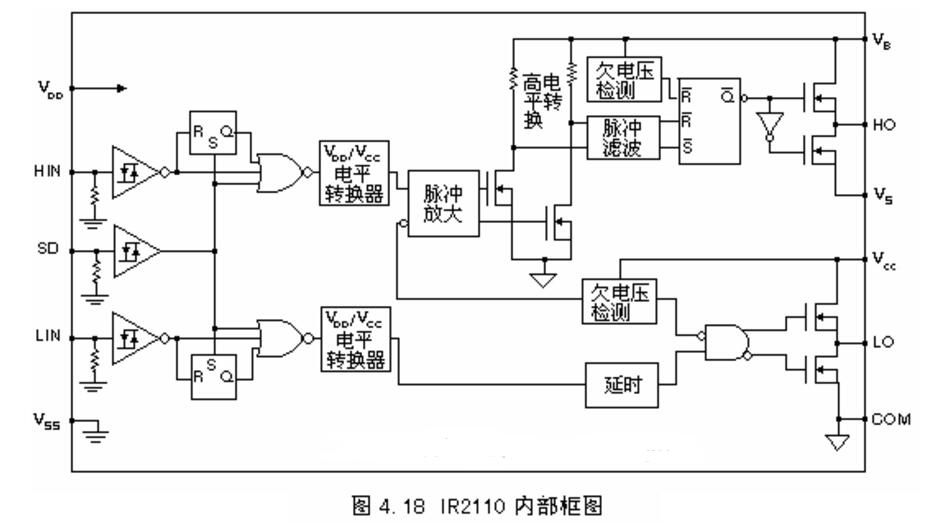

IR2110功率驅動集成芯片應用

新型電子鎮流器控制芯片IR2156

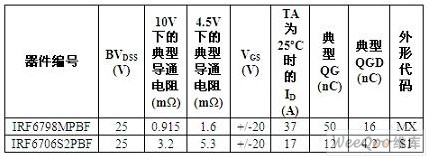

IR推出二款DirectFET MOSFET芯片組

MOSFET半橋驅動芯片IR2111

IR2130集成芯片在逆變器中的設計應用

ir2110驅動工作原理_IR2110的特點和內部功能圖及應用電路圖

低功耗藍牙芯片功耗主要來源的簡單分析

芯片功耗的IR分析

芯片功耗的IR分析

評論