在嵌入式系統(tǒng)中,板上通信接口是指用于將各種集成電路與其他外圍設(shè)備交互連接的通信通路或總線,以下內(nèi)容為常用板上通信接口。

I2C總線

I2C總線是一種同步、雙向、半雙工的兩線式串行接口總線,這里,半雙工的含義是指在任意給定的時(shí)刻,只有一個(gè)方向上是可以通信的。I2C總線由兩條總線組成:串行時(shí)鐘線SCL和串行數(shù)據(jù)線SDA。

SCL線:

負(fù)責(zé)產(chǎn)生同步時(shí)鐘脈沖。

SDA線:

負(fù)責(zé)在設(shè)備間傳輸串行數(shù)據(jù)。I2C總線是共享的總線系統(tǒng),因此可以將多個(gè)I2C設(shè)備連接到該系統(tǒng)上,連接到I2C總線上的設(shè)備既可以用作主設(shè)備,也可以用作從設(shè)備。

主設(shè)備負(fù)責(zé)控制通信,通過(guò)對(duì)數(shù)據(jù)傳輸進(jìn)行初始化/終止化,來(lái)發(fā)送數(shù)據(jù)并產(chǎn)生所需的同步時(shí)鐘脈沖。從設(shè)備則是等待來(lái)自主設(shè)備的命令,并響應(yīng)命令接收,主設(shè)備和從設(shè)備都可以作為發(fā)送設(shè)備或接收設(shè)備。

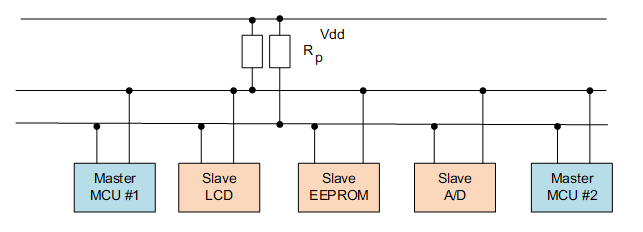

無(wú)論主設(shè)備是作為發(fā)送設(shè)備還是接收設(shè)備,同步時(shí)鐘信號(hào)都只能由主設(shè)備產(chǎn)生。在相同的總線上,I2C支持多個(gè)主設(shè)備的同時(shí)存在,下圖顯示了I2C總線上主設(shè)備和從設(shè)備的連接關(guān)系。

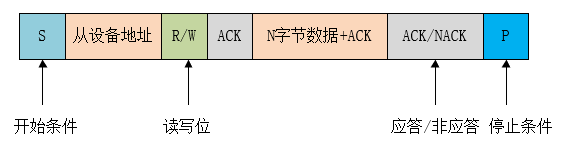

當(dāng)總線空閑時(shí),SDA 和SCL 都處于高電平狀態(tài),當(dāng)主機(jī)要和某個(gè)從機(jī)通訊時(shí),會(huì)先發(fā)送一個(gè)開(kāi)始條件,然后發(fā)送從機(jī)地址和讀寫(xiě)控制位,接下來(lái)傳輸數(shù)據(jù)(主機(jī)發(fā)送或者接收數(shù)據(jù)),數(shù)據(jù)傳輸結(jié)束時(shí)主機(jī)會(huì)發(fā)送停止條件,傳輸?shù)拿總€(gè)字節(jié)為8 位,高位在前,低位在后。

開(kāi)始條件:

SCL 為高電平時(shí),主機(jī)將SDA 拉低,表示數(shù)據(jù)傳輸即將開(kāi)始。

從機(jī)地址:

主機(jī)發(fā)送的第一個(gè)字節(jié)為從機(jī)地址,高7 位為地址,最低位為R/W 讀寫(xiě)控制位,1 表示讀操作,0 表示寫(xiě)操作。一般從機(jī)地址有7 位地址模式和10 位地址模式兩種,如果是10 位地址模式,第一個(gè)字節(jié)的頭7 位是11110XX 的組合,其中最后兩位(XX)是10 位地址的兩個(gè)最高位,第二個(gè)字節(jié)為10 位從機(jī)地址的剩下8 位,如下圖所示:

應(yīng)答信號(hào):

每傳輸完成一個(gè)字節(jié)的數(shù)據(jù),接收方就需要回復(fù)一個(gè)ACK,寫(xiě)數(shù)據(jù)時(shí)由從機(jī)發(fā)送ACK,讀數(shù)據(jù)時(shí)由主機(jī)發(fā)送ACK,當(dāng)主機(jī)讀到最后一個(gè)字節(jié)數(shù)據(jù)時(shí),可發(fā)送NACK然后跟停止條件。

數(shù)據(jù):

從機(jī)地址發(fā)送完后可能會(huì)發(fā)送一些指令,依從機(jī)而定,然后開(kāi)始傳輸數(shù)據(jù),由主機(jī)或者從機(jī)發(fā)送,每個(gè)數(shù)據(jù)為8 位,數(shù)據(jù)的字節(jié)數(shù)沒(méi)有限制。

重復(fù)開(kāi)始條件:

在一次通信過(guò)程中,主機(jī)可能需要和不同的從機(jī)傳輸數(shù)據(jù)或者需要切換讀寫(xiě)操作時(shí),主機(jī)可以再發(fā)送一個(gè)開(kāi)始條件。

停止條件:

在SDA 為低電平時(shí),主機(jī)將SCL 拉高并保持高電平,然后在將SDA 拉高,表示傳輸結(jié)束。

SPI總線

SPI總線是同步、雙向、全雙工的4線式串行接口總線,SPI是由“單個(gè)主設(shè)備+多個(gè)從設(shè)備”構(gòu)成的系統(tǒng)。需要說(shuō)明的是:在系統(tǒng)中,只要任意時(shí)刻只有一個(gè)主設(shè)備是處于激活狀態(tài)的,就可以存在多個(gè)SPI主設(shè)備。常運(yùn)用于EEPROM、FLASH、實(shí)時(shí)時(shí)鐘、AD轉(zhuǎn)換器、數(shù)字信號(hào)處理器和數(shù)字信號(hào)解碼器之間實(shí)現(xiàn)通信。為了實(shí)現(xiàn)通信,SPI共有4條信號(hào)線,分別是:

主設(shè)備出、從設(shè)備入

(Master Out Slave In,MOSI):由主設(shè)備向從設(shè)備傳輸數(shù)據(jù)的信號(hào)線,也稱為從設(shè)備輸入(Slave Input/Slave Data In,SI/SDI)。

主設(shè)備入、從設(shè)備出

(Master In Slave Out,MISO):由從設(shè)備向主設(shè)備傳輸數(shù)據(jù)的信號(hào)線,也稱為從設(shè)備輸出(Slave Output/Slave Data Out,SO/SDO)。

串行時(shí)鐘

(Serial Clock,SCLK):傳輸時(shí)鐘信號(hào)的信號(hào)線。

從設(shè)備選擇

(Slave Select,SS):用于選擇從設(shè)備的信號(hào)線,低電平有效。

SPI使用方法:

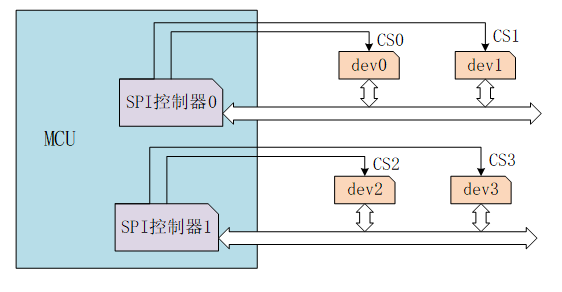

上圖所示芯片有2 個(gè)SPI 控制器,SPI 控制器對(duì)應(yīng)SPI 主設(shè)備,每個(gè)SPI 控制器可以連接多個(gè)SPI從設(shè)備。掛載在同一個(gè)SPI 控制器上的從設(shè)備共享3 個(gè)信號(hào)引腳:SCK、MISO、MOSI,但每個(gè)從設(shè)備的CS 引腳是獨(dú)立的.

主設(shè)備通過(guò)控制CS 引腳對(duì)從設(shè)備進(jìn)行片選,一般為低電平有效,任何時(shí)刻,一個(gè)SPI 主設(shè)備上只有一個(gè)CS 引腳處于有效狀態(tài),與該有效CS 引腳連接的從設(shè)備此時(shí)可以與主設(shè)備通信。所以,SPI通信方式可以使用“一主多從”的結(jié)構(gòu)進(jìn)行通信,每個(gè)連接到總線上的器件都有唯一的地址,主設(shè)備啟動(dòng)數(shù)據(jù)傳輸并產(chǎn)生時(shí)鐘信號(hào),從設(shè)備被主設(shè)備尋址,同一時(shí)刻只允許有一個(gè)主設(shè)備。

從設(shè)備的時(shí)鐘由主設(shè)備通過(guò)SCLK 提供,MOSI、MISO 則基于此脈沖完成數(shù)據(jù)傳輸。SPI 的工作時(shí)序模式由CPOL和CPHA之間的相位關(guān)系決定,CPOL 表示時(shí)鐘信號(hào)的初始電平的狀態(tài),CPOL 為0 表示時(shí)鐘信號(hào)初始狀態(tài)為低電平,為1 表示時(shí)鐘信號(hào)的初始電平是高電平。

CPHA 表示在哪個(gè)時(shí)鐘沿采樣數(shù)據(jù),CPHA 為0 表示在首個(gè)時(shí)鐘變化沿采樣數(shù)據(jù),而CPHA 為1 則表示在第二個(gè)時(shí)鐘變化沿采樣數(shù)據(jù)。根據(jù)CPOL 和CPHA 的不同組合共有4 種工作時(shí)序模式:CPOL=0,CPHA=0、CPOL=0,CPHA=1、CPOL=1,CPHA=0、CPOL=1,CPHA=1。

UART通用異步收發(fā)傳輸器,UART 作為異步串口通信協(xié)議的一種,工作原理是將傳輸數(shù)據(jù)的每個(gè)字符一位接一位地傳輸,在應(yīng)用程序開(kāi)發(fā)過(guò)程中使用頻率較高的數(shù)據(jù)總線。

基于UART的數(shù)據(jù)傳輸是異步形式的串行數(shù)據(jù)傳輸,基于UART的串行數(shù)據(jù)傳輸不需要使用時(shí)鐘信號(hào)來(lái)同步傳輸?shù)陌l(fā)送端和接收端,而是依賴于發(fā)送設(shè)備和接收設(shè)備之間預(yù)定義的配置。

對(duì)于發(fā)送設(shè)備和接收設(shè)備來(lái)說(shuō),兩者的串行通信配置(波特率、單位字的位數(shù)、奇偶校驗(yàn)、起始位數(shù)與結(jié)束位、流量控制)應(yīng)該設(shè)置為完全相同。通過(guò)在數(shù)據(jù)流中插入特定的比特序列,可以指示通信的開(kāi)始與結(jié)束,當(dāng)發(fā)送一個(gè)字節(jié)數(shù)據(jù)的時(shí)候,需要在比特流的開(kāi)頭加上起始位,并在比特流的末尾加上結(jié)束位,數(shù)據(jù)字節(jié)的最低位緊接在起始位之后。

UART 串口的特點(diǎn)是將數(shù)據(jù)一位一位地順序傳送,只要2 根傳輸線就可以實(shí)現(xiàn)雙向通信,一根線發(fā)送數(shù)據(jù)的同時(shí)用另一根線接收數(shù)據(jù)。UART 串口通信有幾個(gè)重要的參數(shù),分別是波特率、起始位、數(shù)據(jù)位、停止位和奇偶檢驗(yàn)位,對(duì)于兩個(gè)使用UART 串口通信的端口,這些參數(shù)必須匹配,否則通

起始位:

表示數(shù)據(jù)傳輸?shù)拈_(kāi)始,電平邏輯為“0” 。

數(shù)據(jù)位:

可能值有5、6、7、8、9,表示傳輸這幾個(gè)bit 位數(shù)據(jù)。一般取值為8,因?yàn)橐粋€(gè)ASCII 字符值為8 位。

奇偶校驗(yàn)位:

用于接收方對(duì)接收到的數(shù)據(jù)進(jìn)行校驗(yàn),校驗(yàn)“1” 的位數(shù)為偶數(shù)(偶校驗(yàn)) 或奇數(shù)(奇校驗(yàn)),以此來(lái)校驗(yàn)數(shù)據(jù)傳送的正確性,使用時(shí)不需要此位也可以。

停止位:

表示一幀數(shù)據(jù)的結(jié)束。電平邏輯為“1”。

波特率:

串口通信時(shí)的速率,它用單位時(shí)間內(nèi)傳輸?shù)亩M(jìn)制代碼的有效位(bit) 數(shù)來(lái)表示,其單位為每秒比特?cái)?shù)bit/s(bps),常見(jiàn)的波特率值有4800、9600、14400、38400、115200 等,數(shù)值越大數(shù)據(jù)傳輸?shù)脑娇欤ㄌ芈蕿?15200 表示每秒鐘傳輸115200 位數(shù)據(jù)。

1-Wire接口

1-Wire接口是由Maxim Dallas半導(dǎo)體公司開(kāi)發(fā)的異步半雙工通信協(xié)議,也稱為Dallas 1-Wire?協(xié)議,其中,按照主-從通信模型,只使用單條信號(hào)線DQ實(shí)現(xiàn)通信。1-Wire總線的一個(gè)重要特征在于,該總線允許在信號(hào)線上傳輸能量,1-Wire接口支持在總線上連接單個(gè)主設(shè)備以及一個(gè)或多個(gè)從設(shè)備。

并行接口

板上并行接口通常用于系統(tǒng)與外圍設(shè)備之間的通信,其中,外圍設(shè)備通過(guò)存儲(chǔ)器映射到系統(tǒng)的主控端。

只要嵌入式系統(tǒng)的主控處理器/控制器含有并行總線,支持并行總線的設(shè)備就可以直接連接到該總線系統(tǒng)上。外圍設(shè)備與主控端之間具有控制信號(hào)接口,可以控制并行總線上的數(shù)據(jù)通信,這里,通信的控制信號(hào)包括讀/寫(xiě)信號(hào)和設(shè)備選擇信號(hào)。

一般說(shuō)來(lái),外圍設(shè)備具有設(shè)備選擇線,只有當(dāng)主控處理器選通該線的時(shí)候,該設(shè)備才是有效的。數(shù)據(jù)傳輸?shù)姆较蚩梢允菑闹骺囟说酵鈬O(shè)備,也可以是從外圍設(shè)備到主控端,這是通過(guò)讀和寫(xiě)控制信號(hào)線進(jìn)行控制的,只有主控處理器能夠控制讀控制信號(hào)和寫(xiě)控制信號(hào)。

一般說(shuō)來(lái),外圍設(shè)備通過(guò)存儲(chǔ)器映射到主控處理器,從而可以訪問(wèn)分配的地址范圍,此時(shí),設(shè)備需要使用地址譯碼電路來(lái)產(chǎn)生芯片選擇信號(hào)。當(dāng)處理器選擇的地址位于設(shè)備指定范圍內(nèi)的時(shí)候,譯碼電路對(duì)芯片選擇線進(jìn)行觸發(fā),從而激活設(shè)備。

然后,處理器可以使能相應(yīng)的控制線(分別是RD與WD),從而由設(shè)備讀出數(shù)據(jù),或者是向設(shè)備寫(xiě)入數(shù)據(jù)。為了實(shí)現(xiàn)并行通信,系統(tǒng)需要嚴(yán)格遵循時(shí)序規(guī)范。前面已經(jīng)提到過(guò),并行通信是由主控處理器啟動(dòng)的。如果某外圍設(shè)備想要對(duì)通信進(jìn)行初始化,那么可以向處理器發(fā)出中斷,告知相關(guān)信息。

為了實(shí)現(xiàn)上述功能,設(shè)備的中斷線需要連接到處理器的中斷線上,并且主控處理器需要觸發(fā)相應(yīng)的中斷。需要說(shuō)明的是,主控處理器的數(shù)據(jù)總線寬度決定了并行接口的寬度,可以是4位、8位、16位、32位、64位等,設(shè)備支持的總線寬度應(yīng)該與主控處理器完全相同。

-

集成電路

+關(guān)注

關(guān)注

5381文章

11385瀏覽量

360858 -

嵌入式系統(tǒng)

+關(guān)注

關(guān)注

41文章

3567瀏覽量

129227 -

通信接口

+關(guān)注

關(guān)注

3文章

234瀏覽量

30963

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

幾種常用單片機(jī)之間的通信方式

幾種常用單片機(jī)之間的通信方式

常用板上通信接口都有哪些呢

通信接口有哪些_幾種常見(jiàn)的通信接口

plc常用的串行通信接口標(biāo)準(zhǔn)

嵌入式開(kāi)發(fā)中常用的幾種通信接口總結(jié)

常用的幾種通信接口解析

常用的幾種通信接口解析

評(píng)論