EtherCAT現場總線協議是由德國倍福公司在2003年提出的,該通訊協議拓撲結構十分靈活,數據傳輸速度快,同步特性好,可以形成各種網絡拓撲結構。

1、EtherCAT簡介

EtherCAT是一個開放架構,以以太網為基礎的現場總線系統,其名稱的CAT為控制自動化技術(Control Automation Technology)字首的縮寫。EtherCAT是確定性的工業以太網,最早是由德國的Beckhoff公司研發。

EtherCAT主站可以用軟件,在標準的以太網媒體接入控制器中實現。許多供應商有提供在不同操作系統下的代碼,也有許多開源軟件或共享軟件。

EtherCAT從站需要特殊的EtherCAT從站控制器,才能實現飛速傳輸(processing on the fly)的技術。EtherCAT從站控制器可以用FPGA來實現,且已有現成的代碼,此控制器也可以用ASIC來實現。

2、EtherCAT特性

A. 完全符合以太網標準:

EtherCAT是對傳統的以太網協議進行修改,因此可以與其他以太網協議并存于統一總線。EtherCAT網絡中也可以使用普通的以太網設備,例如以太網線、以太網卡、交換機、路由器等設備。此外,任何具有標準以太網控制器的設備都可以作為EtherCAT 主站,包括PC計算機、帶有以太網控制器的嵌入式設備。

B.卓越的性能:

EtherCAT是基于以太網技術,數據傳輸速度可以達到100Mbit/s,是最快的工業以太網技術。EtherCAT最大利用以太網帶寬進行數據傳輸,有效數據利用率高,可達90%以上。另外EtherCAT數據幀處理的實時性很高,數據刷新周期小于100us,滿足對實時性要求高的場合。EtherCAT使用高精度的分布式時鐘,能保證各個從站節點設備的同步精度小于1us。

C. 簡單、低成本:

EtherCAT結構簡單,而無需交換機或集線器,復雜功能的節點設備或簡單的I/O節點都可以用作EtherCAT從站。此外EtherCAT在網絡拓撲方面沒有限制,支持多種網絡拓撲結構,如線型、星型、樹型拓撲結構,以及各種拓撲結構的組合,從而使得設備連接非常靈活。

3、BECKHOFFESC IP Core For AMD FPGAs Release 3.00

概述:

BECKHOFFEtherCAT IP核是一個可配置的EtherCAT從控制器(ESC)。它負責EtherCAT通信,作為EtherCAT現場總線和應用程序之間的接口。

A、EtherCATIP核是作為一個可配置的IP,各項功能可以自定義;

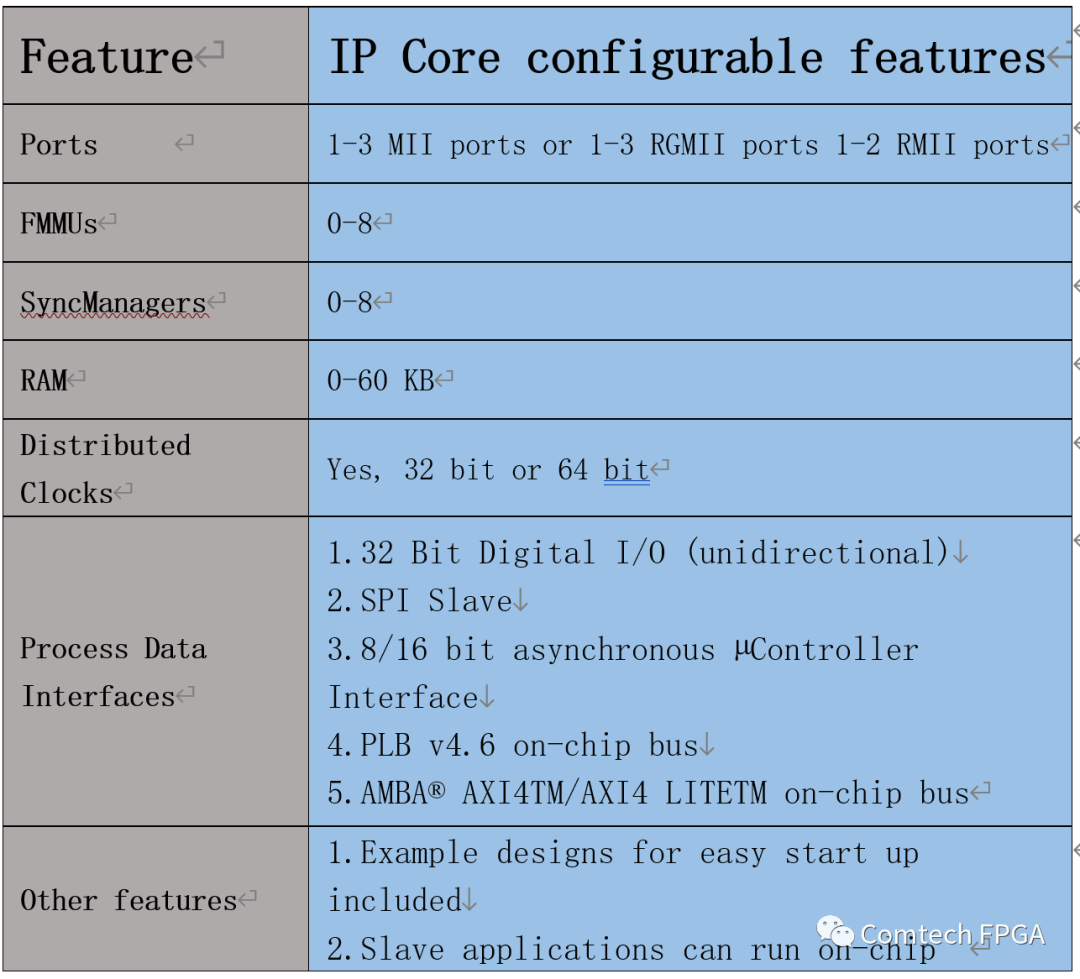

BECKHOFFIP Core Main Features : Table 1

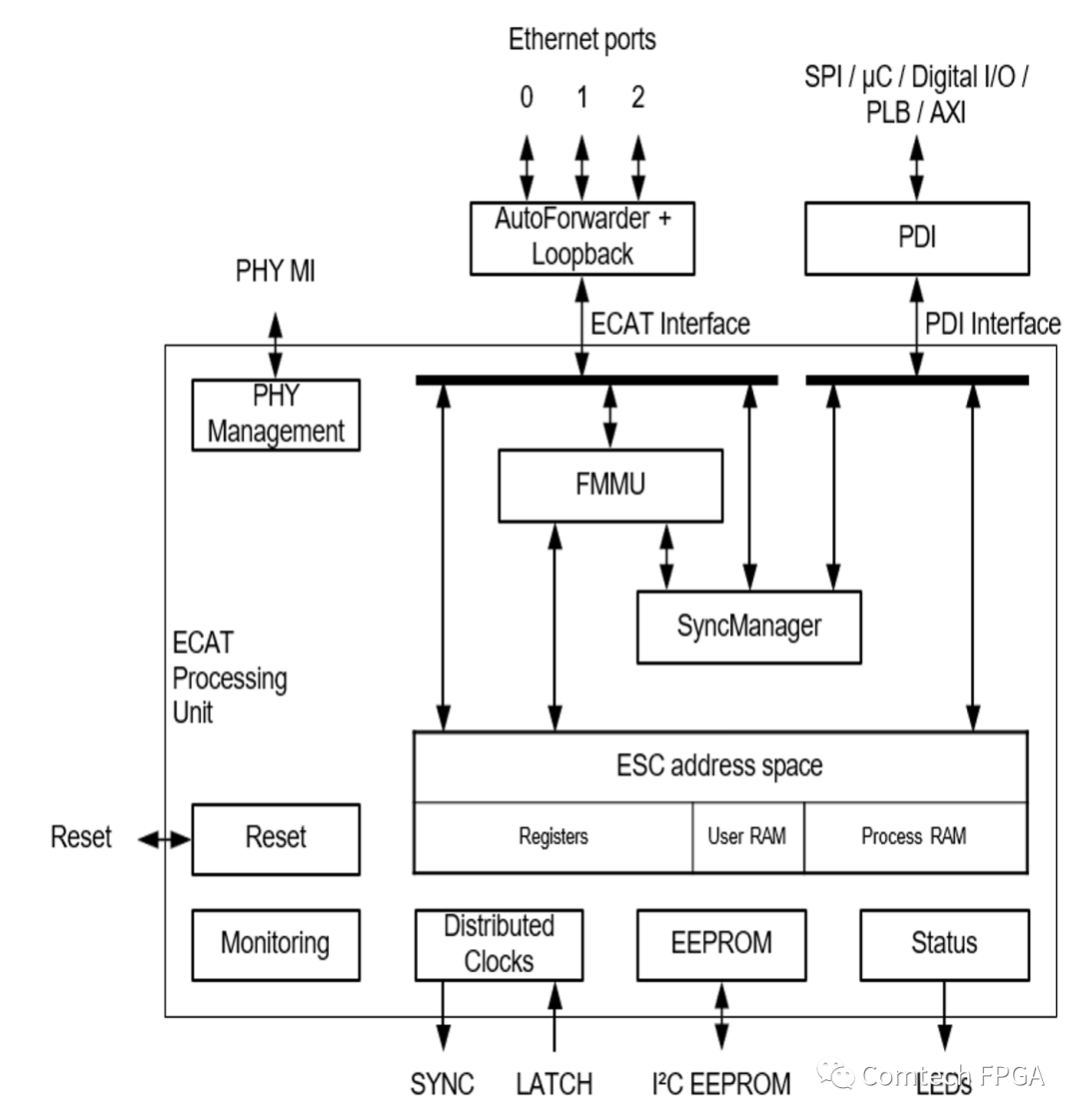

B、EtherCATIP Core Block Diagram;

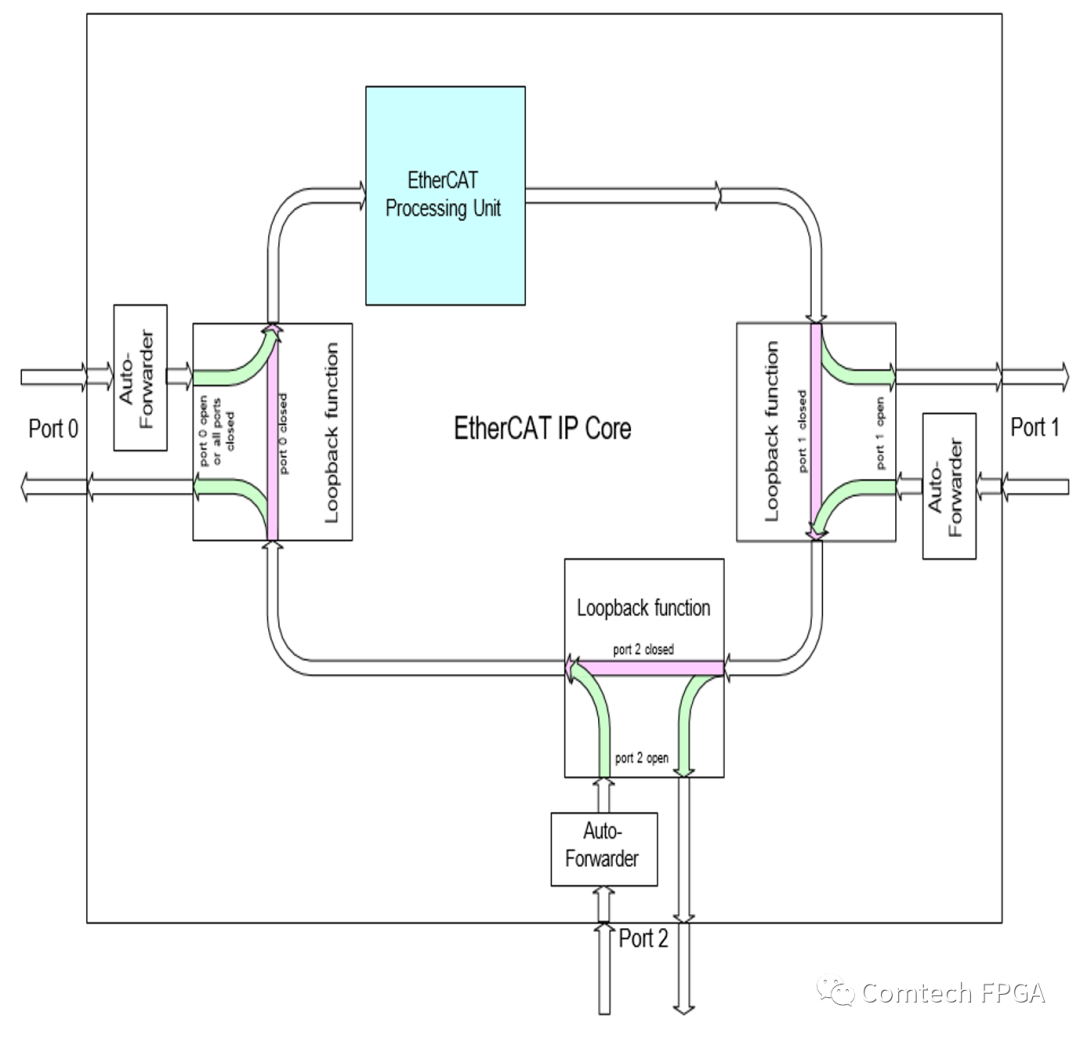

C、端口數據處理順序;

????

????

a、0→EtherCAT Processing Unit→1 / 1→2 / 2→0

b、0→EtherCATProcessing Unit→0

c、0→EtherCATProcessing Unit→1 / 1→0

4、BECKHOFFESC IP使用流程:

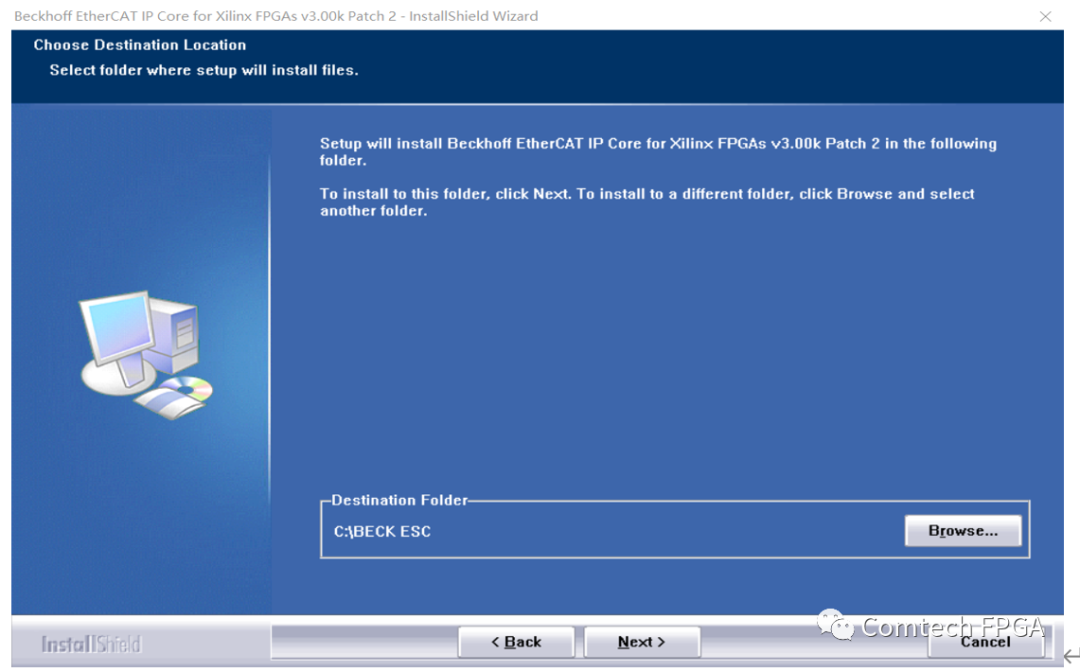

A. 直接安裝,英文目錄;

ISE14.3 - 14.7

B. 安裝過程中提示要加入VENDER ID ,直接跳過 ,需要申請License才能綜合;

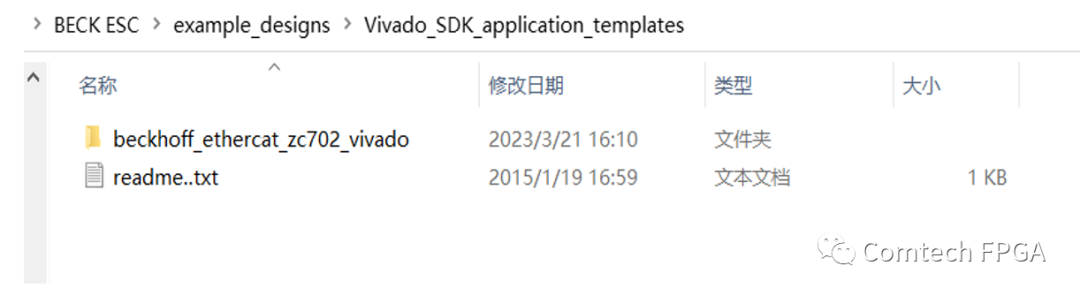

C. 安裝完目錄截圖如下;

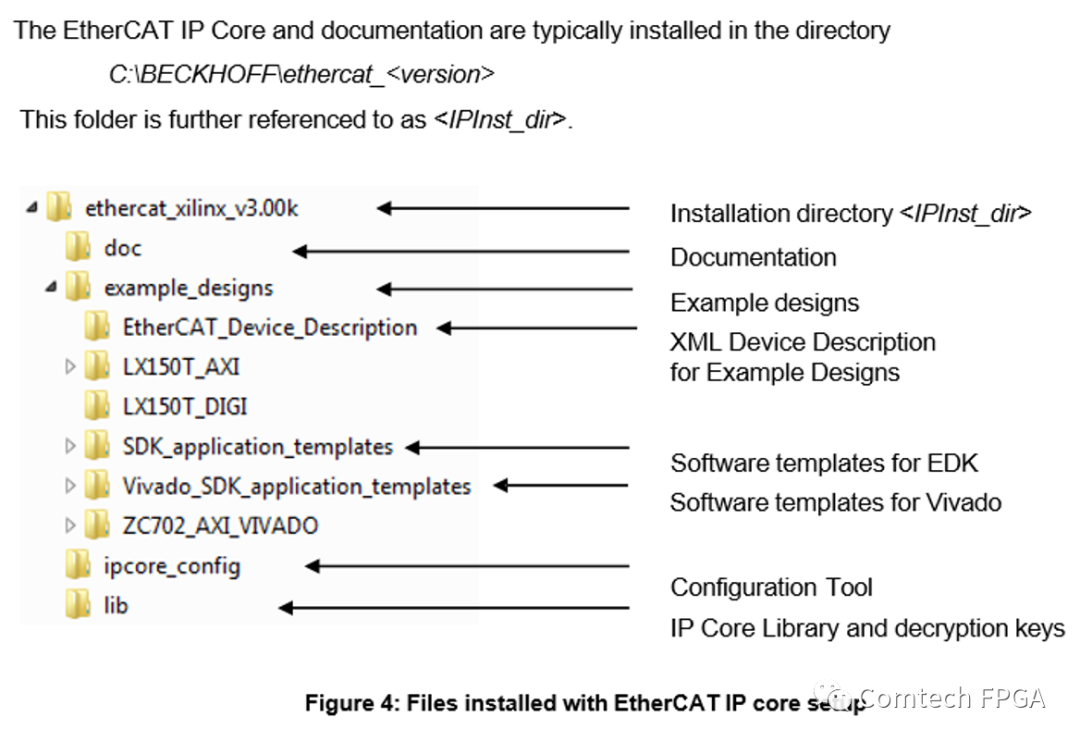

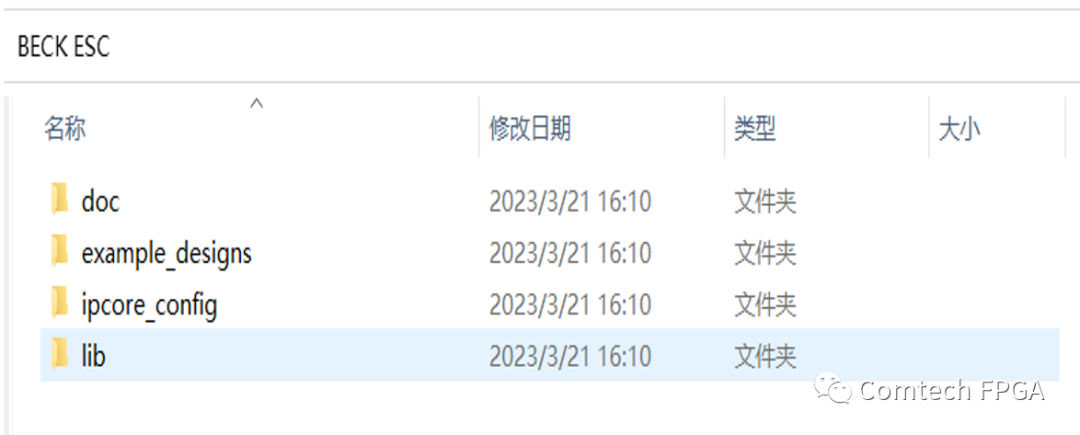

D. 安裝完后,文件截圖以下;

EtherCATIP Core (encrypted VHDL library)

Decryptionkeys for encrypted EtherCAT IP Core

IPCore Configuration Tool (IPCore_Config.exe)

Exampledesigns

E. 支持的AMD 器件包括SOC器件和純FPGA器件;

F. 支持的軟件版本:

Vivado2013.1 - 2013.4, 2014.1 - 2019.3

SDK

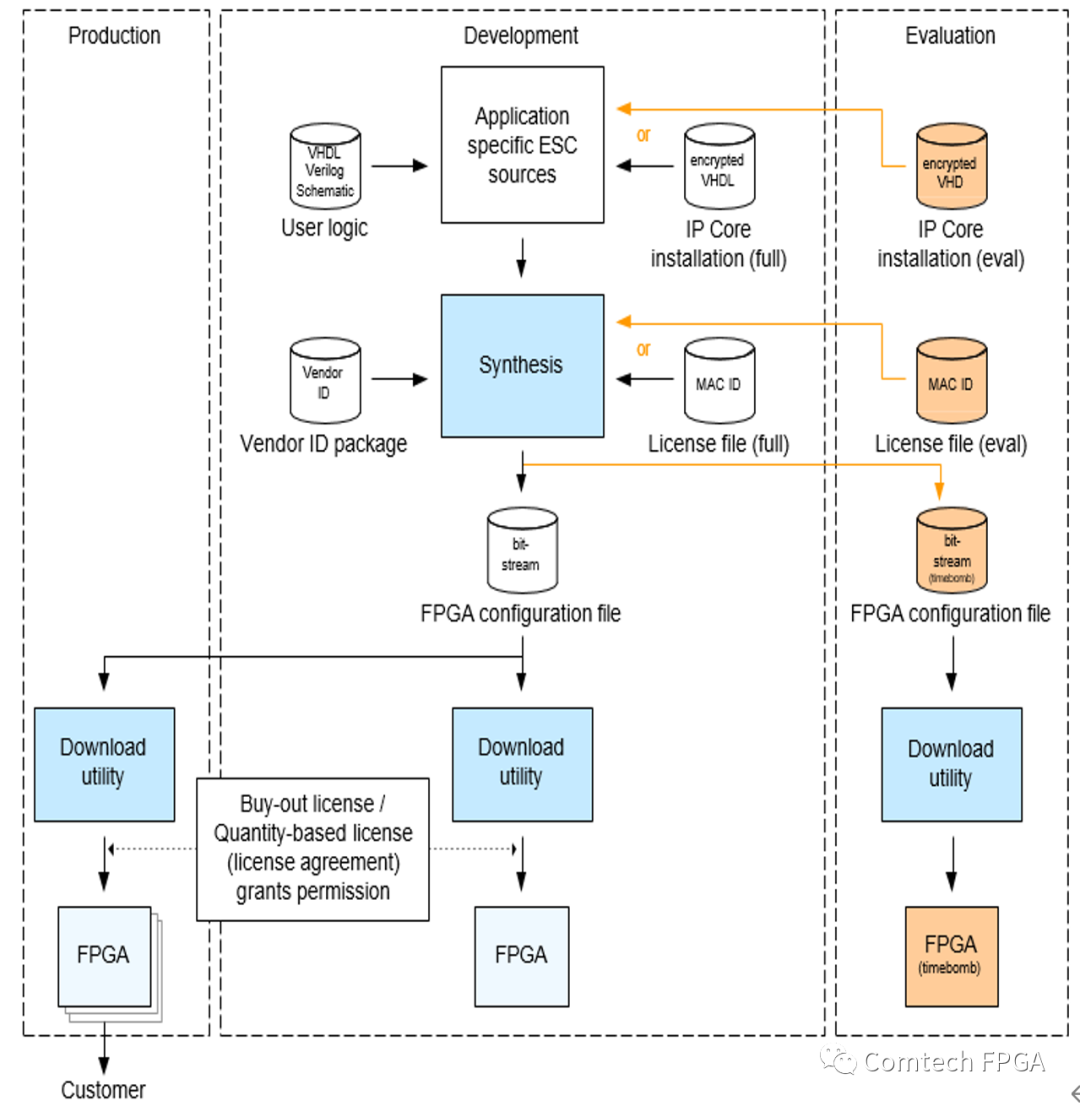

5、設計流程圖:

6、詳細過程如下:

A. 雙擊Ipcore_config目錄下的IPCore_Config.exe;

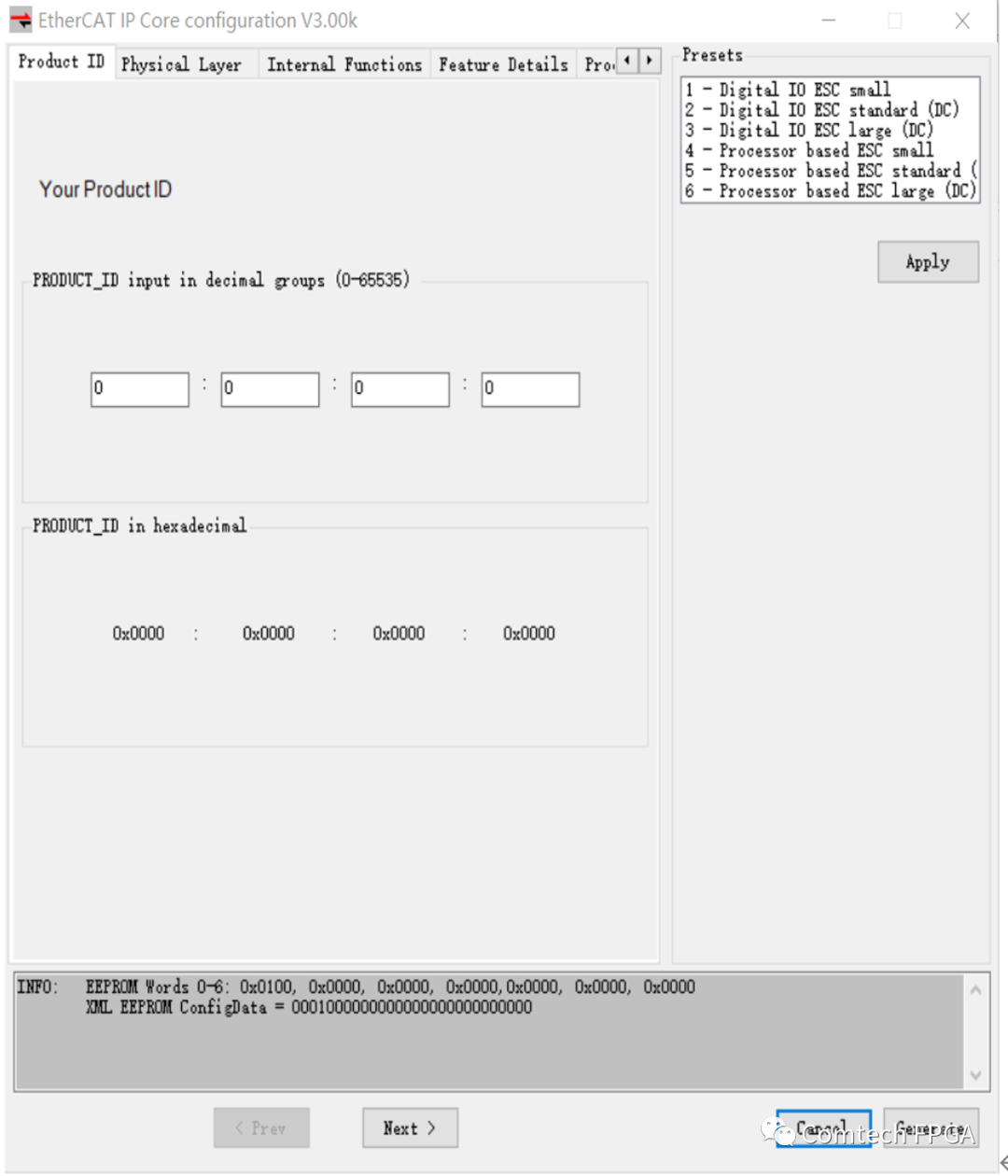

B. 填寫Porduct ID;

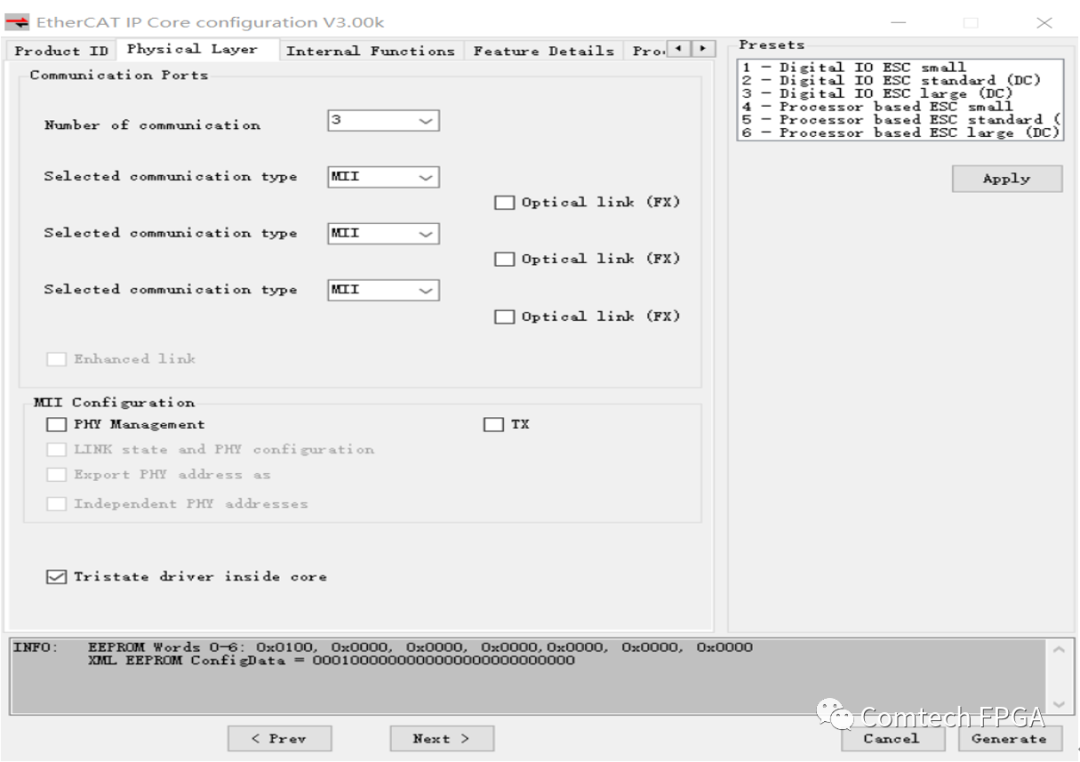

C. 物理層的一些配置:例如幾路端口,PHY的接口類型,MII/RGMII/RMII,由客戶的PHY芯片決定;

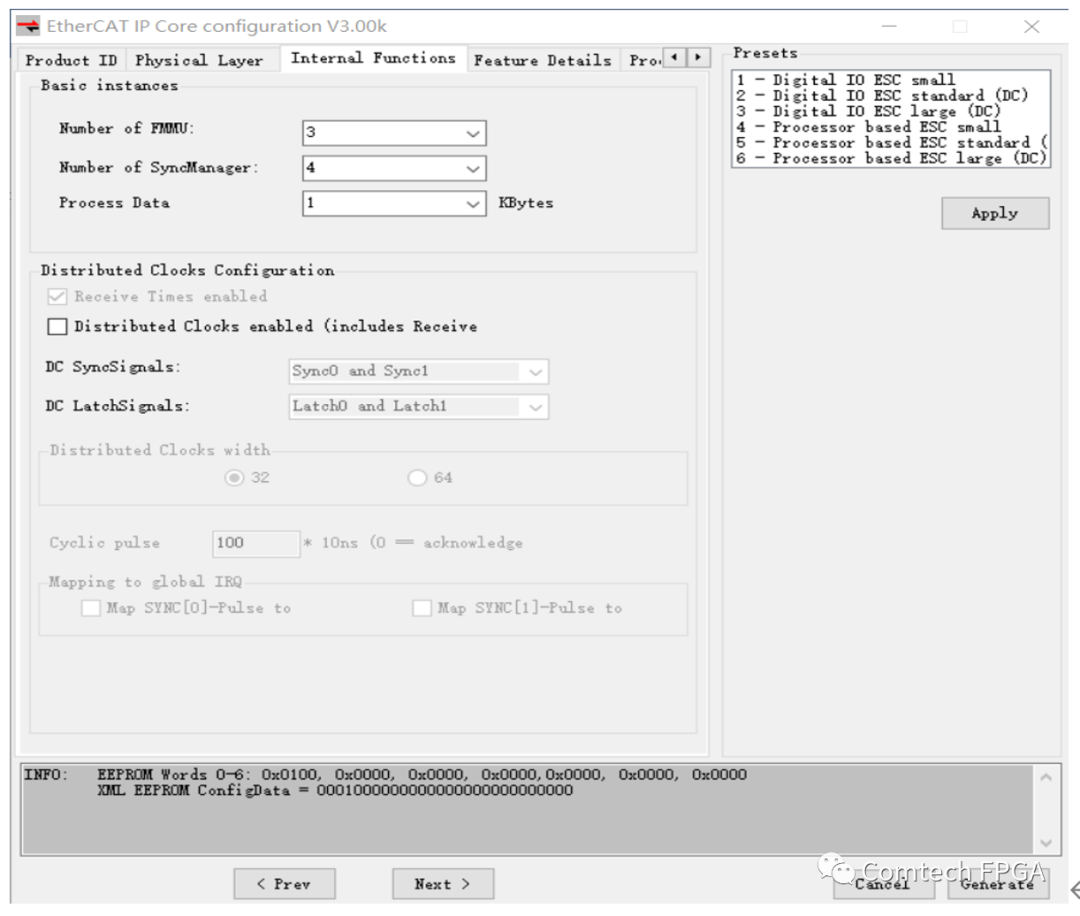

D. 網絡功能的配置;

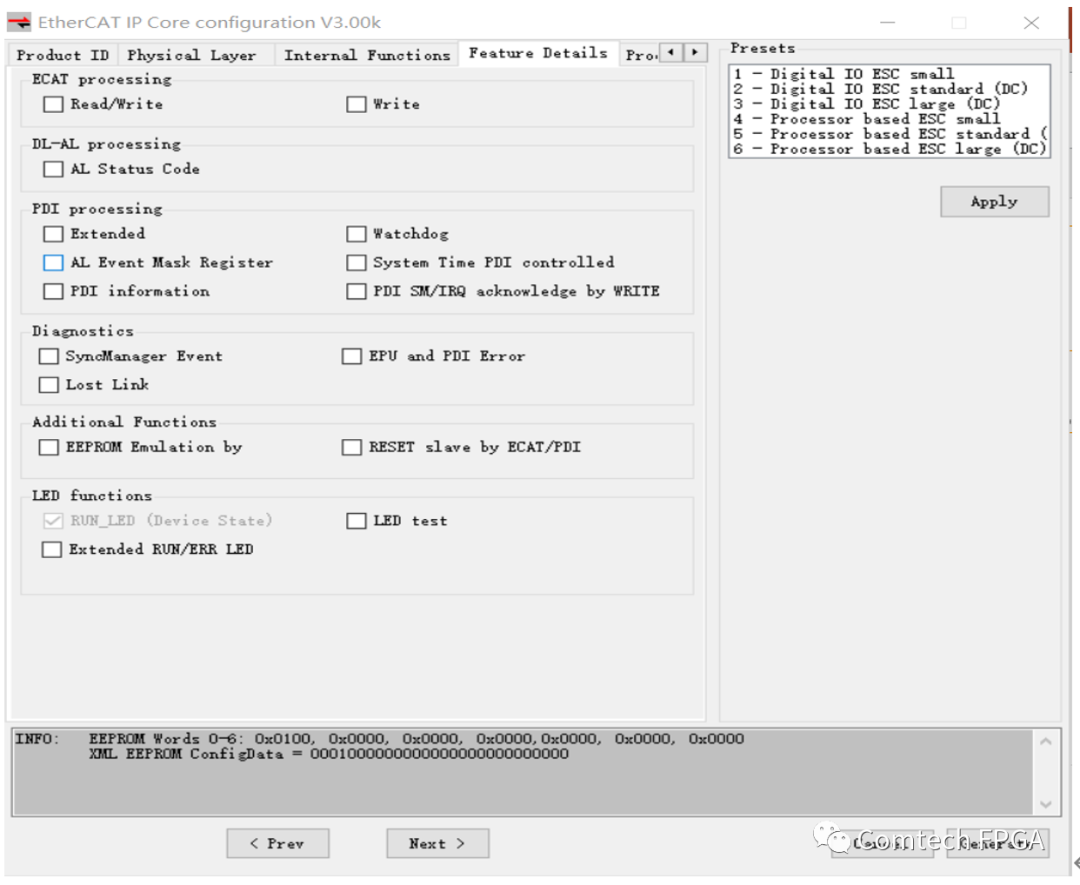

E. ECATProcessing /PDI Processing/LED status;

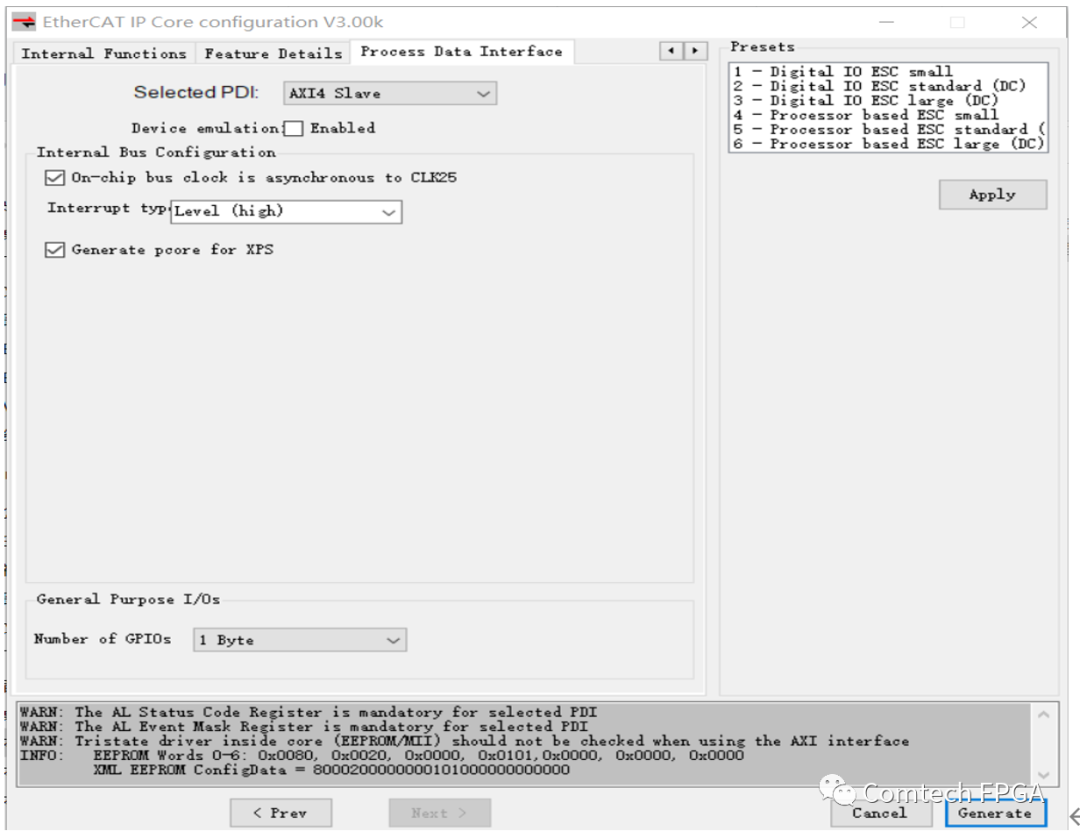

F. ESC跟CPU的接口;

G. 最后一步Generate;

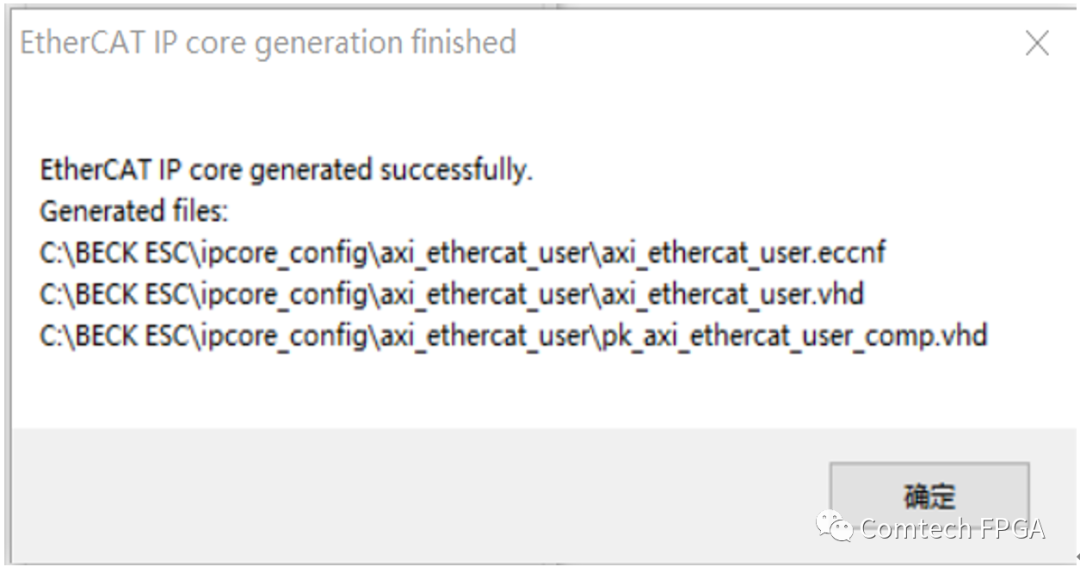

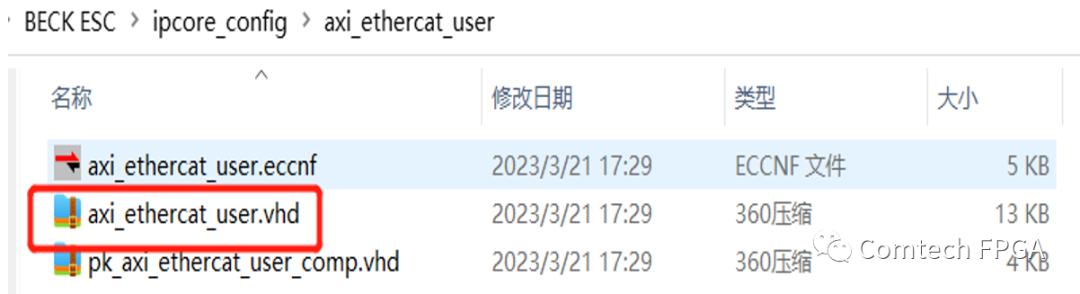

H. 生成的文件如下,不同的配置生成的文件有差異;

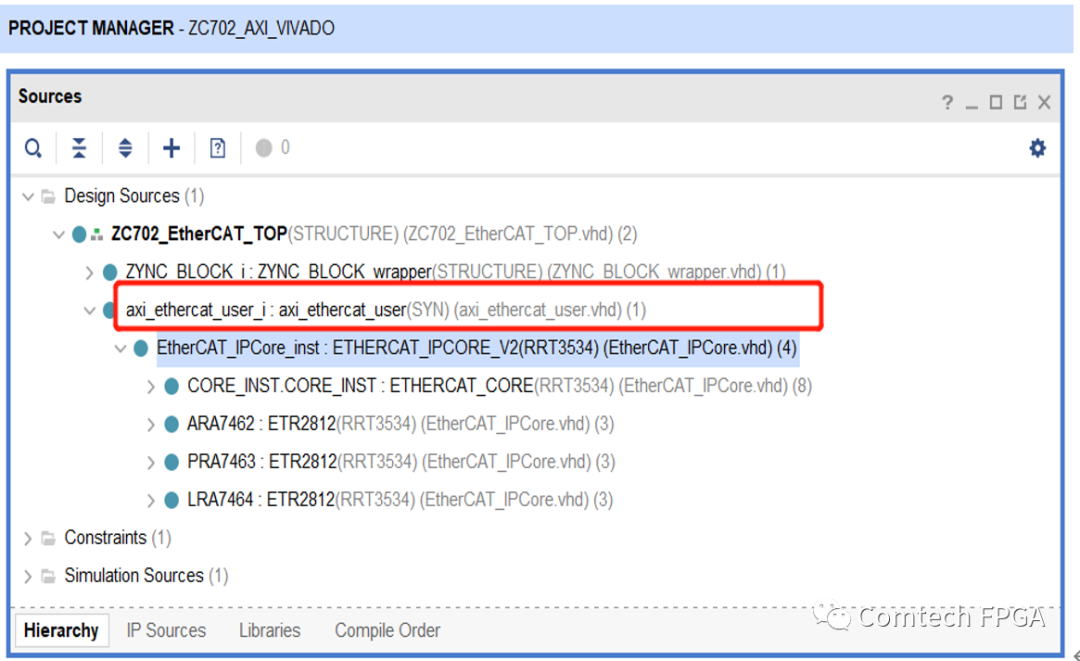

J. 把生成的文件加入到工程中,截圖如下;

K. 導入License,如果沒有授權的License,無法綜合;

I. 綜合、實現后生成BitStream并將其下載到FPGA。使用EtherCAT主機與EtherCAT從機通信;

J. EtherCAT從站需要SII EEPROM(或其他非易失性存儲器),其中包含用于設備識別的EtherCAT從站信息(ESI);

M. 打開SDK,添加應用文件,細節參考readme.txt;

N. 注意事項:

ESCIP 和 PHY 不能一起復位,IP核復位后,再讓PHY復位。

ESC in resetstate → PHY disabled

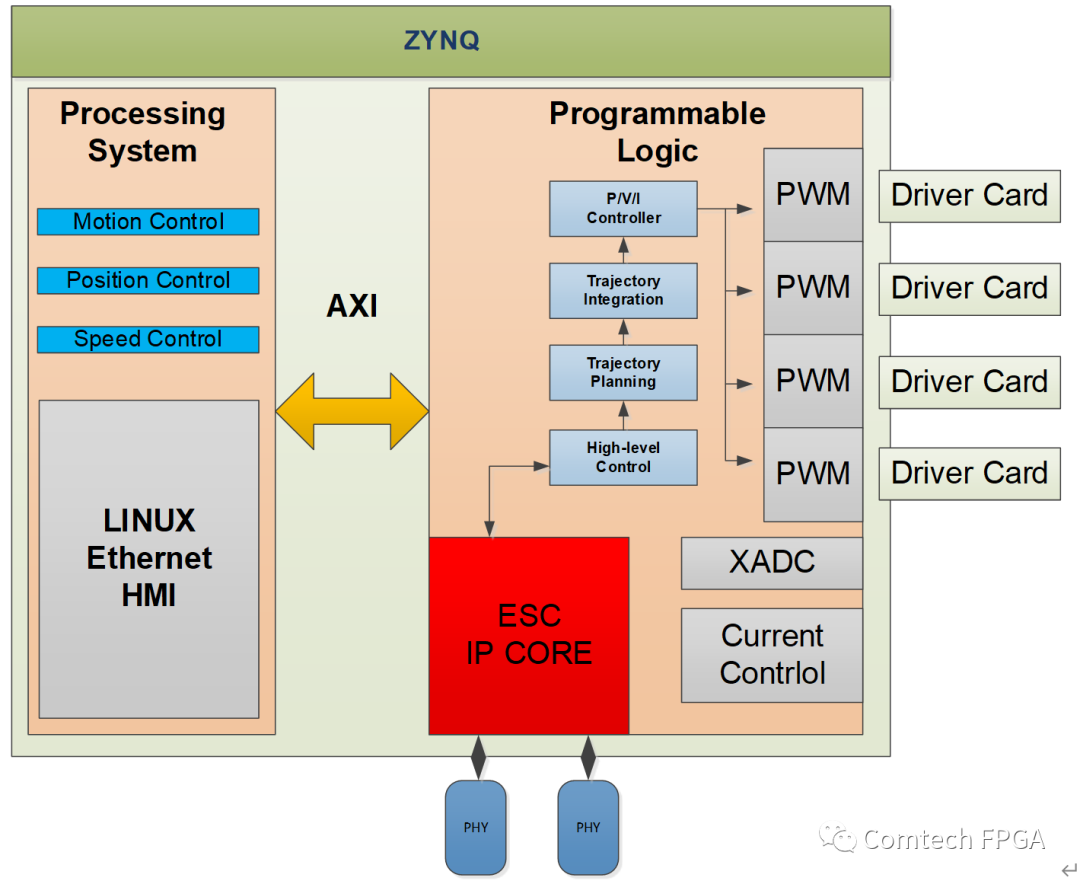

8、AMD推薦方案:

ZYNQ7000 SOC器件+Ethernet PHY(2x100Base-T)

9、基于ZYNQ的ESC方案框圖:

10、AMD ZYNQ 優勢:

A. PS端:ARM Cortex-A9 766MHZ,可實現超強的性能及復雜的應用;

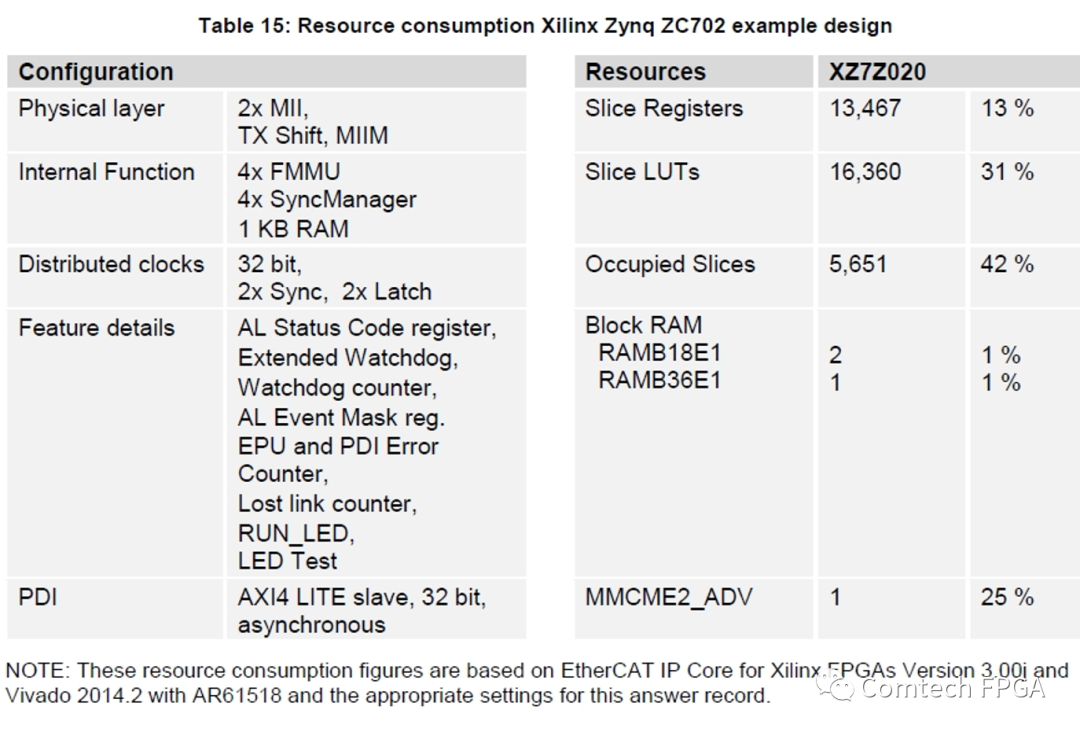

B. PL端:EtherCATSLAVE Controller IP容易布署,消耗相應的邏輯資源;

C. BECKOFFEtherCAT SLAVE Controller IP 應用廣,經過市場驗證,性能穩定;

D. BECKOFFEtherCAT SLAVE Controller IP 在AMD多個平臺上進行過優化,量身定 制。同等功能,相比于其它廠商的平臺,消耗資源少5%-10%。

11、EtherCAT Resource :

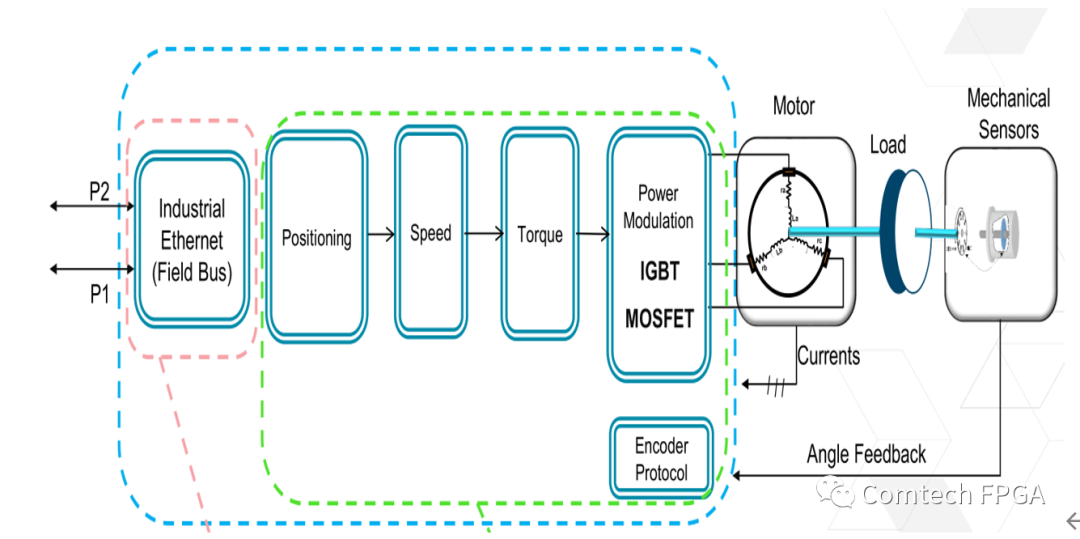

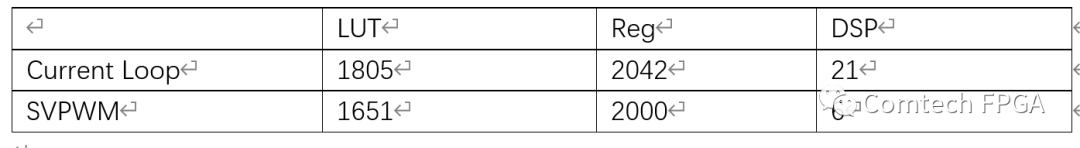

12、一路電流環+SVPWM:

審核編輯:劉清

-

FPGA

+關注

關注

1626文章

21677瀏覽量

601990 -

控制器

+關注

關注

112文章

16213瀏覽量

177465 -

以太網

+關注

關注

40文章

5384瀏覽量

171153 -

EtherCAT總線

+關注

關注

5文章

71瀏覽量

5369 -

AMD芯片

+關注

關注

0文章

14瀏覽量

2817

原文標題:基于AMD器件的EtherCAT從站方案

文章出處:【微信號:Comtech FPGA,微信公眾號:Comtech FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

求一種基于AMD器件的EtherCAT從站方案

求一種基于AMD器件的EtherCAT從站方案

評論