在嘗試將鎖相環(PLL)鎖定時,你是否碰到過麻煩?草率的判斷會延長調試過程,調試過程變得更加單調乏味。根據以下驗證通行與建立鎖定的程序,調試過程可以變得非常簡單。

第1步:驗證通信

第一步是驗證PLL響應編程的能力。如果PLL沒有鎖定,無法讀回,則嘗試發送需要最小量硬件命令工作的軟件命令。一種方法是通過軟件(而非引腳)調節PLL的通電斷電尋找引腳的可預測電流變化或偏置電壓電平變化。許多PLL在其輸入(OSCin)引腳的電平在通電時為Vcc/2,在斷電時為0V。

如果PLL集成了壓控振蕩器(VCO),則查看低壓差(LDO)輸出引腳電壓是否對通電和斷電命令做出反應。還可能可以切換輸入/輸出 (I/O)引腳,比如許多LMX系列PLL的MUXout引腳。如果采用上述方法能夠驗證通信,就可以繼續嘗試進行鎖定。

如果無法驗證通信,則查找常見的原因,例如以下原因:

編程串行

鎖存使能(也稱為芯片選擇條(CSB))過高

對軟件輸入的低通濾波過多

與串行外圍設備接口總線(SPI)存在時序問題

電源引腳焊接有誤

第2步:建立鎖定

驗證通信后,下一步就是嘗試對PLL進行鎖定。下面是PLL無法鎖定的一些更常見的原因:

對鎖定檢測引腳的錯誤解讀。如果配置有誤,鎖定檢測引腳會在實際已經鎖定的情況下顯示出PLL未鎖定。可以通過查看頻譜分析儀輸出或VCO調諧電壓驗證這一情況。

編程問題。向PLL發送錯誤的信息會很容易導致無法鎖定。一些常見的編程錯誤包括:VCO編程頻率超出范圍、VCO校準設置不正確或寄存器時序有誤。

VCO校準問題。對于集成VCO的PLL而言,頻率范圍通常分成幾個不同的頻段。錯誤的編程會導致VCO鎖定錯誤的頻段。對特定寄存器的編程通常會啟動VCO校準;因此必須確定在編程此寄存器時,其他軟件和硬件(尤其是基準輸入)狀態正確,以確保校準正常工作。

輸入或反饋路徑問題。如果VCO輸入或基準輸入因電源水平較低、壓擺率較低、匹配較差或諧波較高而存在問題,會導致PLL打開鎖定。大多數PLL有方法輸出內部頻率計數器的實際頻率輸出,將其發送到引腳。

環路濾波器中與地連接或短路。可以通過查看調諧電壓或切換鑒相器兩極,根據頻率變化確定連接或短路。

PLL環路濾波器不穩定。如果降低電荷泵電流導致PLL鎖定通常是不穩定的表現,但是僅憑這項技術不起作用不能排除不穩定這一因素。導致環路濾波器不穩定的產檢原因有忽略考慮VCO輸入電容;使用過度限制環路帶寬的集成濾波器;或者使用與PLL初始設計不同的PLL設置(電荷泵增益、VCO頻率或鑒相器頻率)。許多TI的工具如PLLatinum?模擬器工具能夠模擬環路濾波器的不穩定性。

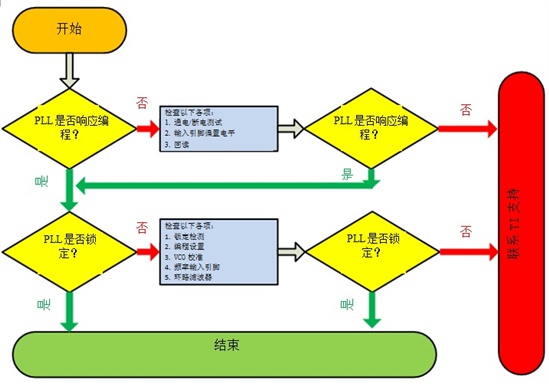

遵循系統的方法,不作出草率的假設能夠使PLL鎖定調試程序變得簡單許多。圖1為指導此程序的流程圖。

圖1:PLL調試流程圖

審核編輯:郭婷

-

寄存器

+關注

關注

31文章

5317瀏覽量

120006 -

pll

+關注

關注

6文章

774瀏覽量

135047 -

VCO

+關注

關注

12文章

190瀏覽量

69148

發布評論請先 登錄

相關推薦

AD9694輸入時鐘低于337.5MHz時,serdes鎖相環無法鎖定怎么解決?

AD9694的204B接口鎖相環無法鎖定是怎么回事?

ADF4360-7對VCO電感位置進行移動后鎖相環無法鎖定

電荷泵鎖相環電路鎖定檢測的基本原理,影響鎖相環數字鎖定電路的關鍵因子是什么?

AD9779內部鎖相環無法鎖定怎么解決?

詳解FPGA數字鎖相環平臺

利用開關的控制加速鎖相環鎖定的設計方法

教大家如何解決鎖相環無法鎖定

如何解決鎖相環無法鎖定

如何解決鎖相環無法鎖定

評論