衛星運營商越來越多地獲取越來越多的在軌數據,并且更愿意在有效載荷上處理這些數據以提取增值洞察力,而不是將大量信息下行傳輸到云端進行地面后處理。現有空間級半導體技術和/或 RF 帶寬限制限制了可實時處理的數據量。我知道有幾個客戶由于這兩個原因不得不取消他們的使命愿望,因為他們的下行鏈路需求會違反 ITU 規定。

相比之下,盡可能靠近原始數據源(即在邊緣)的本地化處理是基于對來自多個傳感器的大量信息的實時計算,這些信息是使用低延遲、確定性的接口在一個小的、具有獨特散熱和可靠性要求的低功耗外形。在軌提取分析顯著減少了延遲和 RF 下行鏈路帶寬——我們正在有效地將數據中心移動到原始數據的!

在這篇文章中,我想討論和比較微處理器和 FPGA 在邊緣進行密集的板載處理。一些應用程序從具有不同帶寬的多個傳感器(例如RF、LIDAR、成像和 GNSS)獲取大量數據,并且需要實時做出關鍵決策,例如,物體的識別和分類以實現航天器態勢感知,即,敵我識別、空間碎片碰撞規避、高清視頻原位對地觀測與太空探索、資源利用。使用機器學習技術提取在軌分析的自主機載處理也有增加的趨勢。

現有解決方案和局限性

當前的機載處理基于微處理器或 FPGA,兩者都沒有針對物體的 AI在軌表征進行優化。前者有利于控制、復雜的決策制定和操作系統支持,而后者可以處理各種計算要求苛刻的算法,在數據移動、自定義加速、面向位的功能和接口方面表現出色。然而,現有解決方案無法有效地處理線性代數、矩陣或矢量處理,也無法以低功耗利用并行性進行自主機器學習、AI 推理以及神經網絡的實施以進行特征檢測和分類。

在商業領域,初為游戲玩家開發的 GPU 正被用于加速各種計算任務,包括加密、金融建模、網絡和人工智能。GPU 使用多核和并行處理來同時執行數千個線程,與微處理器相比運行速度明顯更快且更具成本效益,允許在毫秒而不是秒、分鐘或小時內計算來自多個傳感器的數據密集型分析。GPU 針對大量存儲信息非常快速地反復執行相同的操作進行了優化,而 CPU 往往會到處跳躍。

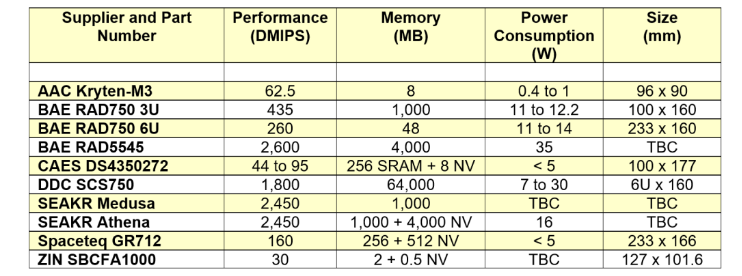

雖然有近三十種空間級微控制器、微處理器、FPGA 和專用 DSP 引擎,但只有一小部分可以考慮用于在軌基于邊緣的應用程序。許多現有設備不具備計算能力或低延遲內存/I/O 接口。有些消耗太多功率,需要大型且昂貴的熱管理解決方案:之前我描述了如何使您的空間級半導體保持冷卻,以確保它們的安全運行并限度地提高可靠性。表 1 列出了我考慮過的遺留標準處理產品。對于下面列出的 FPGA,指定性能是基于資源數量和時鐘頻率的理論峰值。V5QV 不包含標準的微處理器 IP。

表 1現成的航天級機載處理解決方案。

隨著機載數據量預計呈指數級增長,您應該使用哪種類型的處理器來進行密集型、基于邊緣的機載計算?MPU 好還是 FPGA 好?ESA 近關于機載數據處理的 研討會強調了當前的擔憂、趨勢和未來的需求。

阻礙在軌邊緣處理的基本技術限制是:

缺乏大容量、低延遲、低功耗的太空級內存。目前,快速空間級存儲僅限于易失性 DDR3/DDR4 SDRAM。之前,我解釋過要實現 1Tb 的板載存儲需要 64、16Gb 的芯片,總共消耗 17W 的功率,需要 152.3cm 3 的物理空間和 468,060 英鎊的財務成本。這在任何級別上都不是一個可行的實現,并且空間限定的非易失性內存非常慢。

缺乏用于提供所需處理能力的空間應用的高能效微處理器或 FPGA。在過去十年中,基于 65 和 20 納米 SRAM 的 FPGA 提供了消耗 20 W 的有效負載處理,而基于 28 納米閃存的設備提供了更低功耗的解決方案。超深亞微米性能、邏輯密度和資源導致消耗增加。具有所需原始性能的空間級 MPU 的功耗超過 30 W。

現有的航天級微處理器或 FPGA 無法有效地融合和處理來自多個傳感器的輸入。將大量信息移入和移出處理器會造成數據密集型計算的性能瓶頸。

現有的太空級微處理器或 FPGA 無法有效地實施用于對象識別和分類的深度學習算法。

基于邊緣處理的新解決方案

為了實現那些需要在軌、基于邊緣、機載處理的應用,的 FPGA 和微處理器正在解決上述限制:

快速(高達 2,400 MT/s)、4 GB、空間級 DDR4 內存的小尺寸可用性,我在之前的文章中對此SDRAM的硬件設計進行了介紹。

低功耗 28 nm 閃存 FPGA 的可用性降低了功耗,更節能的微處理器提高了 GFlops / W 指標。

自 2020 年以來,Teledyne e2v 的耐輻射 QLS1046-4GB 計算密集型微處理器包括數據路徑加速架構 (DPAA),以增加數據包解析、隊列管理、硬件緩沖區管理和加密,并支持 IEEE 1588 精度時間協議。同樣自 2020 年以來,Xilinx 的XQRKU060改進了信息流和吞吐量,數據路徑、I/O 和內存接口針對低延遲進行了優化。

下一代 7 納米 FPGA 包含專為處理線性代數而優化的 AI 模塊,可加速深度學習算法的性能。QLS1046-4GB 的四個內核均包含原生矢量協處理器,例如。氖。

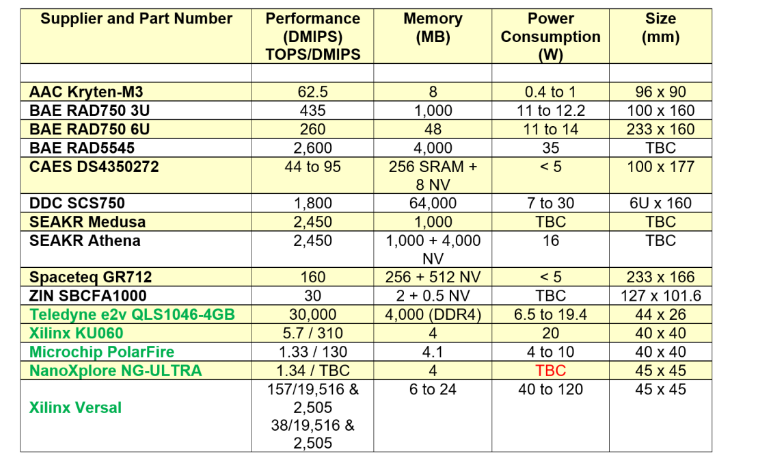

表 2 包括的航天級 FPGA 和微處理器:前者結合了可重構邏輯、MPU,而下一代部件將包含用于高效矢量處理的 AI 塊。對于以綠色列出的 FPGA/MPSoC,指定性能是基于資源數量和時鐘頻率的理論峰值。實際計算水平會較低,具體取決于這些計算的使用方式、實現方式、內存和 I/O 使用情況,但表 2 提供了一個有用的比較,包括軟核 RISC CPU。KU060 和 Versal 器件的高度并行特性反映在它們的大 TOPS 值中。

表 2航天級機載處理解決方案的比較。

隨著機載數據量的顯著增加,使用人工智能和機器學習技術進行自主有效載??荷處理的趨勢越來越明顯,可以為時序關鍵型和非實時應用提取在軌分析。例如,在其地面站覆蓋范圍之外的空間碎片回收航天器將無法接收到啟動避碰操作的延遲命令。從多個傳感器獲得機載態勢感知,然后進行對象檢測和分類,將允許實時做出這種時間關鍵的決定,而無需人工干預。同樣,高清 SAR 圖像生成大量地球觀測數據,而不是阻塞寶貴的 RF 下行鏈路,在軌人工智能推理和神經網絡的實施將允許進行特征識別、場景分割和表征。

傳統計算側重于處理已知問題,即可以輕松描述的問題。另一方面,深度學習就是解決你無法解釋的問題,例如,識別圖像中的對象,并且隨著時間的推移會變得更好。機器學習通常分為兩個階段:訓練和推理。精心策劃的數據被輸入模型,并調整變量以產生特定的預測。這需要線性代數、矩陣和矢量運算,然而,現有的解決方案無法有效地執行這些操作,也無法在低功耗下利用并行性。雖然的微處理器和 FPGA 的原始處理能力可能已經足夠,但這些設備在關鍵的延遲方面存在不足。在存儲和 CPU 之間移動數據會給數據密集型應用程序帶來性能瓶頸。

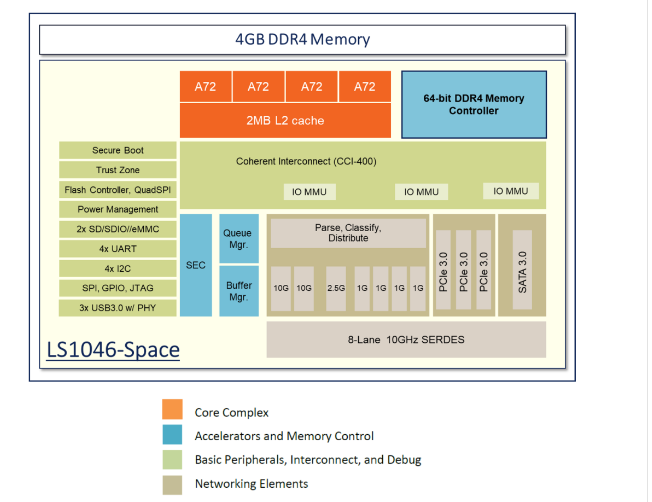

Teledyne e2v 提供其耐輻射Qormino QLS1046-4GB 四核處理器,結合了四個運行頻率高達 1.8 GHz 的 ARM ? Cortex A72 內核和 4 GB 快速 DDR4 SDRAM,外形小巧,44 x 26 毫米,如下圖所示. 將片外存儲器與多個 CPU 集成到單個基板上,無需設計這種復雜的時序關鍵接口,提供顯著的尺寸、重量和功率 (SWaP) 優勢,以實現在軌邊緣處理。該部件提供 30,000 DMIPS 或超過 45,000 CoreMarks 的計算性能。

四個 MPU 執行 ARMv8-A 架構,每個都有自己的 L1 32KB 數據緩存和 48KB 指令緩存,并共享一個公共的 2MB L2,如圖 2 所示。頻率為 1.2 GHz,電源電壓為1 V 和 1.6 GT/s 的 DDR 速率,QLS1046-4GB 的總功耗范圍為 6.5 至 12 W(不包括外圍設備),具體取決于允許結溫。同樣,在 1.8 GHz、1 V 的電源和 2.1 GT/s 的 DDR4 速率下,該設備的功耗為 9.3 至 19.4 W。其原始計算性能與內存帶寬一起避免了 I/O 瓶頸和小尺寸差異化QLS1046-4GB 來自表 1 中列出的解決方案。

圖 1 Qormino QLS1046-4GB 處理器和內存 [Teledyne e2v]。

Teledyne e2v 的耐輻射處理器路線圖將包括新的、多核、基于 ARM ?的 MPU,能夠連接到更大量的快速 DDR4 SDRAM。更多的將允許計算與并行執行的任務分開。可在此處查看描述使用 QLS1046-4GB 進行深度學習的個用例。

圖 2 Qormino QLS1046-4GB 框圖。

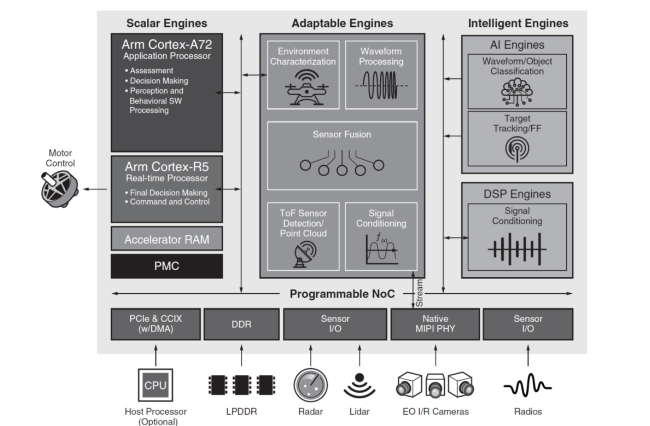

9 月,Xilinx 宣布將發布其 Versal ACAP(自適應計算加速平臺)的抗輻射版本。該器件包含一系列 AI 引擎,包括 VLIW SIMD 高性能內核,包含用于定點和浮點運算的矢量處理器、標量處理器、專用程序和數據存儲器、專用 AXI 通道以及對 DMA 和鎖的支持。

AI tile 提供多達 6 路指令并行性,包括兩個/三個標量操作、兩個向量讀取和一個寫入,以及每個時鐘周期的一個固定或浮點向量操作。數據級并行性是通過矢量級操作實現的,其中可以在每個時鐘周期的基礎上操作多組數據。與的 FPGA 和微處理器相比,AI 引擎將機器學習算法的性能分別提高了 20 倍和 100 倍,功耗僅為其 50%。與表 1 中列出的現成處理解決方案相比,AI 塊是實現智能、自主、在軌邊緣處理的關鍵區別特征。

圖 3 Xilinx 的 Versal ACAP [Xilinx] 的框圖。

結論

對于我目前正在開發的應用程序,哪種類型的板載處理器更好?FPGA、微處理器還是 ACAP?很大程度上取決于算法的實現方式,例如片上緩存的使用、外部存儲器訪問的數量和頻率、流水線、并行化和緩沖。的太空級設備可以超越商用 GPU,同時還能實現更高的功率和價格效率。

對于高清 SAR 視頻,QLS1046-4GB 的原始計算性能及其快速的內存接口和小巧的外形使其適合從地球觀測成像數據中提取實時信息。高達 2.1 GHz 的 DDR4 速率避免了傳統的 I/O 瓶頸。

對于態勢感知,例如,為了識別朋友或敵人,或避免空間碎片碰撞,的 FPGA(如 KU060)能夠實時攝取和處理來自多個傳感器的 Tbps 數據,低延遲,以交付 ASIC一流的系統級性能。同樣對于原位太空探索,資源利用。FPGA 處理一組不同的計算要求高的算法,在數據移動、自定義加速、面向位的功能和接口方面表現出色。

對于對象分類、AI 推理和自主決策制定,以實現特征識別,以便根據實時交通需求對碎片回收航天器或可重新配置的認知轉發器進行后期指揮,Xilinx 的 ACAP 將產生效的基于邊緣的矢量計算解決方案。神經網絡的實施需要 Versal 提供的 TeraOPS 性能和特定領域的并行性。這些 7 nm 設備可能會耗電,因此請檢查早期的功率預測電子表格以確保它們符合您分配的預算。QLS1046-4GB 可以以更低的功耗和更少的財務成本提供深度學習。

航天級微處理器、FPGA 和 ACAP 是互補的機載處理技術,每種技術都具有獨特的優勢。在軌,基于邊緣的處理需要實時計算從數據源處的多個傳感器獲取的大量信息,需要低延遲、確定性的接口,采用小型、低功耗外形,具有獨特的散熱和可靠性要求.

在為密集型在軌邊緣計算選擇合適的機載處理器時,還需要考慮上市時間、實施和采購方面的考慮,例如,FPGA 通常需要比微處理器更多的電源軌,這意味著需要更多的穩壓器,因此需要更大的 PCB 來容納它們。FPGA 還享有更難設計的名聲。對于某些項目,入軌時間可能非常短,原始設備制造商將堅持使用熟悉供應商的現有設備以加快硬件設計。一些制造商沒有技能或時間來學習新的開發工具或不同的編程語言。的超深亞微米、太空級 FPGA 的六位數價格也是許多 OEM 的障礙,尤其是那些以低成本、NewSpace 應用為目標的 OEM。

下一代在軌邊緣處理將結合微處理器、FPGA 和智能計算,形成一個緊密集成的異構平臺。需要多種引擎類型,因為沒有一種引擎能夠以方式執行應用程序所需的所有任務。標量微處理器是控制、復雜決策制定和操作系統支持的理想選擇,可重新配置的 FPGA 增加了處理各種要求苛刻的算法的靈活性,而智能引擎則優化了線性代數和矢量算法的計算,以用于機器學習和人工智能推理。

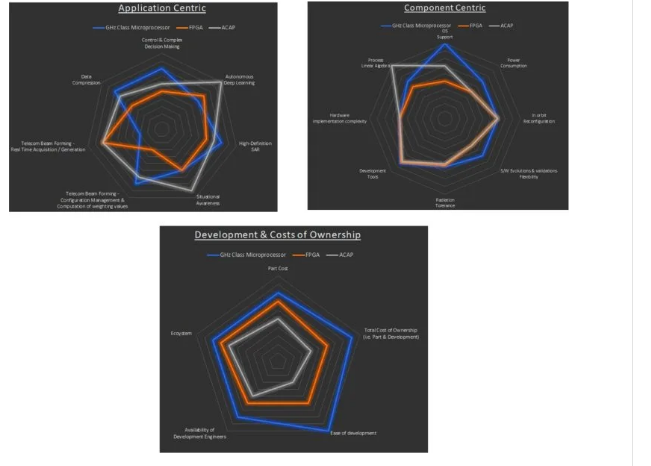

以下雷達圖(圖 4)比較了 QLS1046-4GB、的超深亞微米、航天級 FPGA 和用于在軌、基于 EDGE 的處理的 ACAP:

圖 4: 板載處理解決方案的比較。

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:用于密集、在軌、基于邊緣的計算的微處理器和 FPGA

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601858

原文標題:用于密集、在軌、基于邊緣的計算的微處理器和 FPGA

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

微處理器中寄存器的作用

微處理器的指令集有哪些

微處理器如何控制計算機系統

嵌入式系統的微處理器選擇

用于密集、在軌、基于邊緣的計算的微處理器和 FPGA

用于密集、在軌、基于邊緣的計算的微處理器和 FPGA

評論