一直想給大家講講ESD的理論,很經(jīng)典。但是由于理論性太強(qiáng),任何理論都是一環(huán)套一環(huán)的,如果你不會(huì)畫(huà)雞蛋,注定了你就不會(huì)畫(huà)大衛(wèi)。

先來(lái)談靜電放電(ESD: Electrostatic Discharge)是什么?這應(yīng)該是造成所有電子元器件或集成電路系統(tǒng)造成過(guò)度電應(yīng)力破壞的主要元兇。因?yàn)殪o電通常瞬間電壓非常高(>幾千伏),所以這種損傷是毀滅性和永久性的,會(huì)造成電路直接燒毀。所以預(yù)防靜電損傷是所有IC設(shè)計(jì)和制造的頭號(hào)難題。

靜電,通常都是人為產(chǎn)生的,如生產(chǎn)、組裝、測(cè)試、存放、搬運(yùn)等過(guò)程中都有可能使得靜電累積在人體、儀器或設(shè)備中,甚至元器件本身也會(huì)累積靜電,當(dāng)人們?cè)诓恢榈那闆r下使這些帶電的物體接觸就會(huì)形成放電路徑,瞬間使得電子元件或系統(tǒng)遭到靜電放電的損壞(這就是為什么以前修電腦都必須要配戴靜電環(huán)托在工作桌上,防止人體的靜電損傷芯片),如同云層中儲(chǔ)存的電荷瞬間擊穿云層產(chǎn)生劇烈的閃電,會(huì)把大地劈開(kāi)一樣,而且通常都是在雨天來(lái)臨之際,因?yàn)榭諝鉂穸却笠仔纬蓪?dǎo)電通到。

那么,如何防止靜電放電損傷呢?首先當(dāng)然改變壞境從源頭減少靜電(比如減少摩擦、少穿羊毛類(lèi)毛衣、控制空氣溫濕度等),當(dāng)然這不是我們今天討論的重點(diǎn)。

我們今天要討論的時(shí)候如何在電路里面涉及保護(hù)電路,當(dāng)外界有靜電的時(shí)候我們的電子元器件或系統(tǒng)能夠自我保護(hù)避免被靜電損壞(其實(shí)就是安裝一個(gè)避雷針)。

這也是很多IC設(shè)計(jì)和制造業(yè)者的頭號(hào)難題,很多公司有專(zhuān)門(mén)設(shè)計(jì)ESD的團(tuán)隊(duì),今天我就和大家從最基本的理論講起逐步講解ESD保護(hù)的原理及注意點(diǎn),你會(huì)發(fā)現(xiàn)前面講的PN結(jié)/二極管、三極管、MOS管、snap-back全都用上了。。。

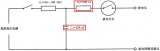

以前的專(zhuān)題講解PN結(jié)二極管理論的時(shí)候,就講過(guò)二極管有一個(gè)特性:正向?qū)ǚ聪蚪刂梗曳雌妷豪^續(xù)增加會(huì)發(fā)生雪崩擊穿而導(dǎo)通,我們稱(chēng)之為鉗位二極管(Clamp)。

這正是我們?cè)O(shè)計(jì)靜電保護(hù)所需要的理論基礎(chǔ),我們就是利用這個(gè)反向截止特性讓這個(gè)旁路在正常工作時(shí)處于斷開(kāi)狀態(tài),而外界有靜電的時(shí)候這個(gè)旁路二極管發(fā)生雪崩擊穿而形成旁路通路保護(hù)了內(nèi)部電路或者柵極(是不是類(lèi)似家里水槽有個(gè)溢水口,防止水龍頭忘關(guān)了導(dǎo)致整個(gè)衛(wèi)生間水災(zāi))。

那么問(wèn)題來(lái)了,這個(gè)擊穿了這個(gè)保護(hù)電路是不是就徹底死了?難道是一次性的?答案當(dāng)然不是。PN結(jié)的擊穿分兩種,分別是電擊穿和熱擊穿,電擊穿指的是雪崩擊穿(低濃度)和齊納擊穿(高濃度),而這個(gè)電擊穿主要是載流子碰撞電離產(chǎn)生新的電子-空穴對(duì)(electron-hole),所以它是可恢復(fù)的。但是熱擊穿是不可恢復(fù)的,因?yàn)闊崃烤奂瘜?dǎo)致硅(Si)被熔融燒毀了。所以我們需要控制在導(dǎo)通的瞬間控制電流,一般會(huì)在保護(hù)二極管再串聯(lián)一個(gè)高電阻,

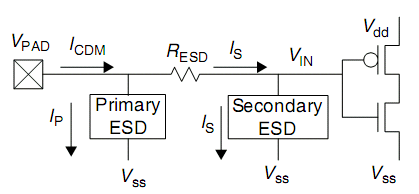

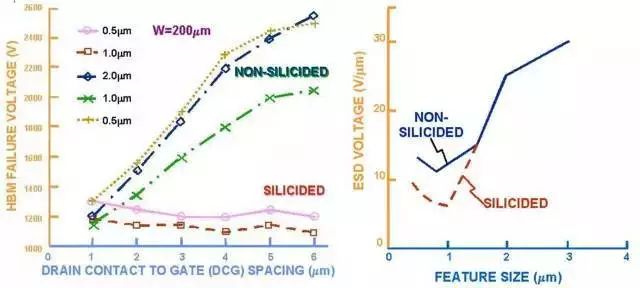

另外,大家是不是可以舉一反三理解為什么ESD的區(qū)域是不能form Silicide的?還有給大家一個(gè)理論,ESD通常都是在芯片輸入端的Pad旁邊,不能在芯片里面,因?yàn)槲覀兛偸窍M饨绲撵o電需要第一時(shí)間泄放掉吧,放在里面會(huì)有延遲的(關(guān)注我前面解剖的那個(gè)芯片PAD旁邊都有二極管。甚至有放兩級(jí)ESD的,達(dá)到雙重保護(hù)的目的。

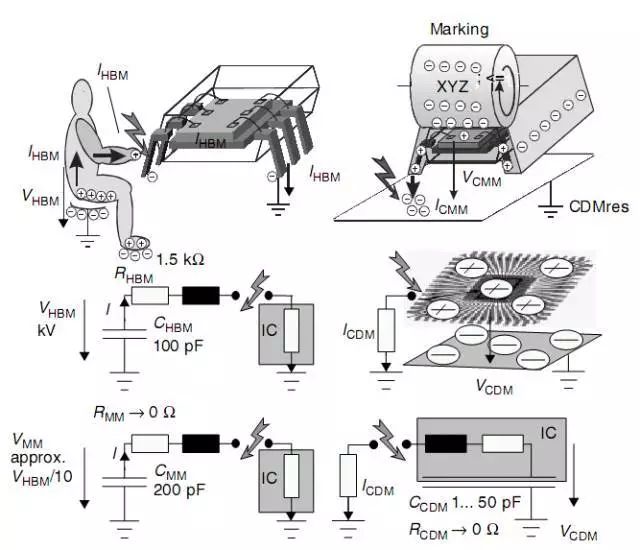

在講ESD的原理和Process之前,我們先講下ESD的標(biāo)準(zhǔn)以及測(cè)試方法,根據(jù)靜電的產(chǎn)生方式以及對(duì)電路的損傷模式不同通常分為四種測(cè)試方式:人體放電模式(HBM: Human-Body Model)、機(jī)器放電模式(Machine Model)、元件充電模式(CDM: Charge-Device Model)、電場(chǎng)感應(yīng)模式(FIM: Field-Induced Model),但是業(yè)界通常使用前兩種模式來(lái)測(cè)試(HBM, MM)。

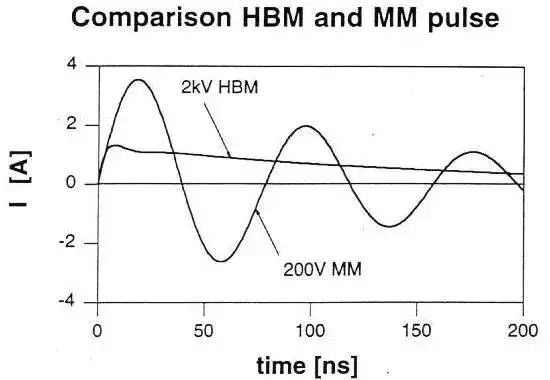

1、人體放電模式(HBM):當(dāng)然就是人體摩擦產(chǎn)生了電荷突然碰到芯片釋放的電荷導(dǎo)致芯片燒毀擊穿,秋天和別人觸碰經(jīng)常觸電就是這個(gè)原因。業(yè)界對(duì)HBM的ESD標(biāo)準(zhǔn)也有跡可循(MIL-STD-883C method 3015.7,等效人體電容為100pF,等效人體電阻為1.5Kohm),或者國(guó)際電子工業(yè)標(biāo)準(zhǔn)(EIA/JESD22-A114-A)也有規(guī)定,看你要follow哪一份了。如果是MIL-STD-883C method 3015.7,它規(guī)定小于<2kV的則為Class-1,在2kV4kV的為class-2,4kV16kV的為class-3。

2、機(jī)器放電模式(MM):當(dāng)然就是機(jī)器(如robot)移動(dòng)產(chǎn)生的靜電觸碰芯片時(shí)由pin腳釋放,次標(biāo)準(zhǔn)為EIAJ-IC-121 method 20(或者標(biāo)準(zhǔn)EIA/JESD22-A115-A),等效機(jī)器電阻為0 (因?yàn)榻饘?,電容依舊為100pF。由于機(jī)器是金屬且電阻為0,所以放電時(shí)間很短,幾乎是ms或者us之間。但是更重要的問(wèn)題是,由于等效電阻為0,所以電流很大,所以即使是200V的MM放電也比2kV的HBM放電的危害大。而且機(jī)器本身由于有很多導(dǎo)線(xiàn)互相會(huì)產(chǎn)生耦合作用,所以電流會(huì)隨時(shí)間變化而干擾變化。

ESD的測(cè)試方法類(lèi)似FAB里面的GOI測(cè)試,指定pin之后先給他一個(gè)ESD電壓,持續(xù)一段時(shí)間后,然后再回來(lái)測(cè)試電性看看是否損壞,沒(méi)問(wèn)題再去加一個(gè)step的ESD電壓再持續(xù)一段時(shí)間,再測(cè)電性,如此反復(fù)直至擊穿,此時(shí)的擊穿電壓為ESD擊穿的臨界電壓(ESD failure threshold Voltage)。通常我們都是給電路打三次電壓(3 zaps),為了降低測(cè)試周期,通常起始電壓用標(biāo)準(zhǔn)電壓的70% ESD threshold,每個(gè)step可以根據(jù)需要自己調(diào)整50V或者100V。

| (1). Stress number = 3 Zaps. (5 Zaps, the worst case) | |

|---|---|

| (2). Stress step | ΔVESD = 50V(100V) for VZAP <=1000VΔVESD = 100V(250V, 500V) for VZAP > 1000V |

| (3). Starting VZAP = 70% of averaged ESD failure threshold (VESD) |

另外,因?yàn)槊總€(gè)chip的pin腳很多,你是一個(gè)個(gè)pin測(cè)試還是組合pin測(cè)試,所以會(huì)分為幾種組合:I/O-pin測(cè)試(Input and Output pins)、pin-to-pin測(cè)試、Vdd-Vss測(cè)試(輸入端到輸出端)、Analog-pin。

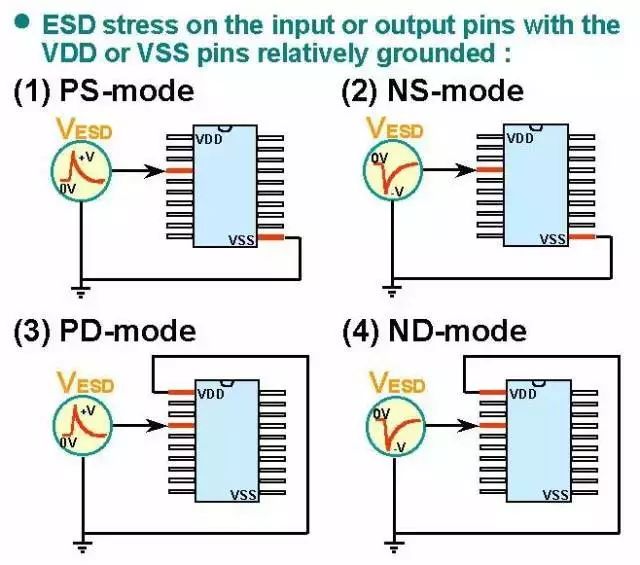

- I/O pins:就是分別對(duì)input-pin和output-pin做ESD測(cè)試,而且電荷有正負(fù)之分,所以有四種組合:input+正電荷、input+負(fù)電荷、output+正電荷、output+負(fù)電荷。測(cè)試input時(shí)候,則output和其他pin全部浮接(floating),反之亦然。

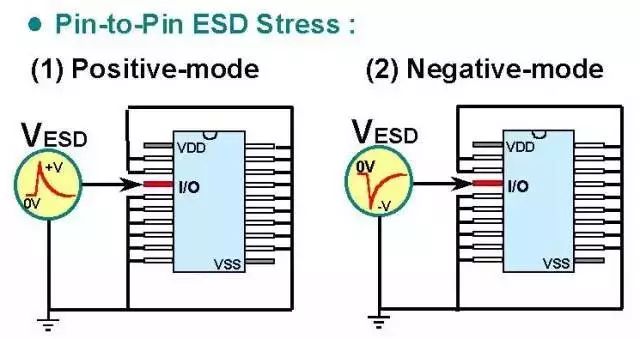

- pin-to-pin測(cè)試: 靜電放電發(fā)生在pin-to-pin之間形成回路,但是如果要每每?jī)蓚€(gè)腳測(cè)試組合太多,因?yàn)槿魏蔚腎/O給電壓之后如果要對(duì)整個(gè)電路產(chǎn)生影響一定是先經(jīng)過(guò)VDD/Vss才能對(duì)整個(gè)電路供電,所以改良版則用某一I/O-pin加正或負(fù)的ESD電壓,其他所有I/O一起接地,但是輸入和輸出同時(shí)浮接(Floating)。

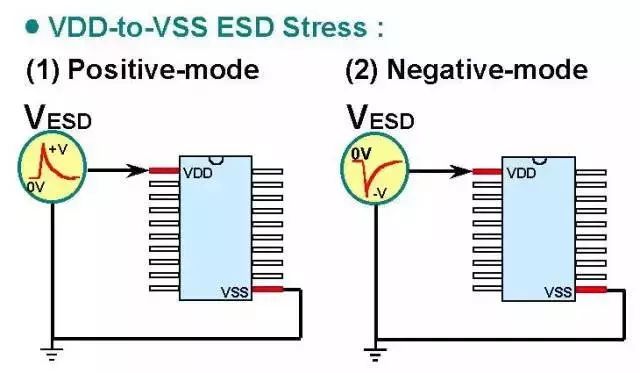

3、Vdd-Vss之間靜電放電:只需要把Vdd和Vss接起來(lái),所有的I/O全部浮接(floating),這樣給靜電讓他穿過(guò)Vdd與Vss之間。

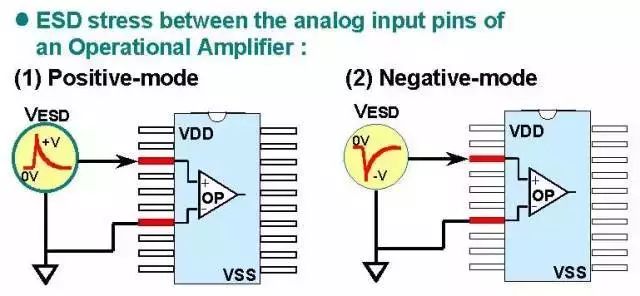

4、Analog-pin放電測(cè)試:因?yàn)?a href="http://www.nxhydt.com/analog/" target="_blank">模擬電路很多差分比對(duì)(Differential Pair)或者運(yùn)算放大器(OP AMP)都是有兩個(gè)輸入端的,防止一個(gè)損壞導(dǎo)致差分比對(duì)或運(yùn)算失效,所以需要單獨(dú)做ESD測(cè)試,當(dāng)然就是只針對(duì)這兩個(gè)pin,其他pin全部浮接(floating)。

好了,ESD的原理和測(cè)試部分就講到這里了,下面接著講Process和設(shè)計(jì)上的factor

-

電路

+關(guān)注

關(guān)注

172文章

5852瀏覽量

171942 -

IC設(shè)計(jì)

+關(guān)注

關(guān)注

37文章

1292瀏覽量

103780 -

靜電放電

+關(guān)注

關(guān)注

3文章

284瀏覽量

44620

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

電源設(shè)計(jì)中的EMC、EMI、ESD概念簡(jiǎn)述

IDDR與ODDR的簡(jiǎn)述

ESD測(cè)試你做了嗎?

ESD槍波形測(cè)試方法

ESD模擬測(cè)試的基礎(chǔ)知識(shí)

ESD耐性的測(cè)試方法耐性

BMS靜電放電ESD測(cè)試的基本知識(shí)

簡(jiǎn)述ESD的原理和測(cè)試2

防靜電ESD測(cè)試過(guò)程展示

ESD的保護(hù)機(jī)理和主要測(cè)試模式有哪些?

基于AFE79xx的JESD204C應(yīng)用簡(jiǎn)述

簡(jiǎn)述ESD的原理和測(cè)試1

簡(jiǎn)述ESD的原理和測(cè)試1

評(píng)論