摘要

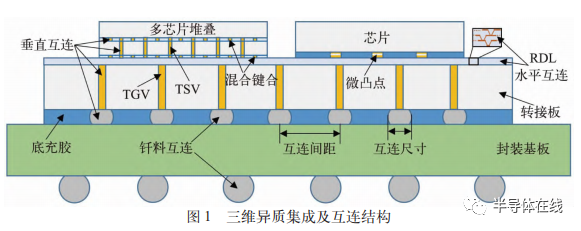

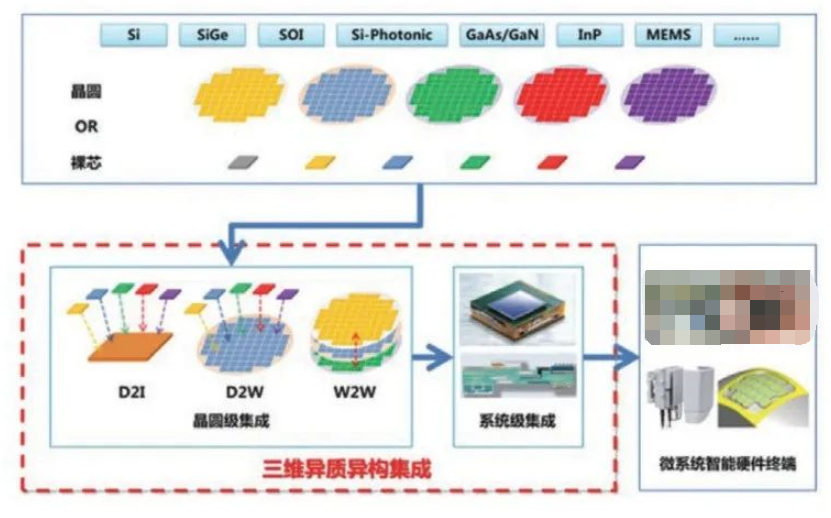

集成電路的納米制程工藝逐漸逼近物理極限,通過異質(zhì)集成來延續(xù)和拓展摩爾定律的重要 性日趨凸顯。異質(zhì)集成以需求為導(dǎo)向,將分立的處理器、存儲(chǔ)器和傳感器等不同尺寸、功能和類型 的芯片,在三維方向上實(shí)現(xiàn)靈活的模塊化整合與系統(tǒng)集成。異質(zhì)集成芯片在垂直方向上的信號(hào)互連 依賴硅通孔(TSV)或玻璃通孔(TGV)等技術(shù)實(shí)現(xiàn),而在水平方向上可通過再布線層(RDL)技術(shù) 實(shí)現(xiàn)高密度互連。

異質(zhì)集成技術(shù)開發(fā)與整合的關(guān)鍵在于融合實(shí)現(xiàn)多尺度、多維度的芯片互連,通過 三維互連技術(shù)配合,將不同功能的芯粒異質(zhì)集成到一個(gè)封裝體中,從而提高帶寬和電源效率并減小 延遲,為高性能計(jì)算、人工智能和智慧終端等提供小尺寸、高性能的芯片。通過綜述TSV、TGV、RDL技術(shù)及相應(yīng)的2.5D、3D異質(zhì)集成方案,闡述了當(dāng)前研究現(xiàn)狀,并探討存在的技術(shù)難點(diǎn)及未來發(fā) 展趨勢(shì)。

1 引言

芯片是推動(dòng)信息社會(huì)蓬勃發(fā)展的基石,掌握高端 芯片的制造技術(shù)關(guān)乎國家未來在人工智能、高性能計(jì) 算、5G/6G通信和萬物互聯(lián)等關(guān)鍵領(lǐng)域的全球競(jìng)爭(zhēng)力。由于集成電路的納米制程工藝逐漸逼近物理極限,通 過芯片三維異質(zhì)集成來延續(xù)和拓展摩爾定律的重要 性日趨凸顯。異質(zhì)集成以需求為導(dǎo)向,將分立的處 理器、存儲(chǔ)器和傳感器等不同尺寸、功能和類型的芯 片,在三維方向上實(shí)現(xiàn)靈活的模塊化整合與系統(tǒng)集成。此時(shí),如何實(shí)現(xiàn)互連芯片之間高帶寬、低延遲和低損 耗的信號(hào)傳輸,成為突破高端芯片內(nèi)存墻、速度墻和 功耗墻等瓶頸的關(guān)鍵。據(jù)臺(tái)積電測(cè)算,若芯片堆疊 的垂直互連間距從現(xiàn)有的36μm降至0.9μm,互連密 度至少可增加3個(gè)數(shù)量級(jí),實(shí)現(xiàn)10倍以上的通信速 度、20倍的能源效率和近2萬倍的帶寬密度提升。以 芯片封裝互連密度來表述的摩爾定律也獲得了廣泛 共識(shí)。由此可見,高密度三維互連技術(shù)將成為未來推 動(dòng)芯片持續(xù)向高性能和微型化發(fā)展的關(guān)鍵引擎。

隨著芯片模塊化思想及芯粒(Chiplet,一類在獨(dú)立 裸片上設(shè)計(jì)、采用不同工藝制程制作并可復(fù)用集成的 芯片)技術(shù)的提出和發(fā)展,芯片設(shè)計(jì)、工藝制程和封裝 測(cè)試由單片一體化向多模塊靈活整合發(fā)展,因此封裝技術(shù)需進(jìn)行相應(yīng)的深度開發(fā)和模塊化整合。21世紀(jì) 以來,美國國防部高級(jí)研究計(jì)劃局(DARPA)、歐洲微 電子研究中心(IMEC)、德國Fraunhofer、法國Leti、新 加坡IME、美國麻省理工學(xué)院、佐治亞理工學(xué)院等單 位均陸續(xù)投入大量資源,開展深入的三維異質(zhì)集成研 發(fā)工作。加入封裝交流群,加VX:tuoke08。這些頂尖研究機(jī)構(gòu)借助系統(tǒng)集成方面的基礎(chǔ) 優(yōu)勢(shì),針對(duì)多芯片三維異質(zhì)集成技術(shù)的開發(fā)一直走在 世界前列。值得注意的是,2022年初,英特爾、臺(tái)積 電、三星、高通、谷歌等行業(yè)領(lǐng)先企業(yè)成立了通用Chiplet高密度互連聯(lián)盟(UCIe),旨在整合推廣三維芯片 互連及異質(zhì)集成的技術(shù)標(biāo)準(zhǔn)并構(gòu)建完善生態(tài),這也標(biāo)志 著異質(zhì)集成技術(shù)進(jìn)入了發(fā)展及產(chǎn)業(yè)應(yīng)用的關(guān)鍵階段。

事實(shí)上,異質(zhì)集成技術(shù)開發(fā)與整合的關(guān)鍵在于融合實(shí)現(xiàn)多尺度、多維度的芯片互連,從而提高帶寬和電源效率并減小延遲,為高性能計(jì)算、人工智能和智 慧終端等提供更小尺寸和更高性能的芯片。芯片的垂 直方向互連依賴硅通孔(TSV)或玻璃通孔(TGV)等技 術(shù),水平方向上通過再布線層(RDL)技術(shù)進(jìn)行互連。本 文綜述了TSV、TGV、RDL等芯片三維互連技術(shù),分析基于這些互連技術(shù)的三維異質(zhì)集成方案及應(yīng)用,闡述 當(dāng)前研究現(xiàn)狀,并探討存在的技術(shù)難點(diǎn)及未來發(fā)展趨勢(shì)。

2芯片三維互連技術(shù)

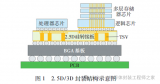

通過垂直方向上的TSV/TGV技術(shù)與水平方向上 的RDL技術(shù)的配合,對(duì)芯片進(jìn)行三維互連,可將不同 尺寸、材料、制程和功能的Chiplet異質(zhì)集成到1個(gè)封 裝體中,形成的三維異質(zhì)集成及互連結(jié)構(gòu)如圖1所示。

2.1 TSV 技術(shù)

TSV主要用于實(shí)現(xiàn)垂直方向上的信號(hào)連接,其中Cu-TSV的應(yīng)用最為廣泛。典型的Cu-TSV制造工藝包 括以下關(guān)鍵步驟:深孔刻蝕、形成絕緣層/粘附阻擋層/種子層、電鍍Cu填充、去除多余Cu及背面的TSV-Cu外露。目前用于三維異質(zhì)集成的TSV直徑約為10μm,深寬比約為10∶1。與半導(dǎo)體領(lǐng)域的其他技術(shù)發(fā) 展方向類似,TSV的直徑、間距和深度等關(guān)鍵尺寸亟 需縮小。TSV直徑的減小,不但能夠減少其占用面積、 提高互連密度,還可以顯著減少Cu-TSV附近的應(yīng)力, 避免影響器件性能。根據(jù)TSV的直徑及深寬比的路線 圖,未來先進(jìn)TSV工藝的直徑有望減小到1μm,深寬 比達(dá)到20∶1。國際上重要的半導(dǎo)體科研機(jī)構(gòu)和領(lǐng)先 企業(yè)已經(jīng)開始研究亞微米直徑的TSV技術(shù)。

細(xì)小直徑、高深寬比的TSV加工的主要難點(diǎn)包括 如何形成連續(xù)均勻的絕緣層/粘附阻擋層/種子層和 無缺陷的超共形電鍍Cu填充等。由于物理氣相沉積 (PVD)、化學(xué)氣相沉積(CVD)在微米尺度深孔內(nèi)覆蓋 率低,通過PVD、CVD沉積絕緣層、粘附阻擋層和種 子層不利于TSV尺寸的進(jìn)一步縮小。原子層沉積 (ALD)可制備小直徑、高深寬比的共形薄層,成為突 破PVD工藝瓶頸的關(guān)鍵技術(shù)。ALD具有的優(yōu)勢(shì)包括:較低的工藝溫度,比現(xiàn)有CVD及PVD工藝更好的深 孔覆蓋能力,介質(zhì)沉積前無需表面處理,更薄的介質(zhì) 層減少了TSV的拋光處理時(shí)間。2015年,IMEC報(bào)道 了直徑為3μm、深度為50μm的TSV制造工藝,采用ALD沉積氧化絕緣層、WN擴(kuò)散阻擋層,利用化學(xué)鍍NiB作為電鍍種子層,快速深孔電鍍工藝實(shí)現(xiàn)TSV填 充。日本學(xué)者研究了直徑為2μm、深度為30μm的TSV結(jié)構(gòu),在ALD-Ru、ALD-W上化學(xué)鍍沉積銅,然后 完成TSV電鍍銅填充,化學(xué)鍍銅和ALD-Ru之間的結(jié) 合強(qiáng)度大于100 MPa。然而,當(dāng)前工藝探索和研究 還缺乏系統(tǒng)性,深孔電鍍/化學(xué)鍍填充、ALD沉積形 成多界面材料和結(jié)構(gòu)的電學(xué)特性、可靠性以及失效機(jī) 理都還需要深入研究。

2.2 TGV 技術(shù)

TGV作為TSV的低成本替代方案,逐漸受到廣 泛關(guān)注。TGV無需沉積絕緣層,具有高頻電學(xué)特性優(yōu) 良、工藝流程簡(jiǎn)單的特點(diǎn)。此外,玻璃的機(jī)械穩(wěn)定性 強(qiáng)、翹曲小且成本低,大尺寸玻璃易于獲取。TGV在射 頻組件、光電集成和MEMS器件等三維封裝領(lǐng)域具有 廣闊的應(yīng)用前景。

以盲孔為例的TGV的工藝流程包括:首先制備TGV盲孔;其次通過物理氣相沉積的方法在TGV盲 孔內(nèi)部沉積Ti/Cu種子層(工藝溫度為250~400℃);接著利用TGV深孔電鍍,自底而上進(jìn)行孔內(nèi)填充,實(shí) 現(xiàn)TGV無孔洞填充并退火。近年來,關(guān)于TGV的成 孔方法被廣泛研究報(bào)道,如噴砂法、光敏玻璃法、等離 子刻蝕法、激光燒蝕和激光誘導(dǎo)濕法刻蝕法等。其 中,激光誘導(dǎo)濕法刻蝕技術(shù)具有快速高效成孔、工藝 簡(jiǎn)單、側(cè)壁光滑、高精度成孔等顯著優(yōu)點(diǎn),被廣泛應(yīng)用 于各種玻璃材料的三維微流道加工。2014年,德國LPKF公司的OSTHOLT等人利用激光誘導(dǎo)濕法刻 蝕技術(shù)率先制備出應(yīng)用于玻璃三維集成的TGV。結(jié)果 顯示,對(duì)于厚度為50~200μm的玻璃,通過改變氫氟 酸(HF)蝕刻參數(shù)可以得到直徑為10~50μm、節(jié)距不 小于50μm的TGV。然而,其側(cè)壁垂直度較差,錐度均 大于5°,對(duì)電學(xué)性能及可靠性都有負(fù)面影響。另外,TGV的深寬比往往可決定芯片的集成度,該方法制備 的TGV深寬比一般不大于6∶1,遠(yuǎn)小于先進(jìn)TSV工藝 所能達(dá)到的20∶1。CHEN等人采用皮秒激光對(duì)硼硅 酸鹽玻璃進(jìn)行改性時(shí),發(fā)現(xiàn)在激光束傳播路徑的影響 區(qū)出現(xiàn)的一系列納米孔洞增強(qiáng)了玻璃樣品在HF溶液 中的選擇性蝕刻能力。通過調(diào)節(jié)激光脈沖和HF溶液 濃度等,可針對(duì)特定成分的玻璃改善TGV側(cè)壁垂直 度。刻蝕液選擇性蝕刻的原因及蝕刻速率隨激光脈沖 能量改變的機(jī)理仍有待闡明;超/兆聲振動(dòng)、溫度和蝕 刻液濃度等因素及多場(chǎng)耦合對(duì)蝕刻速率和選擇比的 影響等重要問題仍未得到研究。

目前,垂直TGV通孔的電鍍填充方式一般為蝶 形填充,其與TSV硅基半導(dǎo)體工藝自下而上的盲孔電 鍍填充具有本質(zhì)差別[20]。與盲孔填充相比,通孔填充在 流體力學(xué)與質(zhì)量傳輸方面均存在明顯差異。盲孔填充 時(shí),鍍液在孔內(nèi)很難流動(dòng);而在通孔內(nèi)部,鍍液可以流 動(dòng)從而加強(qiáng)內(nèi)部的傳質(zhì)。且通孔與盲孔的幾何形狀不 同,沒有盲孔底部,不會(huì)產(chǎn)生自下而上的填充方式。TGV通孔與盲孔在幾何形狀、流場(chǎng)、質(zhì)量傳輸?shù)确矫?的差異,導(dǎo)致用于盲孔填充的電鍍配方及工藝無法直 接用于TGV通孔。另一方面,由于TGV的直徑、深寬 比、表面粗糙度及垂直度等均與印制電路板(PCB)通 孔有顯著差異,現(xiàn)有通孔填充理論應(yīng)用于TGV電鍍 填充具有很大的局限性,需綜合考慮電流密度、添加 劑、流場(chǎng)和傳質(zhì)等多因素耦合,但目前仍缺乏相關(guān)研究。

TGV、TSV以外,通模通孔(TMV)、封裝通孔 (TPV)等技術(shù)也是滿足微電子封裝高密度和多功能要 求的潛在解決方案。TMV是一種在封裝尺度上的 工藝,通過垂直通孔與RDL技術(shù),可有效地為封裝上 封裝(PoP)與多芯片嵌入式堆疊封裝中的不同封裝提 供垂直互連。目前用于垂直互連的TMV孔徑一般為25~150μm,深度為100~1 000μm。此外,獲得高質(zhì)量 的TMV仍需解決制備TMV過程中管壁平整度、通孔 中的殘?jiān)蜕釋?dǎo)致的芯片與模具分層等問題。具有細(xì)間距TPV的薄玻璃中介層因其具有絕緣性能、大 面板可用性和與硅匹配的熱膨脹系數(shù),而能夠作為3D集成的低成本和高I/O基板。在玻璃上實(shí)現(xiàn)TPV的 一般方法有激光燒蝕法、深反應(yīng)離子蝕刻及光化學(xué)蝕刻法。作為TSV的替代方案,實(shí)現(xiàn)更小尺寸的TPV直 徑與金屬化仍需深入研究。

2.3 RDL 技術(shù)

RDL是實(shí)現(xiàn)芯片水平方向互連的關(guān)鍵技術(shù),可將 芯片上原來設(shè)計(jì)的I/O焊盤位置通過晶圓級(jí)金屬布線 工藝變換位置和排列,形成新的互連結(jié)構(gòu)。借鑒PCB銅布線工藝,RDL可通過加成法、半加成法等方法加工。典型的RDL半加成工藝包括:(1)形成鈍化絕緣 層并開口;(2)沉積粘附層和種子層;(3)光刻顯影形成 線路圖案并電鍍填充;(4)去除光刻膠并刻蝕粘附層和 種子層;(5)重復(fù)上述步驟進(jìn)行下一層的RDL布線。高 密度的RDL布線可借鑒半導(dǎo)體銅互連的大馬士革工 藝進(jìn)行加工,引入化學(xué)機(jī)械拋光進(jìn)行平坦化,并去除 多余的銅及粘附層/種子層。

目前,高密度互連有機(jī)RDL線寬/線間距(L/S)約 為6μm,微孔直徑為20μm、間距為50μm,可實(shí)現(xiàn)每 平方毫米每層約40個(gè)I/O的密度。然而,為了進(jìn)一 步提高I/O密度,需要具有1μm線寬/線間距以及1~ 2μm直徑微孔的RDL。RDL技術(shù)的進(jìn)步對(duì)于實(shí)現(xiàn)高 密度、高帶寬(每平方毫米每層超過500個(gè)I/O、帶寬 大于500 Gbit/s)的芯片互連具有極為重要的意義。高 密度RDL有4個(gè)關(guān)鍵問題:(1)細(xì)線條光刻L/S為1μm;(2) 微孔加工是限制RDL實(shí)現(xiàn)高I/O密度和精 細(xì)I/O間距的最主要的障礙;(3)低介電常數(shù)和低耗損 因子的介電材料;(4) 半加成法是實(shí)現(xiàn)高密度RDL的 普遍工藝。

3 基于 TSV 及 RDL 的異質(zhì)集成方案

經(jīng)過多年發(fā)展,TSV封裝技術(shù)的發(fā)展經(jīng)歷了從TSV簡(jiǎn)單互連、2.5D TSV轉(zhuǎn)接板、微凸點(diǎn)3D集成到 目前最為關(guān)注的無凸點(diǎn)3D集成。從應(yīng)用的角度看,已 進(jìn)入量產(chǎn)的基于TSV的封裝技術(shù)主要集中在高端可 編程器件、圖像處理器、存儲(chǔ)芯片以及傳感器芯片等 領(lǐng)域。

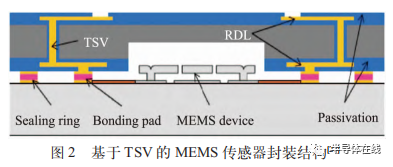

3.1基于TSV及RDL互連的晶圓級(jí)封裝

用TSV簡(jiǎn)單互連代替引線鍵合,實(shí)現(xiàn)硅背面與正 面有源區(qū)或金屬布線之間的電氣導(dǎo)通,是TSV在批量 生產(chǎn)中的首次使用。其典型應(yīng)用包括圖像、指紋、濾波 器、加速度計(jì)在內(nèi)的傳感器的封裝,基于TSV的MEMS傳感器封裝結(jié)構(gòu)如圖2所示。使用TSV可減 小傳感器模塊的封裝尺寸,利于進(jìn)行晶圓級(jí)封裝,提 高生產(chǎn)效率并降低成本。近年來發(fā)展出的基于后通孔TSV的埋入硅基三維異質(zhì)集成技術(shù),提供了1種低成 本、高性能的異質(zhì)集成方案。2016年,華天科技有限公 司開發(fā)出硅基埋入扇出(eSiFO)技術(shù),使用硅片作為 載體,將芯片置于在12英寸硅晶圓上制作的高精度凹 槽內(nèi),重構(gòu)出1個(gè)晶圓;然后采用可光刻聚合物材料填 充芯片和晶圓之間的間隙,在芯片和硅片表面形成扇 出的鈍化平面;再通過光刻打開鈍化層開口,并采用 晶圓級(jí)工藝進(jìn)行布線和互連封裝。硅基埋入封裝具有 超小的封裝尺寸、工藝簡(jiǎn)單、易于進(jìn)行系統(tǒng)封裝和高 密度三維集成等優(yōu)點(diǎn)。同時(shí),可通過制備背面RDL和Via-last TSV,實(shí)現(xiàn)異質(zhì)集成多芯片的三維堆疊封 裝。其基本工藝流程包括:將測(cè)試正常的芯片嵌入單 個(gè)eSiFO封裝體,然后分別在eSiFO封裝體的正面和 背面形成RDL,再通過微凸點(diǎn)和Via-last TSV實(shí)現(xiàn)多 個(gè)獨(dú)立的eSiFO封裝體與嵌入式芯片之間的電信號(hào) 互連。eSiFO技術(shù)可以將由不同設(shè)計(jì)公司、晶圓廠設(shè)計(jì) 制造的各種晶圓尺寸和特征尺寸的不同系統(tǒng)或不同 功能的芯片集成到1個(gè)芯片中,從而實(shí)現(xiàn)真正的不同 封裝體之間的三維異質(zhì)集成封裝。

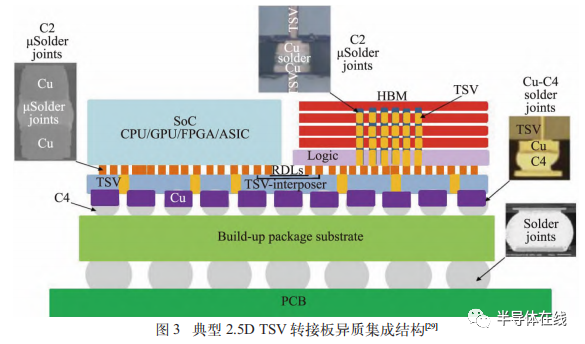

3.2 2.5D TSV轉(zhuǎn)接板異質(zhì)集成

2.5D TSV轉(zhuǎn)接板技術(shù)是為解決有機(jī)基板布線密 度不足、信號(hào)延遲大、帶寬限制等問題而開發(fā)的帶有TSV垂直互連通孔和高密度金屬布線的新型基板技 術(shù)。通過帶有TSV垂直互連通孔的無源或有源載板,實(shí)現(xiàn)多個(gè)芯片間的高密度連接,再與有機(jī)基板互連以 提高系統(tǒng)集成密度,解決芯片管腳密度與有機(jī)基板引 出結(jié)構(gòu)無法兼容的問題。典型2.5D TSV轉(zhuǎn)接板異質(zhì) 集成結(jié)構(gòu)如圖3所示,采用TSV及微凸點(diǎn)(包括可 控塌陷C4凸點(diǎn)和銅柱C2凸點(diǎn))實(shí)現(xiàn)垂直互連,通過 高密度RDL實(shí)現(xiàn)水平互連,實(shí)現(xiàn)中央處理器(CPU)、 圖形處理器(GPU)、高帶寬內(nèi)存(HBM)等Chiplet的 異質(zhì)集成。

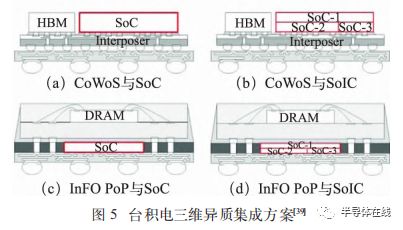

IMEC、Fraunhofer、Leti、IME、臺(tái)積電、聯(lián)電等半導(dǎo) 體頂尖研究機(jī)構(gòu)和企業(yè)均陸續(xù)推出各自的2.5D TSV轉(zhuǎn)接板異質(zhì)集成方案。其中,臺(tái)積電于2011年推出的2.5D封裝襯底上晶圓級(jí)芯片封裝(CoWoS)技術(shù)最具 代表性,并成功實(shí)現(xiàn)大規(guī)模量產(chǎn)。該技術(shù)通過芯片到 晶圓工藝將芯片連接至硅轉(zhuǎn)接板上,再把堆疊芯片與 基板連接,實(shí)現(xiàn)芯片-轉(zhuǎn)接板-基板的三維封裝結(jié) 構(gòu)。該技術(shù)采用前道工藝在轉(zhuǎn)接板上制作高密度的互 連線,通過轉(zhuǎn)接板完成多個(gè)芯片的互連,可以大幅提 高系統(tǒng)集成密度,降低封裝厚度。基于臺(tái)積電的CoWoS技術(shù),Xilinx推出“Virtex-7 2000T”產(chǎn)品,該產(chǎn) 品將4個(gè)采用28 nm工 藝的現(xiàn)場(chǎng)可編程 門 陣 列 (FPGA) 芯片通過TSV轉(zhuǎn)接板互連,實(shí)現(xiàn)了在單個(gè)FPGA模組里集成數(shù)個(gè)FPGA的功能,超越了摩爾定 律的限制[31]。此后推出的基于CoWoS技術(shù)的產(chǎn)品包括 華為海思Hi616、英偉達(dá)TESLA顯卡和Fujistu A64FX超級(jí)計(jì)算芯片等。針對(duì)高性能計(jì)算應(yīng)用,臺(tái)積電于2020年進(jìn)一步開發(fā)了集成深溝槽電容 (DTC)的CoWoS技術(shù),其電容密度高達(dá)300 nF/mm2,漏電流小 于1 fA/μm2,該CoWoS具有更低的功耗和更好的數(shù) 據(jù)傳輸性能。到2021年,CoWoS技術(shù)已經(jīng)發(fā)展至第 五代,轉(zhuǎn)接板面積可達(dá)2 500 mm2,單個(gè)轉(zhuǎn)接板可集 成8個(gè)HBM和超過3個(gè)芯片級(jí)系統(tǒng)(SoC)/Chiplet模 塊;同時(shí)集成DTC以增強(qiáng)電源完整性,并發(fā)展出相應(yīng) 的5層亞微米尺度的銅RDL互連技術(shù)。近年來,人工 智能、高性能計(jì)算等對(duì)超強(qiáng)算力的需求迅猛增長(zhǎng),大 力推動(dòng)了2.5D TSV轉(zhuǎn)接板封裝技術(shù)的應(yīng)用。通過異 質(zhì)集成CPU、GPU和HBM獲得更高的帶寬密度,成 為提高算力的關(guān)鍵途徑。根據(jù)對(duì)TOP500超級(jí)計(jì)算機(jī) 系統(tǒng)的分析,2020年基于CoWoS技術(shù)的總計(jì)算能力 占所有TOP500系統(tǒng)總計(jì)算能力的50%以上。

3.3基于TSV和微凸點(diǎn)的三維異質(zhì)集成

3D集成將芯片在垂直方向通過TSV和微凸點(diǎn)進(jìn) 行堆疊,可以實(shí)現(xiàn)高性能、低功耗、高寬帶、小形狀因 子等目的,充分發(fā)揮晶圓級(jí)堆疊和TSV技術(shù)互連線長(zhǎng) 度短的優(yōu)勢(shì)。該技術(shù)早期主要應(yīng)用于動(dòng)態(tài)隨機(jī)存取存 儲(chǔ)器(DRAM)、高帶寬內(nèi)存等。典型產(chǎn)品如2014年三 星基于TSV和微凸點(diǎn)互連量產(chǎn)的64 GB DRAM,互連TSV尺寸為7μm×50μm;與采用引線鍵合的內(nèi)存相 比,信號(hào)傳送速率提升一倍,而功耗減少一半。

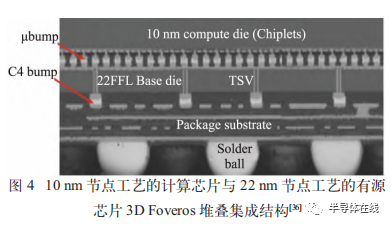

近年來,基于TSV和微凸點(diǎn)的三維集成技術(shù)不斷 拓展到邏輯芯片的三維堆疊集成。2019年,英特爾推 出基于TSV和微凸點(diǎn)的新型3D集成技術(shù)Foveros,該 技術(shù)能夠?qū)崿F(xiàn)邏輯芯片的面對(duì)面堆疊,首次將芯片堆 疊從傳統(tǒng)的無源中介層和內(nèi)存等擴(kuò)展到高性能邏輯 芯片,例如CPU、GPU和AI處理器等。10 nm節(jié) 點(diǎn)工藝的計(jì)算芯片與22 nm節(jié)點(diǎn)工藝的有源芯片3D Foveros堆疊集成結(jié)構(gòu)如圖4所示。采用Foveros封 裝技術(shù)的英特爾Lakefield處理器于2020年投入市場(chǎng)。三星也于2020年發(fā)布了X-Cube三維集成技術(shù),利用TSV和微凸點(diǎn)技術(shù)將HBM芯片與邏輯芯片進(jìn)行堆 疊,在速度、功率、效率方面實(shí)現(xiàn)顯著飛躍。

3.4基于無凸點(diǎn)混合鍵合的三維異質(zhì)集成

一直以來,3D集成廣泛采用Sn基釬料微凸點(diǎn)和TSV實(shí)現(xiàn)高效的垂直互連。然而,當(dāng)間距減小到20μm以內(nèi),熱壓鍵合過程中的細(xì)微傾斜將使釬料變形擠出 而發(fā)生橋連短路。同時(shí),液-固反應(yīng)形成的金屬間化合 物(IMC)將占據(jù)凸點(diǎn)的大部分體積,使之轉(zhuǎn)變?yōu)榇嘈?連接。并且,表面擴(kuò)散及柯肯達(dá)爾孔洞等問題的影響 急劇增加,難以進(jìn)一步縮減互連間距,微凸點(diǎn)的微型 化遭遇前所未有的瓶頸。基于Cu/絕緣層混合鍵合的無凸點(diǎn)3D集成可實(shí)現(xiàn):(1)剛性互連,避免出現(xiàn)橋 連問題;(2) 與集成電路后道工序及TSV銅互連相兼 容,無需底充膠;(3)芯片堆疊中多次熱壓工藝無影響 (銅的熔點(diǎn)為1 083℃);(4) 無脆性相IMC形成;(5) 優(yōu)異的電、熱、機(jī)械和抗電遷移性能。因此,無凸點(diǎn)Cu/絕緣層混合鍵合在超細(xì)間距(小于10μm)芯片垂直互 連中的應(yīng)用具有無可比擬的優(yōu)勢(shì)。

對(duì)于Cu-Cu直接鍵合及Cu/絕緣層混合鍵合的 研究已持續(xù)了幾十年,然而由于當(dāng)時(shí)的市場(chǎng)需求有限 并且工藝難度過大,其一直未引起過多關(guān)注。直到2015年,索尼獲得Ziptronix公司的混合鍵合技術(shù)授 權(quán),首次推出了基于無凸點(diǎn)混合鍵合的高性能圖像傳 感器產(chǎn)品。半導(dǎo)體業(yè)界逐漸意識(shí)到混合鍵合將成為 突破微凸點(diǎn)微型化瓶頸的有效途徑。此后英特爾、臺(tái) 積電、華為、長(zhǎng)江存儲(chǔ)、IMEC、IME、Leti等領(lǐng)先機(jī)構(gòu)和 企業(yè)陸續(xù)對(duì)混合鍵合技術(shù)進(jìn)行了深入研發(fā)。英特爾 推出了基于無凸點(diǎn)混合鍵合的Foveros三維集成技 術(shù),但未披露過多細(xì)節(jié)。臺(tái)積電則較為詳細(xì)地公布了 其基于無凸點(diǎn)混合鍵合的三維異質(zhì)集成技術(shù),將之稱 為集成片上系統(tǒng)(SoIC),其混合鍵合工藝溫度與 無鉛焊料回流工藝溫度相當(dāng)。SoIC集成采用超薄芯 片,以實(shí)現(xiàn)大深寬比和高密度的TSV互連。為此,臺(tái)積 電提出并優(yōu)化2條工藝路線:(1)芯片-晶圓鍵合后再 背面露銅,首先將芯片面對(duì)面混合鍵合,隨后對(duì)芯片 背面減薄,背面露銅后沉積絕緣層和Cu盤,再次與另 一芯片Cu-Cu鍵合并重復(fù)以上工藝,實(shí)現(xiàn)芯片堆疊;(2)背面露銅后再進(jìn)行芯片-芯片鍵合,首先將晶圓臨 時(shí)鍵合于玻璃載板并進(jìn)行背面減薄,背面露銅后沉積 絕緣層和Cu盤,晶圓與載板解鍵合后切割成單顆芯 片,單顆芯片再分別進(jìn)行Cu-Cu鍵合以實(shí)現(xiàn)芯片堆 疊。基于混合鍵合的SoIC及其改進(jìn)版本SoIC+可以 獲得超細(xì)間距和超高密度的互連。它比倒裝芯片技術(shù) 具有更好的電氣性能,插入損耗幾乎為零,遠(yuǎn)遠(yuǎn)小于2D并排倒裝芯片技術(shù)的插入損耗。與臺(tái)積電采用的傳 統(tǒng)微凸點(diǎn)3D TSV集成對(duì)比,無凸點(diǎn)SoIC集成的12層存儲(chǔ)器在垂直方向上的尺寸下降高達(dá)64%,帶寬密 度則增加28%,而能源消耗下降19%。

由此可見,無凸點(diǎn)3D集成技術(shù)可實(shí)現(xiàn)超高密度 的芯片垂直互連,繼續(xù)推動(dòng)芯片向高性能、微型化和 低功耗方向發(fā)展。同時(shí),以臺(tái)積電無凸點(diǎn)3D集成SoIC技術(shù)為例,SoIC可與CoWoS、集成扇出型封裝等技術(shù) 實(shí)現(xiàn)深度異質(zhì)集成整合,三維異質(zhì)集成方案如圖5所 示。原來需要放到1個(gè)片上系統(tǒng)SoC芯片上實(shí)現(xiàn)的 方案,現(xiàn)在可以轉(zhuǎn)換成多個(gè)Chiplet來做。這些分解開 的Chiplet再通過集成SoIC實(shí)現(xiàn)靈活整合,其芯片產(chǎn) 品具有設(shè)計(jì)成本低、速度快、帶寬足和低功耗的優(yōu)勢(shì)。因此,基于無凸點(diǎn)混合鍵合的三維異質(zhì)集成技術(shù)若真 正實(shí)現(xiàn)量產(chǎn),無疑是集成電路行業(yè)劃時(shí)代的革新技 術(shù)。然而,當(dāng)前該技術(shù)在設(shè)計(jì)規(guī)則、平整度、清潔度、材 料選擇和對(duì)準(zhǔn)等方面仍面臨諸多挑戰(zhàn)。

4基于玻璃基板的異質(zhì)集成方案

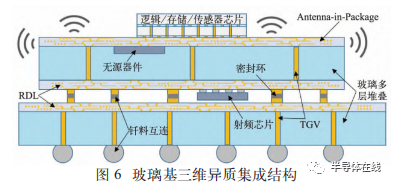

玻璃基板具有較多優(yōu)勢(shì):玻璃的低損耗使其傳輸 性能優(yōu)良,高平整度的表面可以進(jìn)行細(xì)間距的布線, 以及可調(diào)的熱膨脹系數(shù)使得異質(zhì)集成的應(yīng)力問題減 少。TGV的加工比TSV更為簡(jiǎn)單高效,機(jī)械、激光或 刻蝕等方法組合使用,均可批量進(jìn)行玻璃打孔。由于 玻璃本身的絕緣特性,僅需沉積粘附層與種子層即可 進(jìn)行電鍍填充。同時(shí),玻璃基板封裝可以通過玻璃面板級(jí)工藝進(jìn)行大批量的制造,具有成本優(yōu)勢(shì)。玻璃基 三維異質(zhì)集成結(jié)構(gòu)如圖6所示。

4.1基于TGV及RDL的異質(zhì)集成

佐治亞理工學(xué)院在2014年提出的三維極薄玻璃 轉(zhuǎn)接板厚度約為30~50μm,轉(zhuǎn)接板位于三維堆疊存 儲(chǔ)芯片與邏輯芯片之間,取消了邏輯芯片的TSV通 孔,其TGV間距為20~50μm,與3D-IC中所需的TSV間距一致。與此同時(shí),TGV展示出了更低的插入 損耗、更小的延時(shí)和串?dāng)_。三維極薄玻璃轉(zhuǎn)接板技術(shù) 可有效地降低成本及工藝難度,提升轉(zhuǎn)接板整體性能 并降低整體厚度。欣興電子在2014年提出玻璃轉(zhuǎn)接板 嵌入式載板,將厚度為100μm、孔徑為30μm的玻 璃轉(zhuǎn)接板埋入層壓板后進(jìn)行標(biāo)準(zhǔn)的層壓板工藝,實(shí)現(xiàn) 轉(zhuǎn)接板與層壓板的互連。此結(jié)構(gòu)減少了焊球數(shù)量,在 使整體封裝結(jié)構(gòu)更薄的同時(shí)減少了底填所帶來的熱 膨脹問題,可以減少傳統(tǒng)工藝中轉(zhuǎn)接板與基板組裝造 成的損耗,采用鍍銅而不是焊料連接的方式將轉(zhuǎn)接板 與基板直接連接,可以提高可靠性和電性能。2016年, 格羅方德、IBM以及加州大學(xué)伯克利分校聯(lián)合發(fā)表了 針對(duì)系統(tǒng)小型化的端到端集成的多芯片玻璃轉(zhuǎn)接板 方案。該方案的TGV最終高度為55μm,上、下直徑 分別為25μm和12μm,在芯片鍵合端采用大馬士革工 藝制造最小特征尺寸為2.5μm的金屬布線。這項(xiàng)工作成 功地將TSV轉(zhuǎn)接板的設(shè)計(jì)方案復(fù)刻到TGV轉(zhuǎn)接板中, 在轉(zhuǎn)接板的上方利用大馬士革工藝制造精細(xì)銅布線。

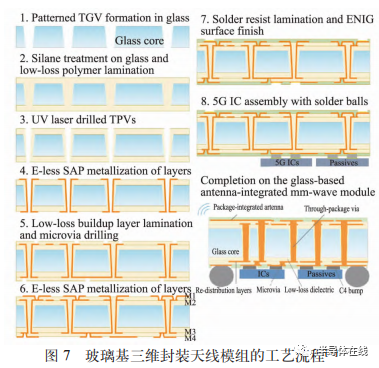

2020年,佐治亞理工學(xué)院發(fā)表了28 GHz頻段的 面板級(jí)超薄玻璃基片上的AiP異質(zhì)集成,玻璃基三 維封裝天線模組的工藝流程如圖7所示。在玻璃基 板上制作的八木-宇田天線,其中心頻率為25.85 GHz, 分?jǐn)?shù)帶寬為28.2%,覆蓋了28 GHz頻段,基板的背面 集成了有源集成電路以及離散無源組件。天線在目標(biāo) 頻率范圍內(nèi)還具有廣角主瓣,具備良好的信號(hào)發(fā)射和 接收覆蓋能力。模塊級(jí)表征結(jié)果顯示其具有低互連信 號(hào)損耗,在28 GHz時(shí)TPV損耗為0.021 dB。此項(xiàng)工作 表明玻璃基AiP異質(zhì)集成可以為毫米波通信模組提 供1個(gè)高性能的解決方案。本文作者團(tuán)隊(duì)探索了多 層玻璃的天線集成技術(shù),采用激光誘導(dǎo)濕法刻蝕玻璃 技術(shù)制備TGV,隨后在玻璃表面進(jìn)行金屬布線,并采 用釬料進(jìn)行多層玻璃堆疊鍵合,開發(fā)出采用5層玻璃 堆疊的方案,制作工作頻段在75~90 GHz的天線。輻 射部分由4個(gè)微帶貼片組成,封裝總尺寸為10 mm×9 mm×1 mm。TGV和RDL形成的互連可實(shí)現(xiàn)層間的 直接傳輸和信號(hào)耦合,以提高傳輸效率。此外,低介電 常數(shù)確保了玻璃的微弱表面波效應(yīng)。實(shí)驗(yàn)和仿真結(jié)果 表明,該系統(tǒng)的回波損耗小于25 dB,增益大于7 dBi。

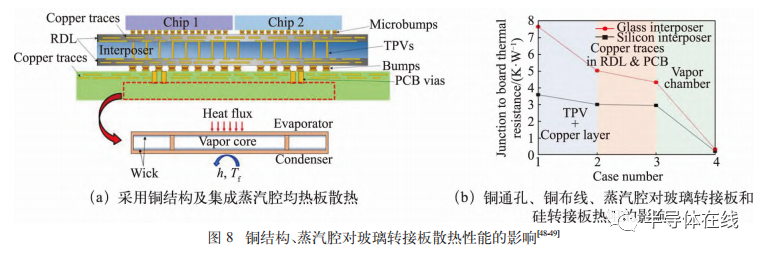

然而,玻璃的主要問題在于導(dǎo)熱系數(shù)低導(dǎo)致的散 熱不良。CHO等人研究發(fā)現(xiàn),玻璃轉(zhuǎn)接板通孔、接 地銅結(jié)構(gòu)等可提供有效的熱傳導(dǎo)途徑,引入大量銅通 孔、銅布線等結(jié)構(gòu)可以顯著提高玻璃轉(zhuǎn)接板的散熱性 能,同時(shí)可實(shí)現(xiàn)在硅材料中難以實(shí)現(xiàn)的邏輯器件和存 儲(chǔ)器件之間的良好熱隔離。在PCB中引入蒸汽腔均熱 板可以進(jìn)一步提高散熱性能,克服玻璃的低熱導(dǎo)率問 題,獲得和硅轉(zhuǎn)接板幾乎相當(dāng)?shù)纳嵝阅堋c~結(jié)構(gòu)、蒸 汽腔對(duì)玻璃轉(zhuǎn)接板散熱性能的影響如圖8所示。

4.2埋入玻璃式扇出型異質(zhì)集成

佐治亞理工學(xué)院在2019年針對(duì)高效高帶寬異質(zhì) 集成發(fā)表了TGV三維封裝方案———嵌入平板玻璃技 術(shù),實(shí)現(xiàn)了邏輯芯片和存儲(chǔ)芯片的面對(duì)面式三維集 成。100μm厚度的邏輯芯片被埋入110μm深度的玻 璃盲槽中,并將介質(zhì)真空壓入芯片與盲槽的側(cè)壁間, 再用光刻打開開口,實(shí)現(xiàn)其與存儲(chǔ)芯片的直接互連。相較于目前的2.5D封裝結(jié)構(gòu)和3D-IC,這種結(jié)構(gòu)有著 更高的I/O密度、更佳的性能、更低的成本以及更好的 可靠性。該種結(jié)構(gòu)無需對(duì)處理器芯片進(jìn)行TSV工藝,同 時(shí)可實(shí)現(xiàn)超短互連和高效的超高帶寬,具有較大的潛力。

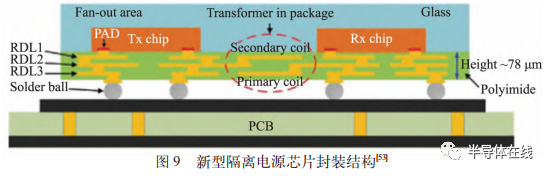

本文作者研究團(tuán)隊(duì)基于玻璃成孔工藝開發(fā)了埋 入玻璃式扇出型(eGFO)異質(zhì)集成技術(shù),并成功應(yīng)用于 電源芯片、濾波器、超聲換能器、毫米波雷達(dá)天線等集成封裝。其中新型隔離電源芯片封裝結(jié)構(gòu)如圖9所 示,基于eGFO異質(zhì)集成技術(shù)將接收和發(fā)射線圈通過 封裝表面上的RDL制成的微型變壓器異質(zhì)集成在一 起。電源芯片實(shí)現(xiàn)了46.5%的峰值轉(zhuǎn)換效率和最大1.25 W的輸出功率,而封裝尺寸僅有5 mm×5 mm,在 目前所報(bào)道的無磁芯隔離電源芯片中效率和功率密 度均為最高。針對(duì)超聲換能器陣列不耐高溫的特性, 團(tuán)隊(duì)開發(fā)了低溫RDL優(yōu)先的eGFO技術(shù)。通過臨時(shí) 鍵合在載板上制作3層RDL及銅柱凸點(diǎn),使用低固化 溫度的各向異性導(dǎo)電膠實(shí)現(xiàn)超聲換能器陣列與臨時(shí) 玻璃基板之間的電學(xué)連接;以玻璃代替有機(jī)塑膜材 料,通過膠帶轉(zhuǎn)移法制作了包含超聲換能器陣列器件 的重構(gòu)晶圓;通過晶圓級(jí)鍵合實(shí)現(xiàn)了超聲換能器陣列 與臨時(shí)玻璃基板之間的批量鍵合,避免了在長(zhǎng)期預(yù)熱 條件下的失效問題。

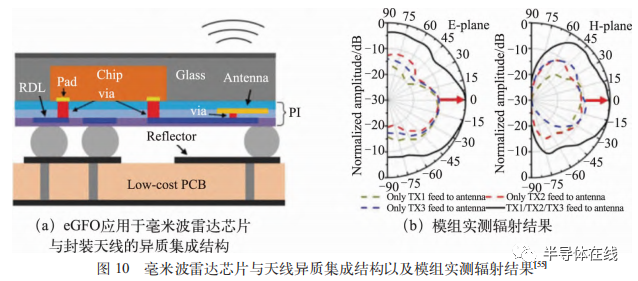

同時(shí),eGFO還可應(yīng)用于毫米波雷達(dá)芯片和封裝 天線的異質(zhì)集成,其結(jié)構(gòu)如圖10(a)所示,模組實(shí)測(cè) 輻射結(jié)果如圖10(b)所示。仿真及實(shí)測(cè)結(jié)果表明,接收 天線陣列實(shí)現(xiàn)了10.5 dBi的增益,發(fā)射天線陣列實(shí)現(xiàn) 了9 dBi的增益。基于此技術(shù),中國電子科技集團(tuán)公司 第三十八研究所在ISSCC 2021國際固態(tài)電路會(huì)議上 發(fā)布了一款高性能的77 GHz毫米波芯片及模組,其 集成封裝尺寸僅為23.1 mm×10.7 mm×220μm,在國際 上首次實(shí)現(xiàn)2顆3發(fā)4收毫米波芯片及10路毫米波 天線單封裝集成,其探測(cè)距離達(dá)到38.5 m,刷新了全球 毫米波封裝天線最遠(yuǎn)探測(cè)距離的新紀(jì)錄。

5 結(jié)束語

異質(zhì)集成技術(shù)開發(fā)與整合的關(guān)鍵在于融合實(shí)現(xiàn) 多尺度、多維度的芯片互連,芯片在垂直方向上的TSV、TGV互連技術(shù)與水平方向上的RDL互連技術(shù) 相配合,可將不同尺寸、材料、制程和功能的Chiplet異 質(zhì)集成整合到1個(gè)封裝體中,從而提高帶寬、延遲和電 源效率,為高性能計(jì)算、人工智能和智慧終端等提供 更小尺寸和更高性能的芯片。

TSV作為三維異質(zhì)集成的核心技術(shù),其關(guān)鍵尺寸 需要不斷地縮小,細(xì)小直徑、高深寬比TSV加工的主 要難點(diǎn)包括:形成連續(xù)均勻的絕緣層/粘附阻擋層/種子層和無缺陷的超共形電鍍Cu填充等。通過TSV與RDL互連技術(shù)的融合,基于TSV互連的晶圓級(jí)封 裝、2.5D TSV轉(zhuǎn)接板、微凸點(diǎn)3D集成和無凸點(diǎn)3D集 成等異質(zhì)集成方案相繼被推出,并在高端可編程器 件、圖像處理器、存儲(chǔ)芯片以及傳感器芯片等領(lǐng)域?qū)?現(xiàn)量產(chǎn)。

目前,無凸點(diǎn)3D集成技術(shù)可實(shí)現(xiàn)超高帶寬密度 的芯片垂直互連,并可與其他封裝技術(shù)實(shí)現(xiàn)深度異質(zhì) 集成整合,將分解開的Chiplet互連封裝成片上集成系 統(tǒng),在降低芯片設(shè)計(jì)成本和芯片功耗的同時(shí)提升帶寬 和計(jì)算速度。基于無凸點(diǎn)混合鍵合的三維異質(zhì)集成技 術(shù)若真正實(shí)現(xiàn)量產(chǎn),無疑是集成電路行業(yè)劃時(shí)代的革新技術(shù)。然而,當(dāng)前該技術(shù)在界面設(shè)計(jì)規(guī)則、平整度、 清潔度和材料選擇等方面仍面臨諸多挑戰(zhàn)。

基于玻璃TGV的轉(zhuǎn)接板異質(zhì)集成的優(yōu)勢(shì)包括:玻璃表面較高的平整度可以進(jìn)行細(xì)間距的RDL布線;玻璃的低損耗特性使得TGV/RDL傳輸性能優(yōu)良;玻 璃具有可調(diào)的熱膨脹系數(shù),使得異質(zhì)集成應(yīng)力問題減 少;同時(shí)玻璃轉(zhuǎn)接板可以通過玻璃面板級(jí)工藝進(jìn)行大 批量制造而具有成本優(yōu)勢(shì)。因此,這一技術(shù)在5G通訊 射頻器件、無源器件、MEMS器件等領(lǐng)域具有廣闊的 應(yīng)用前景。

審核編輯 :李倩

-

傳感器

+關(guān)注

關(guān)注

2548文章

50740瀏覽量

752147 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7455瀏覽量

163623 -

人工智能

+關(guān)注

關(guān)注

1791文章

46896瀏覽量

237670

原文標(biāo)題:芯片三維互連技術(shù)及異質(zhì)集成研究進(jìn)展

文章出處:【微信號(hào):深圳市賽姆烯金科技有限公司,微信公眾號(hào):深圳市賽姆烯金科技有限公司】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

一文看懂陶瓷穿孔三維互連(TCV)技術(shù)

從發(fā)展歷史、研究進(jìn)展和前景預(yù)測(cè)三個(gè)方面對(duì)混合鍵合(HB)技術(shù)進(jìn)行分析

三維堆疊封裝新突破:混合鍵合技術(shù)揭秘!

柔性基板異質(zhì)集成系統(tǒng)的印刷互連技術(shù)

硅通孔三維互連與集成技術(shù)

三維打印技術(shù)原理

泰來三維 工廠三維掃描建模技術(shù)服務(wù)

泰來三維|三維激光掃描技術(shù)在古建筑保護(hù)中的應(yīng)用

激光距離選通三維成像技術(shù)研究進(jìn)展綜述

頭盔三維掃描和3D打印在頭盔受力研究中的技術(shù)應(yīng)用

上海微系統(tǒng)所在硅基磷化銦異質(zhì)集成片上光源方面取得重要進(jìn)展

泰來三維|文物三維掃描,文物三維模型怎樣制作

農(nóng)業(yè)輪式機(jī)器人三維環(huán)境感知技術(shù)研究進(jìn)展

泰來三維|見過三維掃描烏賊嗎?三維掃描助力仿生設(shè)計(jì)學(xué)研究

淺談三維單片異構(gòu)集成的發(fā)展歷程

芯片三維互連技術(shù)及異質(zhì)集成研究進(jìn)展

芯片三維互連技術(shù)及異質(zhì)集成研究進(jìn)展

評(píng)論