1、數字電路模塊和模擬電路模塊之間的干擾

如果模擬電路射頻和數字電路單獨工作,可能各自工作良好。但是,一日將二者放在同一塊電路板上,使用同一個電源一起工作,整個系統很可能就不穩定。這主要是因為數字信號頻繁地在地和正電源>3V之間擺動,而且周期特別短,常常是納秒級的。由于較大的振幅和較短的切換時間。使得這些數字信號包含大量且獨立于切換頻率的高頻成分。在模擬部分,從無線調諧回路傳到無線設備接收部分的信號一般小于1uV。因此數字信號與射頻信號之間的差別會達到120dB。顯然,如果不能使數字信號與射頻信號很好地分離。微弱的射頻信號可能遭到破壞,這樣一來,無線設備工作性能就會惡化,甚至完全不能工

作。

2、供電電源的噪聲干擾

射頻電路對于電源噪聲相當敏感,尤其是對毛刺電壓和其他高頻諧波。微控制器會在每個內部時鐘周期內短時間突然吸人大部分電流,這是由于現代微控制器都采用CMOS工藝制造。因此。假設一個微控制器以1MHz的內部時鐘頻率運行,它將以此頻率從電源提取電流。如果不采取合適的電源去耦.的地方必將引起電源線上的電壓毛刺。如果這些電壓毛刺到達電路RF部分的電源引腳,嚴重時可能導致工作失效。

3、不合理的地線

如果RF電路的地線處理不當,可能產生一些奇怪的現象。對于數字電路設計,即使沒有地線層,大多數數字電路功能也表現良好。而在RF頻段,即使一根很短的地線也會如電感器一樣作用。粗略地計算,每毫米長度的電感量約為1nH433MHz時10toniPCB線路的感抗約27Ω。如果不采用地線層,大多數地線將會較長,電路將無法具有設計的特性。

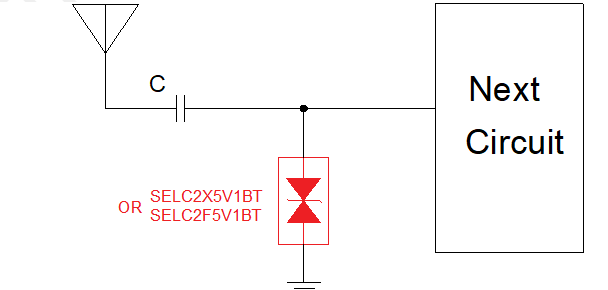

4、天線對其他模擬電路部分的輻射干擾

在PCB電路設計中,板上通常還有其他模擬電路。例如,許多電路上都有模,數轉換 ADC或數/模轉換器DAC。射頻發送器的天線發出的高頻信號可能會到達ADC的模擬淙父恕 R蛭魏蔚緶廢唄范伎贍莧縑煜咭謊3齷蚪郵脖F信號。如果ADC輸入端的處理不合理,RE信號可能在ADC輸入的ESD二極管內自激。從而引起ADC偏差。

在設計RF布局時,必須優先滿足以下幾個總原則:

1、盡可能地把高功率RF放大器HPA和低噪音放大器LNA隔離開來,簡單地說,就是讓高功率RF發射電路遠離低功率RF接收電路:

2、確保PCB板上高功率區至少有一整塊地,最好上面沒有過孔,當然,銅箔面積越大越好;

3、電路和電源去耦同樣也極為重要:

4、RF輸出通常需要遠離RF輸入;

5、敏感的模擬信號應該盡可能遠離高速數字信號和RF信:

物理分區、電氣分區設計分區

可以分解為物理分區和電氣分區。物理分區主要涉及元器件布局、朝向和屏蔽等問題;電氣分區可以繼續分解為電源分配、RF走線、敏感電路和信號以及接地等的分區。

1、我們討論物理分區問題

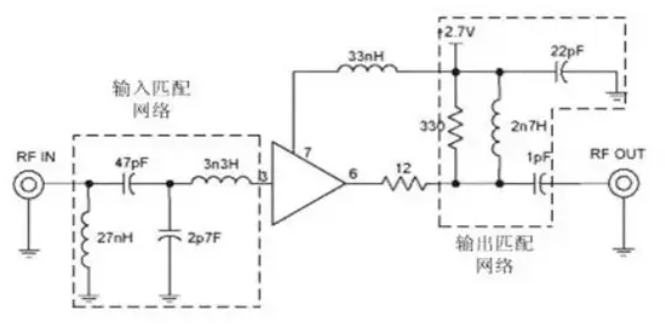

元器件布局是實現一個優秀RF設計的關鍵,最有效的技術是首先固定位于RF路徑上的元器件,并調整其朝向以將RF路徑的長度減到最小,使輸入遠離輸出,并盡可能遠地分離高功率電路和低功率電路。

最有效的電路板堆疊方法是將主接地面主地安排在表層下的第二層,并盡可能將RE線走在表層上。將RF路徑上的過孔尺寸減到最小不僅可以減少路徑電感,而且還可以減少主地上的虛焊點,并可減少RF能量泄漏到層疊板內其他區域的機會。在物理空間上,像多級放大器這樣的線性電路通常足以將多個RF區之間相互隔離開來,但是雙工器、混頻器和中頻放大器/混頻器總是有多個RF/IF信號相互干擾,因此必須小心地將這一影響減到最小。

2、F與F走線應盡可能走一字交叉,并盡可能在它們之間隔一塊地

正確的RF路徑對整塊PCB板的性能而言非常重要,這也就是為什么元器件布局通常在手機PCB板設計中占大部分時間的原因。在手機PCB板設計上,通常可以將低噪音放大器電路放在PCB板的某一面,而高功率放大器放在另一面,并最終通過雙工器把它們在同一面上連接到RF端和基帶處理器端的天線上。

3、恰當和有效的芯片電源去耦也非常重要

許多集成了線性線路的RF芯片對電源的噪音非常敏感,通常每個芯片都需要采用高達四個電容和一個隔離電感來確保濾除所有的電源噪音。一塊集成電路或放大器常常帶有一個開漏極輸出,因此需要一個上拉電感來提供一個高阻抗RF負載和一個低阻抗直流電源,同樣的原則也適用于對這一電感端的電源進行去耦。

有些芯片需要多個電源才能工作,因此你可能需要兩到三套電容和電感來分別對它們進行去耦處理,電感極少并行靠在一起,因為這將形成一個空芯變壓器并相互感應產生干擾信號,因此它們之間的距離至少要相當于其中一個器件的高度,或者成直角排列以將其互感減到最小。

4、電氣分區原則大體上與物理分區相同,但還包含一些其它因素手機的某些部分采用不同工作電壓,并借助軟件對其進行控制,以延長電池工作壽命。這意味著手機需要運行多種電源,而這給隔離帶來了更多的問題。

電源通常從連接器引入,并立即進行去耦處理以濾除任何來自線路板外部的噪聲,然后再經過一組開關或穩壓器之后對其進行分配。手機PCB板上大多數電路的直流電流都相當小,因此走線寬度通常不是問題,不過,必須為高功率放大器的電源單獨走一條盡可能寬的大電流線,以將傳輸壓降減到最低。為了避免太多電流損耗,需要采用多個過孔來將電流從某一層傳遞到另一層。此外,如果不能在高功率放大器的電源引腳端對它進行充分的去耦。那么高功率噪聲將會輻射到整塊板上,并帶來各種各樣的問題。

高功率放大器的接地相當關鍵,并經常需要為其設計一個金屬屏蔽罩。在大多數情況下,同樣關鍵的是確保RF輸出遠離RF輸入。這也適用于放大器、緩沖器和濾波器。在最壞情況下,如果放大器和緩沖器的輸出以適當的相位和振幅反饋到它們的輸入端,那么它們就有可能產生自激振蕩。在最好情況下,它們將能在任何溫度和電壓條件下穩定地工作。

實際上,它們可能會變得不穩定,并將噪音和互調信號添加到RF信號上。如果射頻信號線不得不從濾波器的輸入端繞回輸出端,這可能會嚴重損害濾波器的帶通特性。為了使輸入和輸出得到良好的隔離,首先必須在濾波器周圍布一圈地,其次濾波器下層區域也要布一塊地,并與圍繞濾波器的主地連接起來。把需要穿過濾波器的信號線盡可能遠離濾波器引腳也是個好方法。

5、要保證不增加噪聲必須從以下幾個方面考慮

首先,控制線的期望頻寬范圍可能從DC直到2MHz,而通過濾波來去掉這么寬頻帶的噪聲幾乎是不可能的:其次,VCO控制線通常是一個控制頻率的反饋回路的一部分,它在很多地方都有可能引入噪聲,因此必須非常小心處理VCO控制線。要確保RF 走線下層的地是實心的,而且所有的元器件都牢固地連到主地上,并與其它可能帶來噪聲的走線隔離開來。

此外,要確保VCO的電源已得到充分去耦,由于VCO的RF輸出往往是一個相對較高的電平,VCO輸出信號很容易干擾其它電路,因此必須對VCO加以特別注意。事實上,VCO往往布放在RF區域的末端,有時它還需要一個金屬屏蔽罩。

諧振電路一個用于發射機,另一個用于接收機與VCO有關,但也有它自己的特點。簡單地講,諧振電路是一個帶有容性二極管的并行諧振電路,它有助于設置VCO工作頻率和將語音或數據調制到RF信號上。所有VCO的設計原則同樣適用干諧振電路。由于諧振電

路含有數量相當多的元器件、板上分布區域較寬以及通常運行在一個很高的RF頻率下,因此諧振電路通常對噪聲非常敏感。

信號通常排列在芯片的相鄰腳上,但這些信號引腳又需要與相對較大的申感和電容配

合才能工作,這反過來要求這些電感和電容的位置必須靠得很近,并連回到一個對噪聲很敏感的控制環路上。要做到這點是不容易的。

自動增益控制AGC放大器同樣是一個容易出問題的地方,不管是發射還是接收電路都會有AGC放大器。AGC放大器通常能有效地濾掉噪聲,不過由于手機具備處理發射和接收信號強度快速變化的能力,因此要求AGC電路有一個相當寬的帶寬,而這使某些關鍵電路上的AGC放大器很容易引入噪聲。設計AGC線路必須遵守良好的模擬電路設計技術,而這跟很短的運放輸入引腳和很短的反饋路徑有關,這兩處都必須遠離RF、IF或高速數字信號走線。

同樣,良好的接地也必不可少,而且芯片的電源必須得到良好的去耦。如果必須要在輸入或輸出端走一根長線,那么最好是在輸出端,通常輸出端的阻抗要低得多,而且也不容易感應噪聲。通常信號電平越高,就越容易把噪聲引入到其它電路。在所有PCB設計中,盡可能將數字電路遠離模擬電路是一條總的原則,它同樣也適用于RF PCB設計。公共模擬地和用于屏蔽和隔開信號線的地通常是同等重要的,因此在設計早期階段,仔細的計劃、考慮周全的元器件布局和徹底的布局*估都非常重要,同樣應使RF線路遠離模擬線路和一些很關鍵的數字信號,所有的RF走線、焊盤和元件周圍應盡可能多填接地銅皮,并盡可能與主地相連。如果RF走線必須穿過信號線,那么盡量在它們之間沿著RF走線布一層與主地相連的地。如果不可能的話,一定要保證它們是十字交叉的,這可將容性耦合減到最小,同時盡可能在每根RF走線周圍多布一些地,并把它們連到主地。

審核編輯黃宇

-

電源

+關注

關注

184文章

17585瀏覽量

249488 -

電路設計

+關注

關注

6665文章

2428瀏覽量

203306 -

RF

+關注

關注

65文章

3042瀏覽量

166822 -

VCO

+關注

關注

12文章

190瀏覽量

69148 -

無線射頻

+關注

關注

4文章

204瀏覽量

27004

發布評論請先 登錄

相關推薦

射頻技術rf的基本原理是什么

射頻收發器就是基帶嗎

射頻技術在無線通信領域的應用

射頻(RF)電路設計的常見問題

射頻電路基礎知識:射頻電路的基本理論和參數定義

RF無線射頻電路設計基礎

RF無線射頻電路設計基礎

評論