掌握基本的射頻微波理論知識;熟練使用 HFSS、ADS、SONNET、Cadence(virtuoso,calibre)、EMX等電磁仿真以及射頻芯片設計軟件;熟悉CMOS、GaN、GaAs、IPD 等多個廠家的工藝;具有多次射頻/微波/毫米波前端芯片的流片成功經驗。

一、基本概念

濾波器定義:

顧名思義,濾波器就是一種濾除某種波形的器件,在射頻微波中的濾波器主要是用于選擇有用信號,濾除無用信號的器件。

濾波器分類:

濾波器的分類有很多標準,主要還是基于用戶所關注的點來分類,筆者簡單總結了以下分類,僅供參考:

按照傳輸函數:切比雪夫型;橢圓函數型;巴特沃斯型;準橢圓函數型等。

按照濾波功能:低通濾波器;帶通濾波器;帶阻濾波器;高通濾波器。

按照實現結構:發夾型;階躍阻抗型;開口環型;二維碼型;糖葫蘆型等。

按照制造材料:介質濾波器;腔體濾波器,聲表濾波器,體表濾波器等。

題外話:據筆者觀察,目前IEEE上關于第三個分類的濾波器,收錄在SCI的四區居多,對于第一類修正相關理論后綜合的濾波器文章大多都能發表在SCI的1/2區。而產業界大多集中在第四類濾波器的研究上,主要是期望通過最簡單的結構,來獲得滿足系統要求的,低成本的高可靠濾波器。

濾波器的主要指標:

工作頻率(f): 主要是指用戶需要處理的信號的工作頻率,比如帶通濾波器的通帶,帶阻濾波器的阻帶便是工作頻率。

工作帶寬(BW):不特別聲明的情況下,一般是指3dB工作帶寬,即所需要選擇的信號幅度在工作頻段內與極值點(高低通濾波器則為截至頻率點)相比,幅度下降3dB時的工作頻段寬度。

插入損耗(IL):一般是指在信號通過的頻段內,信號的幅度損耗值(即二端口濾波器的輸出波與輸入波的比值取對數)。

電壓駐波比(VSWR):一般是用來衡量濾波器輸入與輸出端口出的回波多少的指標,一般1.5以下也足夠了,其意義表示僅有4%左右的能量被反射到輸入口,96%的都已經發射出去了,且與S11/S22有個同樣的作用,且可以同過散射參數變換得到(例如:端口1的VSWR=(1+S11)/(1-S11),換成數值計算時需要注意的是VSWR和S11的單位是不一致的,前者為功率表示,后者電壓表示,因此后者換算成數值時需要把20除到等式另一側,即相對VSWR的換算多了一個開根號的處理)。

帶外抑制度:帶外抑制是指對通帶以外的信號的抑制程度,有時候也會和矩形系數來表示。此類指標在系統設計是比較關注的,后續設計我們也會重點介紹相關的傳輸零點引入技術,來實現對帶外信號的抑制。

二、濾波器設計理論

微波基礎以及濾波器的理論學習,推薦大家參看:

——Pozar的《微波工程》;

——土井淳的《電磁場基本原理66課》;

——Jia-Sheng Hong的《Microstripp Filter For RF/Microwave Aplplication》;

——Protap Pramanick的《Modern RF and Microwave Filter Design》;

以帶通濾波器設計理論為例,目前主要有兩條比較實用的底層數學邏輯去設計所需濾波曲線:

由集中參數低通原型出發,經過頻率變換獲得集中參數電路模型,然后用不同的結構去實現濾波器的設計。這類方法對于仿真工具匱乏的年代的工程師們是十分受用的。對于集總型濾波器可以直接按照變換得到的電感電容值去實現相應的實際濾波器;而對于微帶濾波器大多還需要根據kurda變換,將電感電容值變換成實際的電長度和特征阻抗值,最終得到符合要求的分布式濾波器的實際尺寸。

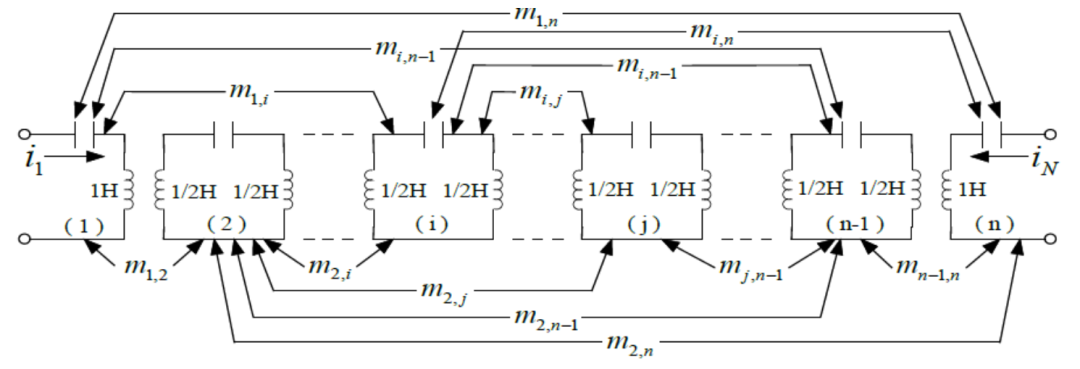

由耦合矩陣出發,根據所需的耦合系數去設計帶通濾波器。隨著電磁仿真軟件的發展,工程師們可以在仿真軟件中輕松提取各類特征阻抗,電長度,諧振器諧振頻率,諧振器間耦合系數。因此當設計師拿到下發的設計任務后,只需要更加指標綜合出濾波器的耦合矩陣,得到耦合系數(合理的數值)便可以容易地設計出滿足要求的。本文搬運一個耦合型濾波器的經典理論來拋磚引玉,歡迎大家討論:

本文搬運一個耦合型濾波器的經典理論來拋磚引玉,歡迎大家討論:

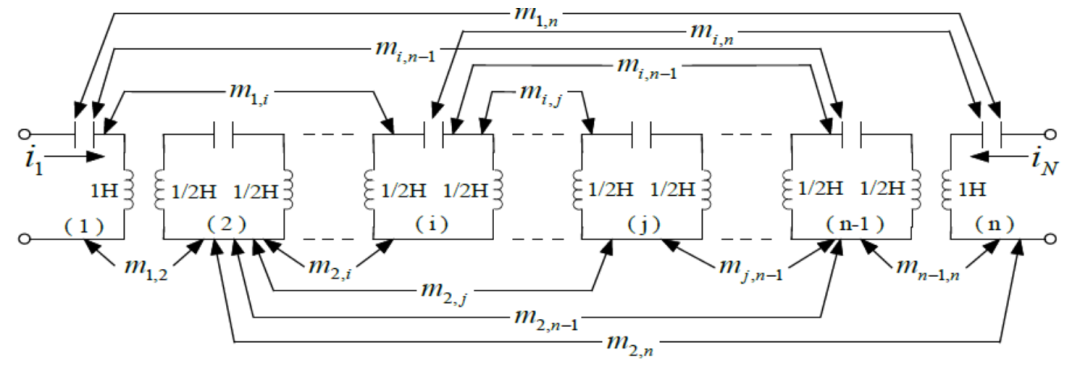

耦合型濾波器的低通原型電路

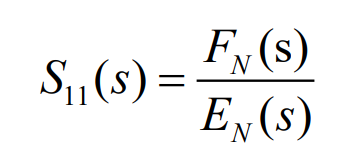

針對上圖中的耦合型濾波網絡,假設不存在傳輸損耗,此時上面的散射參數矩陣可以得到如下公式:

其中,n是諧振器個數。E、P和F是以為復變量的多項式,ω0是歸一化頻率。

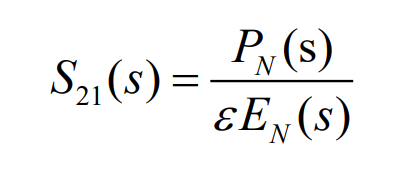

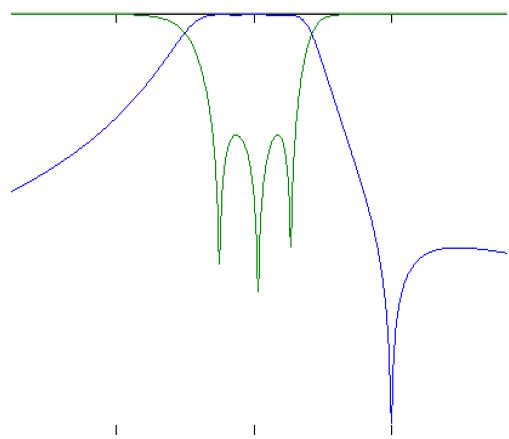

此時濾波器的傳輸系數:

其中PN(S)是以s為變量的m階多項式(m

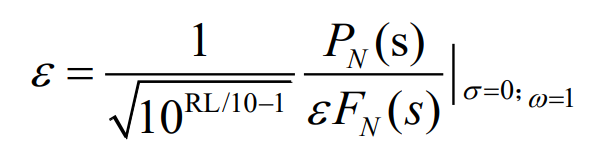

其中RL表示濾波器的回波損耗(Retrun Loss)。上文提到的按照響應函數對濾波器分類下表給出了常見的傳輸函數S21的分類:

表1 常見濾波器傳輸函數及濾波器分類

同理,由上面的散射矩陣可得反射系數為:

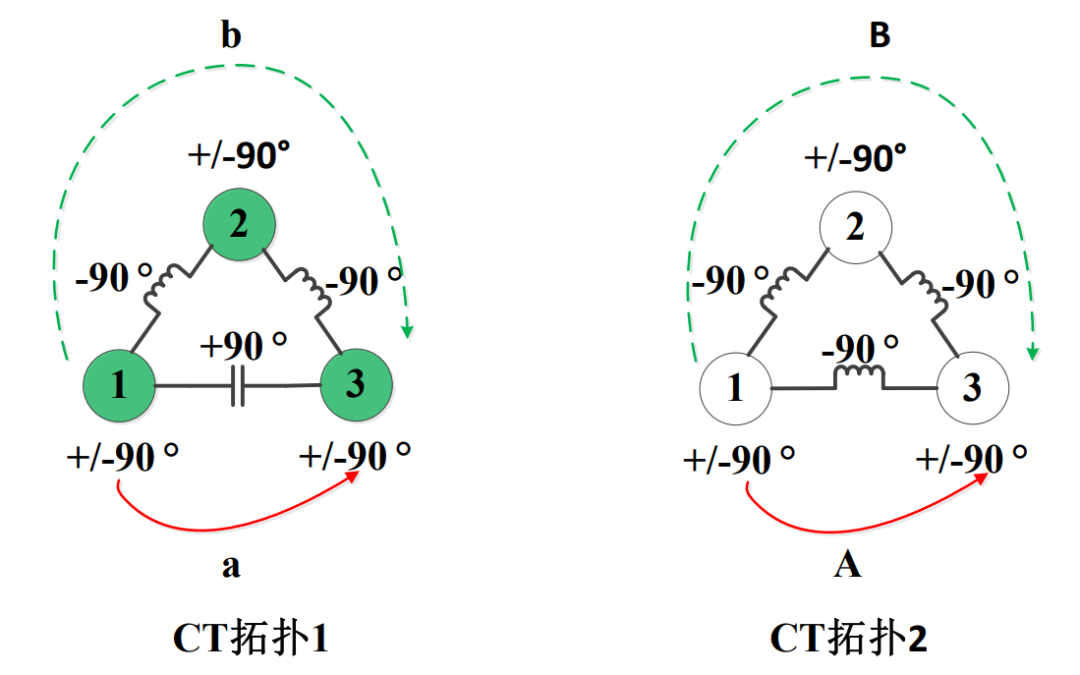

其中FN是n階首項為1的多項式,EN是歸一化Hurwitz多項式。并滿足下面的譜方程:

使濾波器反射系數為零的復頻率點被稱作反射零點或傳輸極點。

看完這些理論大家先不要慌,不要覺得復雜。既然數學本身不是為了讓事情更加復雜,而是為了讓事情變得更加簡明,同時我們很多時候設計濾波器就是在調試濾波器的極點和零點所在位置,那么對于傳輸零點與極點的設計我們用什么數學方法更加簡單呢?

有!筆者認為答案是:耦合矩陣!!!(后期我們的芯片濾波器也是先通過軟件綜合出耦合矩陣,再變換到集中元件,最后做EM仿真得到最終版圖)

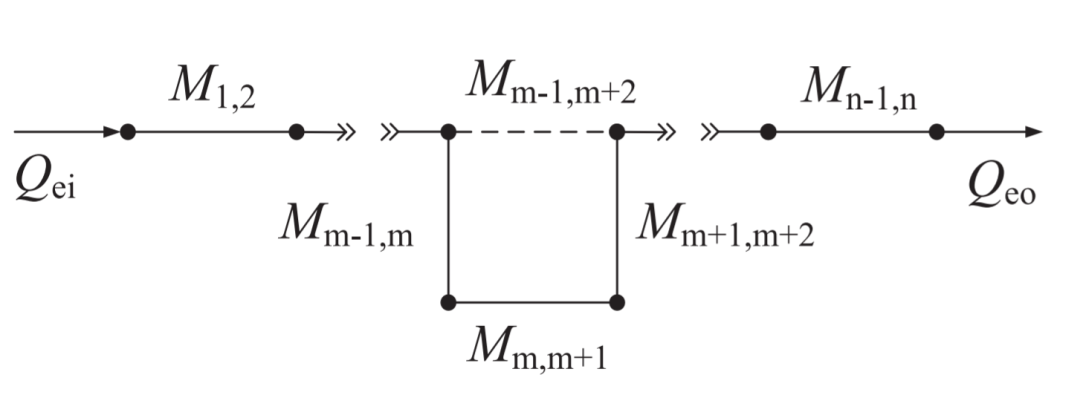

由于篇幅原因以及前期有RFASK相關專欄作者分享過耦合矩陣的Matlab實現代碼(基本上大家可以從代碼中看到其數學推導過程),因此對于由低通原型到傳輸函數,再到導納矩陣,再到耦合矩陣,再由相似變換簡化耦合矩陣這個相對復雜的數學過程本文就不再討論了,本文主要拋出常見的實現帶通濾波器耦合矩陣的“CT(Cascaded Triplet)”與“CQ(Cascaded Quadruplet)”拓撲結構,來簡單討論其底層的數學邏輯。

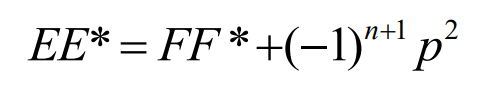

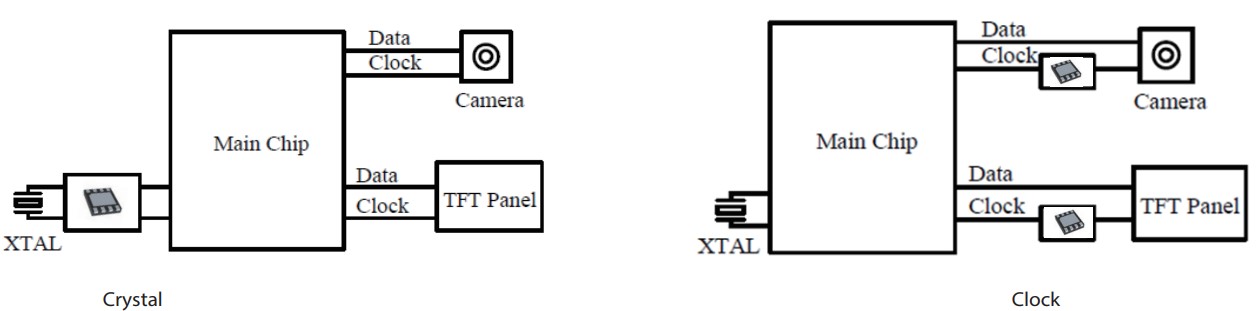

CT,CQ拓撲利用信號傳輸的相位關系,可以獨立地產生一個或兩個傳輸零點,而與其它諧振器無關,這樣有利于設計師們獨立地設計調試各個部件。下圖展示兩款帶通濾波器的CT拓撲結構的單元電路,其中1,2,3分別表示諧振器1,諧振器2與諧振器3,諧振器之間的度數表示不同的耦合方式:

現在大家跟著我一起來做一個簡單的數學題,看看可不可以把這兩個CT結構單元電路的傳輸零點的位置找出來:

(1)先讓大家玩個小游戲,找找看上圖這兩個CT結構有什么不同???

答案揭曉:諧振器1與諧振器3的耦合方式不同,也就是CT拓撲1的源負之間(1,3諧振器之間)的耦合采用的電耦合,CT拓撲2采用的磁耦合。

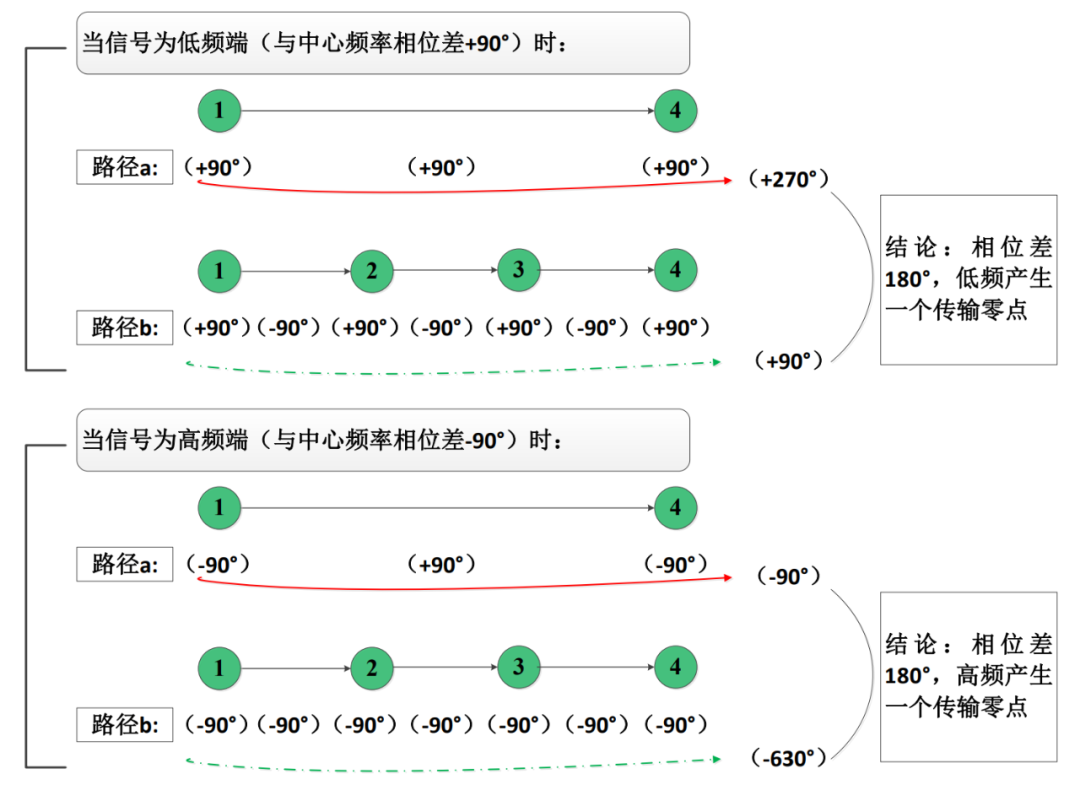

(2)對于CT拓撲1的結構,假定信號從諧振器1出發,經過兩條路徑(a與b)到達諧振器3,同時假設此時的信號在相對于中心頻率的低頻端(咱們自信點,極限一點,就讓此時信號經過諧振器的相位與中心頻率相位差為+90°),那么,請問此時信號能不能傳輸到諧振3???

如上表所示,由于低頻端的信號經過a,b兩路后相位差為180°,即此時低頻端的信號(相對中心頻率相位差為+90°)不能傳輸過去,因此在低頻端(與中心頻率相位差+90°處)產生了一個傳輸零點,如下圖所示:

(3)同樣的道理,CT拓撲2的高頻端信號(與中心頻率相位差-90°),由1→A→3與1→B→3兩條路徑也不能由諧振器1傳輸到諧振器3,因此CT拓撲2的耦合矩陣得到的濾波器能夠在高頻端獲得一個傳輸零點,如下圖所示:

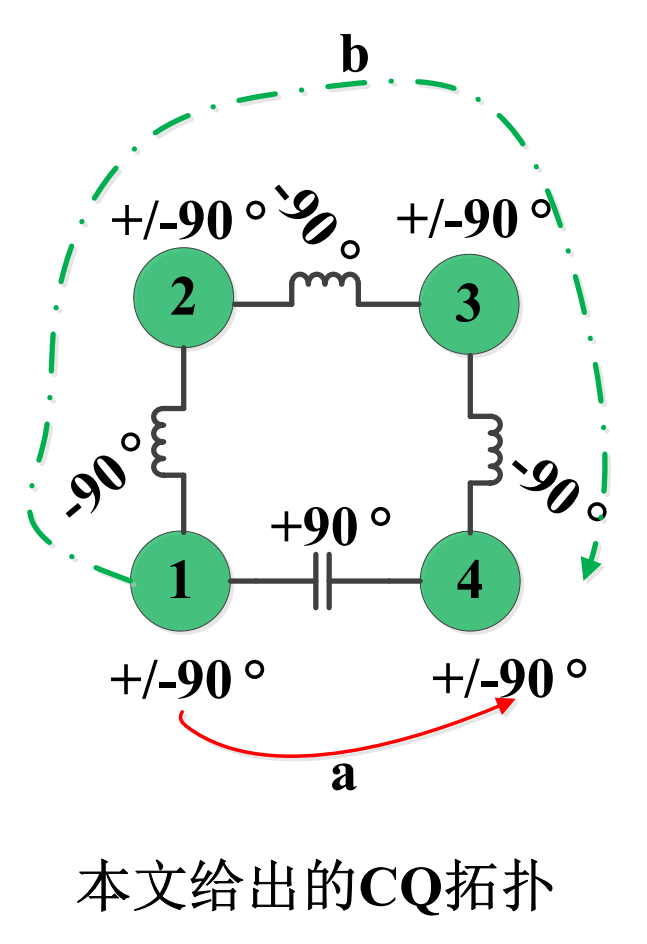

對于引入了兩個傳輸零點的CQ結構,也可以按照此類方法分析。由于CQ結構的組合較多,本文先給出如下圖所示的一個CQ拓撲結構的傳輸相位關系的數學推導(其余的CQ拓撲的數學推導,大家可以自行下來算算哦):

針對上圖所示簡化版的CQ模型中有如下結論:想要利用CQ拓撲在中心頻段上下兩個邊帶分別獲得一個零點,滿足“諧振器同步調諧,耦合邊兩同兩異”即可。這里讀者朋友可能就要問了,老師你發明的啥子詞語哦,啥叫“諧振器同步調諧,耦合邊兩同兩異”呢??OKay,“諧振器同步調諧”主要就是保證當信號進入輸入端時,瞬間傳輸到輸出端,假定了(這是理論模型,只是假定哦,求不杠)信號在所有諧振器中幾乎沒有什么損耗且相位一樣,而“耦合邊兩同兩異”主要就是保證兩路信號在高/低頻時相位保持180°的相位差,筆者這里用下圖來解釋下:

如上圖,本文的CQ模型中所謂的“耦合邊兩同兩異”即耦合邊Mm-1,m+2與Mm,m+1的耦合方式不同,而耦合邊Mm-1,m與耦合邊Mm+1,m+2的耦合方式相同。

好啦,其實濾波器的理論心法還有很多方向去寫,由于篇幅原因,今天就歇了,如果后面大家感興趣的話,咱們再來聊聊。下面即將進入芯片濾波器設計的主題。

三、芯片濾波器的設計

對于芯片濾波器的設計,是不是主要利用低通原型,查找真值表,然后頻率變換得到想要的集中參數,最后來實現想要的頻率響應呢?其實對也不對,因為芯片濾波器會有比較多的應用場景,不同的場景所采用的方法還是有一點點區別,本文主要目的是讓大家了解芯片濾波器的設計流程,采用一個實際例子給大家展示具體的芯片濾波器過程(本次設計采用ADS2022仿真工具)。

本設計實例主要按照如下內容展開: ①設計約束,講解芯片設計前期考慮;②濾波器原型綜合,利用耦合矩陣得到相應的原型響應曲線;③濾波器原理圖仿真,根據耦合矩陣推導出對應的電感、電容值,并適當調試得到前仿結果;④濾波器電磁(EM)仿真,考慮布局布線對濾波器的影響,仿真得到最終值;⑤版圖繪制與DRC。

——設計約束:

(1)工藝約束,由于本次準備設計的射頻濾波器擬采用無源結構來實現,因此工藝節點對設計本身的約束較小,但之所以沒有采用常用的IPD工藝,是因為便于與某射頻前端系統中的其他模塊集成,因此擬采用某2 μm GaAs HBT工藝;

(2)指標約束,本次設計主要是舉例為主,設計了一款Sub-6GHz的濾波器,具體的指標不做過多展開,后續在帶通濾波器的基礎上我會加一個傳輸零點的控制的M外推型電路,便是基于提高帶外抑制度的考慮。讀者需要注意的是,在實際工程中的指標約束可以是系統其他模塊電路根據相應需求提出的,也可以是系統應用背景要求的,濾波器設計師很多時候往往是人在江湖,身不由己,只有玩命擼指標咯,如果實在懟不出來再去和PM argue吧。

(3)尺寸約束,在片上實現濾波器結構,自然是盡可能地小(芯片每平米的價格可比北上廣的房價貴哦),本設計實例沒有采用上文提到的CQ結構來實現一對傳輸零點的引入,而是采用只有兩個諧振器的源負耦合,來實現有一對傳輸零點的帶通濾波器,正是基于能少用諧振器就是少用的原則來做的。

——濾波器原型綜合:

如上設計約束中提到的,本次采用如下圖所示耦合拓撲結構,在輸入端(S)與輸出端(L)之間插入兩個諧振器(1,2),諧振器之間構建兩路不同的耦合,一路(1→a→2),一路(1→b→2),根據上文中提到的基本分析方法可知,當信號偏離中心頻率的相位差+90°與-90°時,S到L的信號相位之和都差180°,因此可以實現一對位于中心頻點兩側的傳輸零點。

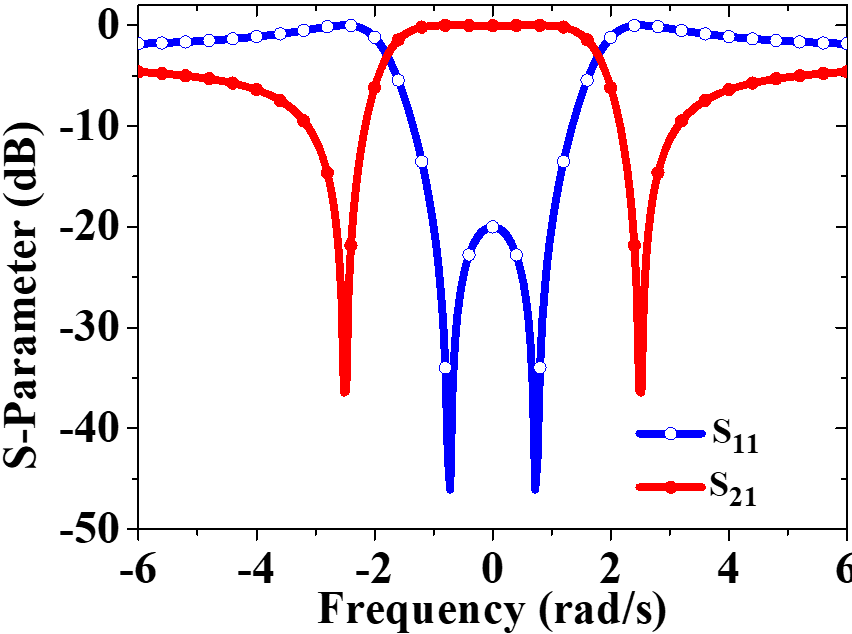

此時根據設計指標,利用耦合矩陣綜合軟件(可以是之前RFASK的博主分享的也可以自己在Matlab里面編寫)建立上圖拓撲,然后得到耦合矩陣以及原型響應曲線如下:

——濾波器原理圖設置以及仿真:

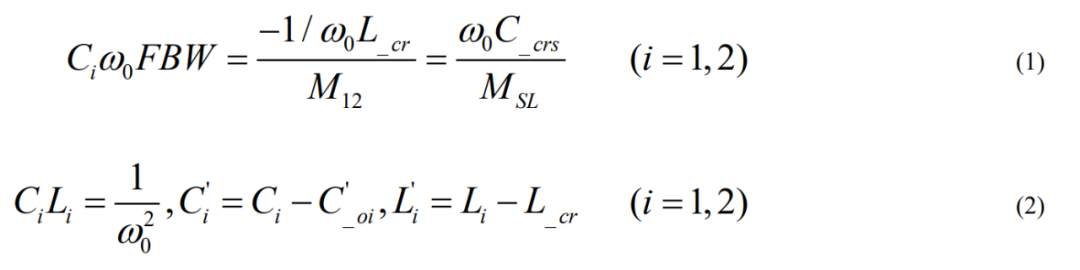

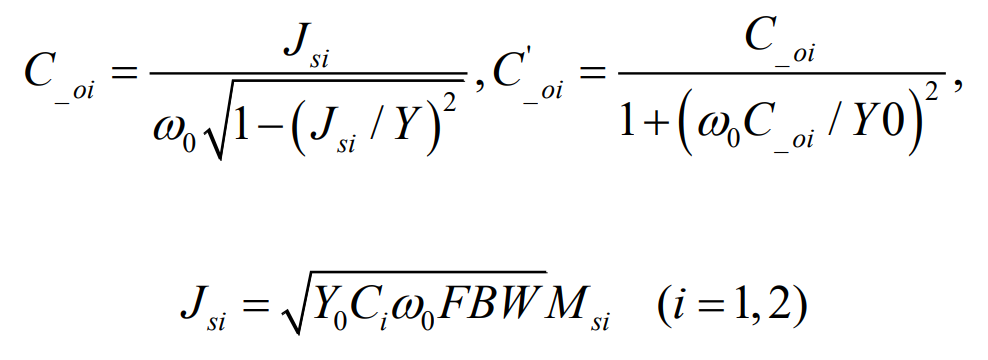

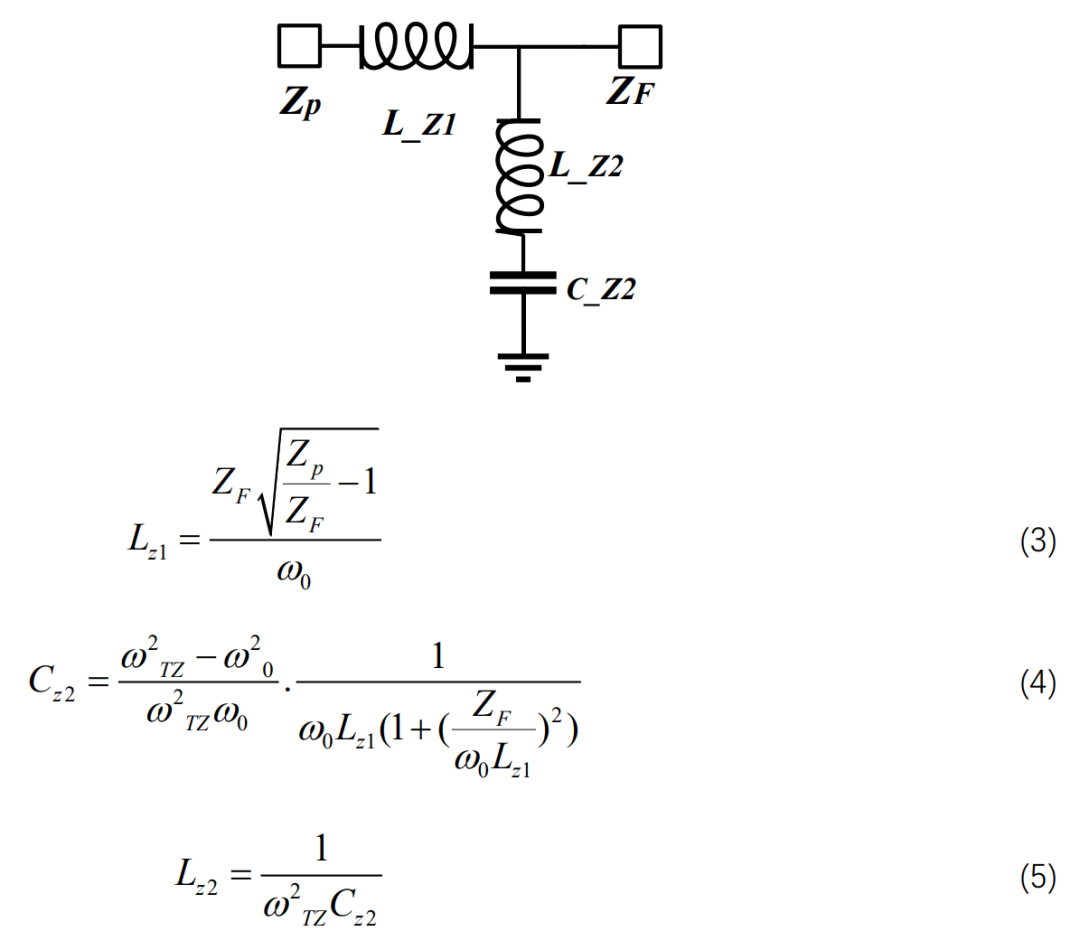

根據綜合得到的耦合矩陣,然后計算得到諧振器以及耦合之路的電感電容值,具體的推導不在贅述,下面給出本文中的理論方法:

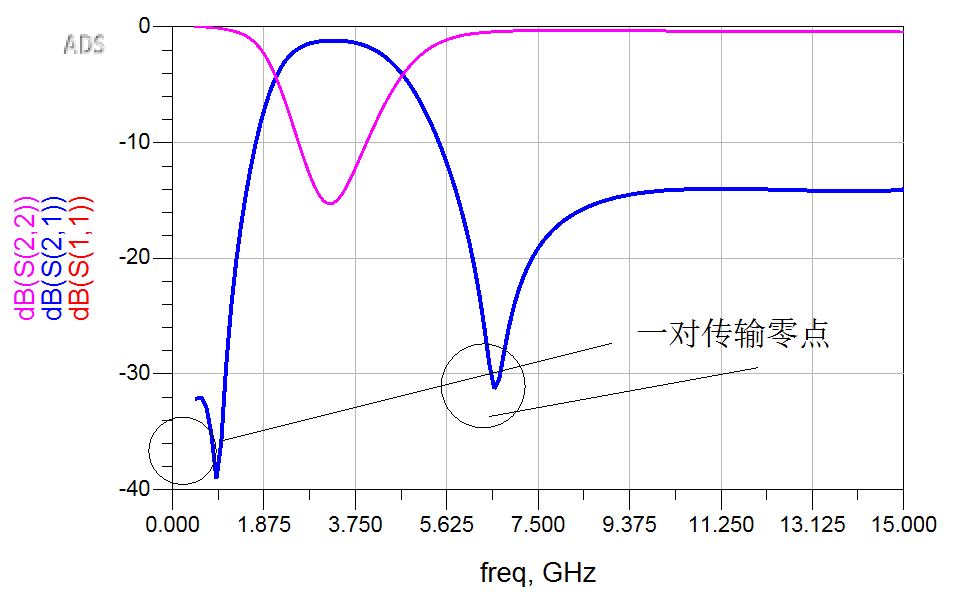

此時

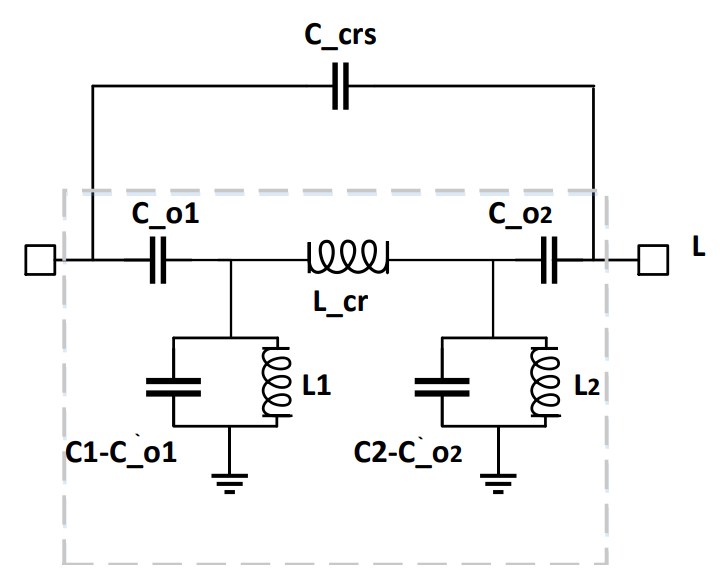

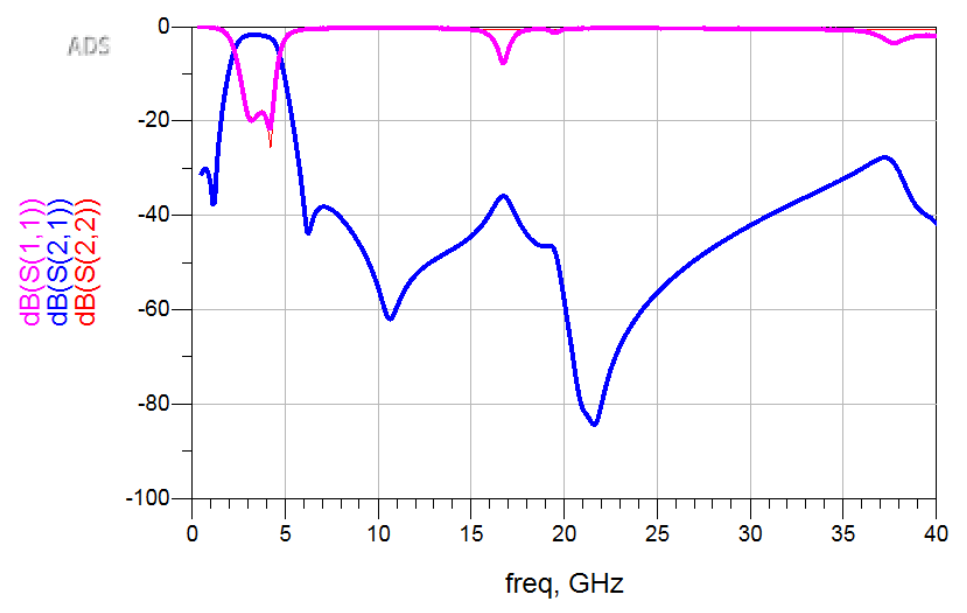

其中Y0為1/50Ω-1,Ci為自定義的歸一化電容值。然后在ADS2022中搭建原理圖仿真得到如下結果:

上圖基本實現了一對傳輸零點的引入,下面再在ADS Momentum中搭建電磁仿真模型。

——濾波器電磁(EM)仿真:

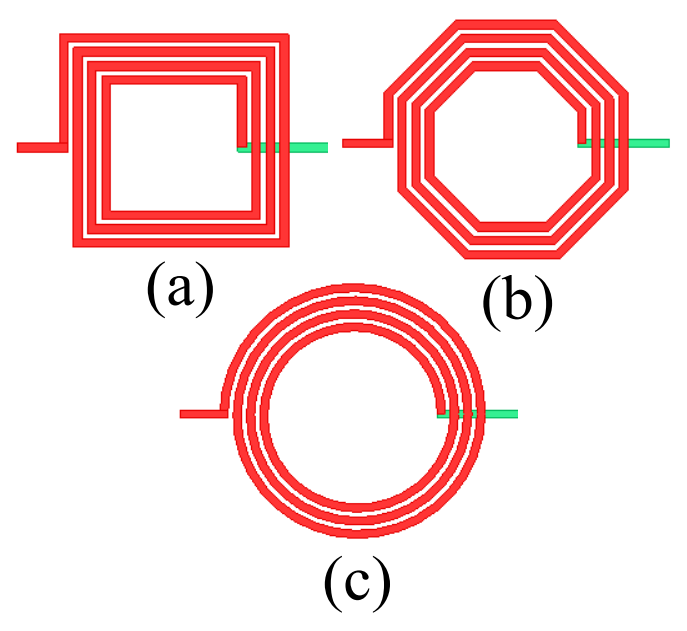

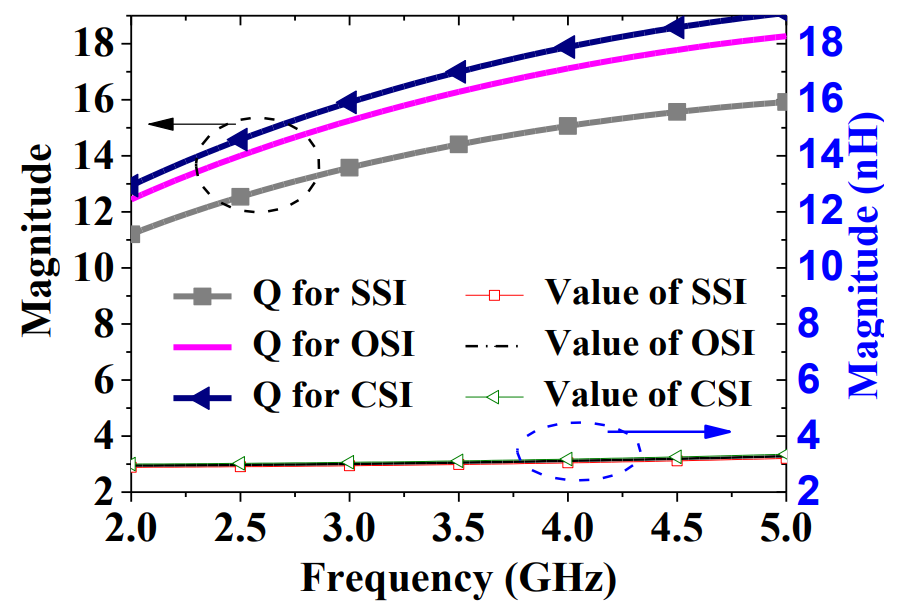

感值、容值及其Q值的提取。在進行電磁仿真時,可以在控制面板中調出廠家提供的電感,電容進行整版仿真,不過一般實際工程中會先對電感,電容值進行提取,以獲得準確的電感/容值和其Q值。如下圖所示,我們對常見的電感進行電磁仿真,提取其感值和Q值,對比方形螺旋電感(Square spiral inductor,SSI)、八邊形螺旋電感(Octagonal spiral inductor,QSI)、圓形螺旋電感(Circular spiral inductor,SSI)分析發現,圓形螺旋的電感Q值相對較高,后續在廠家版圖規則允許的前提下我們選用Q值較高的電感。

對于電容的選擇,讀者可以根據廠家的Guide文件查看其分類,一般在射頻微波頻段用廠家提供的面積小,Q值相對較高的MIM電容較多,如果頻率到了毫米波可能會自行設計電容(如平板電容,交趾電容等),本文就不對電容做特殊分析了。

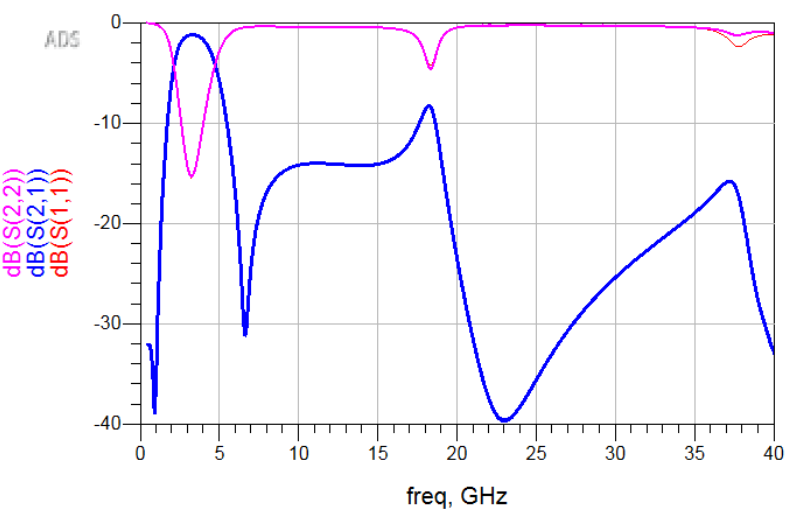

(2)整版仿真。根據提取到的電感電容模型值,在ADS Momentum中搭建如下圖所示版圖,然后再在EM ->Simulation settings里面設置好仿真條件。需要注意的是求解器的選擇,每個導波波長內的網格劃分cells數以及邊沿網格的選擇很多時候會影響到設計的準確度。設置好后仿真得到如下結果:

(3)對仿真結果進行分析,發現問題,解決問題,改進濾波器的性能。

發現問題:針對上述整版電磁仿真結果發現在18GHz處產生了一個寄生通帶,且7GHz~18GHz的帶外抑制度較差;

原因分析:分析其原因主要是諧振器的寄生參數引入的寄生諧振以及在引入交叉耦合(上文中提到的1→b→2路徑)時外加的傳輸線引入了寄生諧振頻率。

解決方案:其實在傳統的PCB濾波器也會有寄生通帶,微帶濾波器的處理方法較多,比如諧振器之間采用不同形狀(每個諧振器的寄生通帶不一樣,級聯后可以整體消除寄生通帶)、諧振器采用如SIR(階躍阻抗諧振器)等具有通帶抑制的結構,但是在芯片內部相對集總參數的諧振器處理相對較難,因此本文采用了一種零點引入技術,在10 GHz引入傳輸零點,加大對寄生通帶的抑制。具體而言,采用引入傳輸零點的Pi型電路,如下圖所示

其中,fTZ = 10 GHz, f0 = 3 GHz, ZF = 50 Ω and ZP = 82 Ω(Zp是對上文版圖的輸出端口阻抗提取得到的值)那么可以推導出對芯片進行重新繪制電磁仿真模型,得到如下仿真結果

——版圖繪制與DRC:

與硅基射頻電路的版圖相比,III-V族化合物電路設計完后的版圖一般不需要做金屬密度填充,對晶體管外的襯底的處理相對較少。因此本文的版圖設計要點主要有:對外Pad應該滿足封裝要求,如果是內部集成到系統應該滿足其他模塊的設計要求;金屬走線,器件放置等應該滿足廠家的DRC( design rule check);最終版圖導出后,如果要與系統其他模塊集成,盡量將其打散(先選中版圖,然后按照下圖操作),以免將模塊給沖掉。

后記:濾波器的理論要求相對較高,本文涉及不及萬分之一,僅僅展示了一種相對容易的數學方法結合仿真軟件來實現芯片濾波器的設計,前前后后碼字到眼花,倉促之間難免有紕漏,希望各位兄弟姐妹能積極討論修正哦。

審核編輯:湯梓紅

-

芯片

+關注

關注

453文章

50387瀏覽量

421785 -

濾波器

+關注

關注

160文章

7727瀏覽量

177670 -

波形

+關注

關注

3文章

377瀏覽量

31506 -

GaN

+關注

關注

19文章

1918瀏覽量

72977 -

帶通濾波器

+關注

關注

18文章

228瀏覽量

43088

原文標題:重磅!芯片濾波器設計實戰指南

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

電源濾波器的作用與選擇指南?

芯片濾波器設計實戰指南

芯片濾波器設計實戰指南

評論