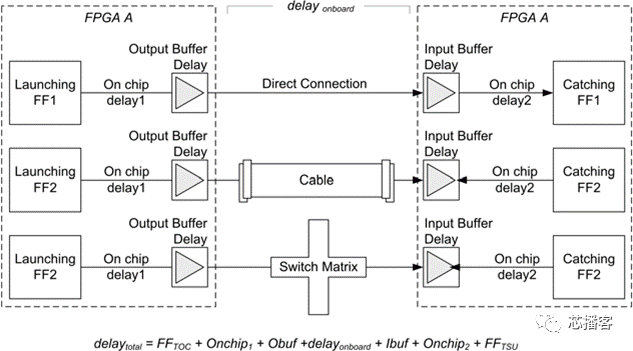

FPGA與FPGA之間互連對信號延遲的影響,兩片F(xiàn)PGA的IO之間每一個額外的過渡,例如連接器、焊點甚至板內(nèi)通孔,都會增加一些阻抗,從而降低信號質量,并增加信號之間串擾的概率。然而,經(jīng)過仔細分析,發(fā)現(xiàn)這并不是一個想象中的大問題。主要矛盾是FPGA互連線的影響。比如,我們可以以如下圖所示的三種連接模型方式表示:

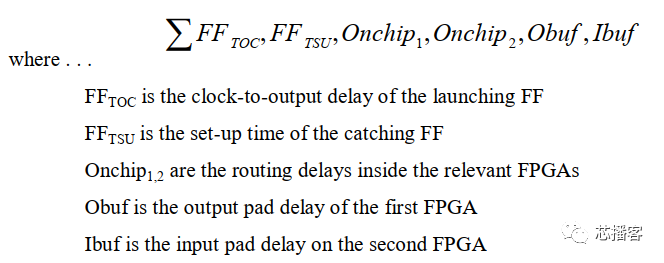

路徑延遲由上圖所示的表達式給出。每個互連方法的共同點是延遲分量,它是所有片內(nèi)延遲和片內(nèi)/片外延遲的總和,每個變量的意義如下表示為:

三種連接方式,除了Delay onborad這個時間不盡相同,其他時間是一樣的,都是板間的各種連線以及器件的延遲之和,所以決定性因素還在于Delay onbaord時間,Direct Connection是最快的,Cable線互連和Switch連接方式的延遲會更長一些。當然,取決于FPGA原型驗證供應商的PCB能力如何。因為Cable線的延遲大家基本都會選擇專業(yè)的做線纜的公司提供的線纜。這么看來,站在不同的角度來看,這個速率的影響因素就各不相同了,如果你是FPGA供應商,那么提升自身PCB設計能力是基礎,選擇Cable是另一個方面。如果你是SoC供應商,那么,不同廠商的不同連接方式都需要考慮。

除了以上因素,還有其他RTL設計相關相關因素:

1. SoC設計中RTL的風格以及如何有效地將其映射到FPGA中

2. 設計中互連的復雜性,尤其是總線

3. 使用沒有FPGA等效的IP塊

4. 每個FPGA的資源利用率(50%左右是合理的)

5. FPGA之間互連的信號復用比(TDM比)

6. 將快速IO數(shù)據(jù)導入FPGA核心的速度

在典型的設計中,F(xiàn)PGA交換互連的IO之間信號的傳播延遲時間不太容易預測,因為為了路由整個設計,一些信號必須通過多個轉換元件。平均來說,有兩次轉換的遍歷,但在非常大的設計的極端情況下,這可能高達八次,可能該設計被劃分為多達20個FPGA設備。為了確保關鍵路徑穿過盡可能少的轉換電路,F(xiàn)PGA原型驗證系統(tǒng)供應商必須開發(fā)并支持布線優(yōu)化工具。此外,如果此布線任務可以在相關工程師的控制下進行,則工具的選項將變得非常廣泛。這種并發(fā)分區(qū)和布線工具將在基于交換互連的系統(tǒng)上提供最佳結果,因此我們再次看到了為板提供復雜支持工具的好處。

PCB電路板設計和布局的質量也是關鍵

整個FPGA原型驗證工作中,讓設計以非常高的速度運行是一項重要的任務,因為要最接近真實的模擬未來芯片的工作場景。因此必須能夠依靠FPGA的硬件電路板每次都能達到最高速率規(guī)格。如果FPGA原型驗證供應商交付的產(chǎn)品在硬件性能上有明顯差異或批次之間或同一批次中的電路板之間存在延遲,則表明硬件電路板設計質量不高。

例如,對于以100MHz以上的速度運行的接口(如PCIe或DDR3等接口的本地操作所需),該接口必須在其FPGA上具有快速引腳以及PCB本身的穩(wěn)健設計和布局。要做到這一點,特別是使用最新的高引腳數(shù)FPGA,需要具有非常多層的復雜電路板設計。例如,很少有電路板供應商能夠設計和建造40層電路板。本身必須做到長度和阻抗匹配,以允許遠程同步點之間的差分信號和延遲匹配。當在多個FPGA之間劃分任何給定設計時,這將允許更大的自由度。

對高質量可再現(xiàn)板性能的需求尤其適用于時鐘和重置網(wǎng)絡,其不僅必須足夠靈活以允許各種時鐘源和速率,而且還必須在分布式時鐘網(wǎng)絡的每個點提供良好的時鐘信號。

電源也是設計的關鍵部分,初級FPGA核心和IO電壓軌引腳的低阻抗、高電流路徑是特別是在每個時鐘周期在FPGA之間切換許多信號的設計上。

第一次檢查時,使用相同F(xiàn)PGA的兩個電路板似乎提供了大致相同的速度和質量,但利用原始FPGA性能以及可靠的硬件電路板。例如,甚至必須監(jiān)測和控制設備溫度,以保持可靠性并在電路板允許的范圍內(nèi)實現(xiàn)可能的最高性能。

信號復用的支持

時分復用(TDM)的概念及其在FPGA之間增加有效IO的能力是很好理解的,不難看出兩個或多個信號如何在FPGA引腳之間共享相同的互連路徑。TDM方法需要FPGA內(nèi)部的多路復用器和解多路復用器邏輯,并且需要一種保持兩端同步的方法。還需要以比FPGA內(nèi)部邏輯更高的速率運行TDM路徑,并確保到達多路復用器或離開多路復用器的信號都滿足必要的時序約束。這將是一項手動執(zhí)行的復雜任務,因此會開發(fā)EDA工具,可以自動插入TDM邏輯,分析時序,甚至選擇用哪些信號填充多路復用器。

無論使用哪種工具,問題仍然存在,即使用多路復用,基于FPGA的原型必須以較低的速度運行,或者板載路徑必須能夠以較高的速度運行。TDM比為8:1或更高的情況并不罕見,在這種情況下,F(xiàn)PGA內(nèi)部以16MHz運行的設計必須縮小到2MHz,或者外部信號必須以128MHz或更高頻率在FPGA之間傳播,或者在這兩個極端之間進行某種妥協(xié)。由于某些基于FPGA的原型需要高復用率,TDM路徑的運行速度可能會限制總體性能。因此,板之間的良好區(qū)別在于它們能夠以高速和良好的可靠性運行外部信號;有噪聲的板將可能在TDM流中引入毛刺,并擾亂其兩端之間的同步。

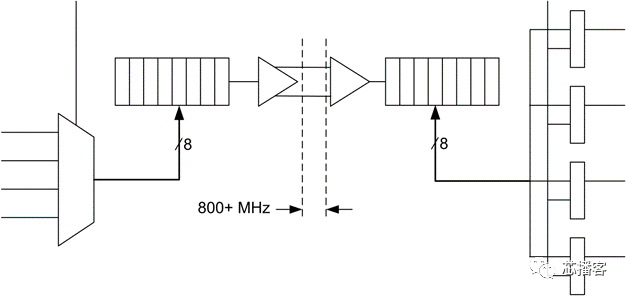

除了簡單的TDM之外,還可以使用現(xiàn)代FPGA引腳的LVDS(低壓差分信號)功能,以便以高達1GHz的速度運行板載路徑。這種全速要求FPGA之間具有非常好的板級傳播特性。下圖給出了一個串行TDM配置的非詳細示例,該配置允許八個信號通過一對差分信號進行傳輸。

在800MHz的高傳輸速度和8:1的復用率下,前面說的128MHz速度可以很容易地得到支持,甚至可以提高到64:1的比率,只要電路板足夠好。運行高得多的多路復用器比率的可能性大大提高了FPGA之間的可用連接性。例如,TDM比為64:2(2而不是1,因為需要差分管腳)可以在運行于30MHz或更高的速率。

因此,F(xiàn)PGA板之間的一個很好的區(qū)別是,它們能夠支持高質量的LVDS信號以實現(xiàn)更高的整體性能,并為FPGA提供必要的電壓和IO電源以支持LVDS。同樣重要的是,設計者以及他們用于劃分的工具必須了解哪些板跡線的長度將匹配,并且能夠承載高質量的差分信號。一個好的電路板將提供盡可能多的此類對,并將提供工具或實用程序支持,以將這些對分配給最合適的信號。

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601846 -

lvds

+關注

關注

2文章

1036瀏覽量

65705 -

TDM

+關注

關注

0文章

57瀏覽量

15609

原文標題:【芯知識】FPGA原型平臺速度的影響因素

文章出處:【微信號:于博士Jacky,微信公眾號:于博士Jacky】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

什么是FPGA原型驗證?如何用FPGA對ASIC進行原型驗證?

FPGA原型平臺速度的影響因素

FPGA原型平臺速度的影響因素

評論