在本文中,將談論抖動合成器與清除器的不同系統參考信號(SYSREF)模式,以及如何用它們來最大限度地提高JESD204B時鐘方案的性能。

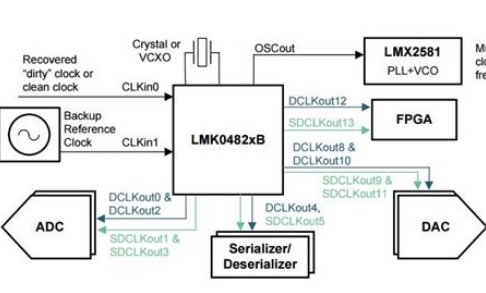

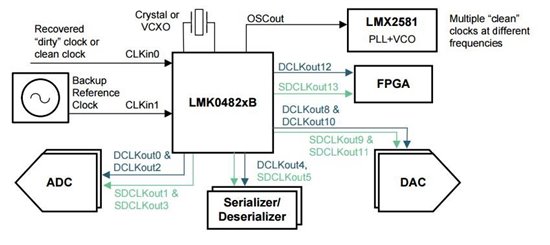

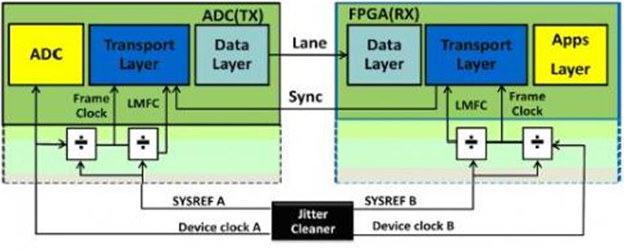

LMK04821系列器件為該話題提供了很好的范例研究素材,因為它們是高性能的雙環路抖動清除器,可在具有器件和SYSREF時鐘的子類1時鐘方案里驅動多達七個JESD204B轉換器或邏輯器件。圖1是典型JESD204B系統(以LMK04821系列器件作為時鐘解決方案)的高級方框圖。

圖1:典型的JEDEC JESD204B應用方框圖

LMK04821憑借來自第二鎖相環(PLL)電壓控制振蕩器的單個SYSREF時鐘分頻器來產生SYSREF信號。信號從分頻器被分配到個別的輸出路徑。每個輸出路徑均包含數字和模擬延遲,以調節與器件時鐘有關的SYSREF相位。

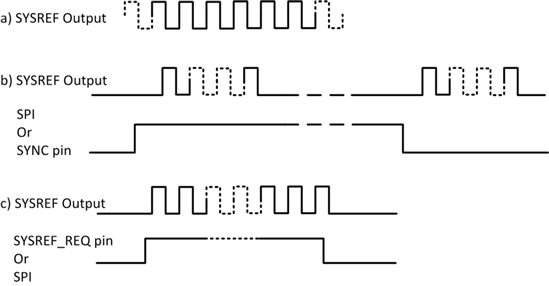

根據JESD204B標準,SYSREF可采用不同的模式,如圖2所示。它可以是連續性(也稱為周期性)、有間隙的周期性或一次性信號。連續性和有間隙的周期性SYSREF的周期必須是本地多幀時鐘(LMFC)的整數倍,以避免多幀中間的SYSREF脈沖。

連續性模式允許連續性輸出。由于從SYSREF至器件時鐘存在串擾,因此許多開發人員不用連續性模式。但是,連續性模式使系統開發人員能在兩個信號之間手動設置恰當的確定性相位關系。設置后,它可變為有間隙的周期性SYSREF。

在有間隙的周期性或一次性模式中,SYSREF時鐘分頻器的輸出通過脈沖發生器被饋送給輸出路徑。脈沖發生器用門控制SYSREF信號,只讓少數脈沖通過。脈沖數可被設定為一個、兩個、四個或八個。因為沒有周期性信號,所以從SYSREF至器件時鐘的串擾被最大限度地減少。

LMK0482x中另一類有間隙的周期性SYSREF模式是請求模式,只要SYNC/SYSREF_REQ引腳為高電平,該模式就能輸出SYSREF脈沖的連續流。

圖2:LMK0482x的SYSREF模式是:a)連續性SYSREF;b)脈沖式SYSREF(一次性或有間隙的周期性模式);c)SYSREF請求(有間隙的周期性模式)

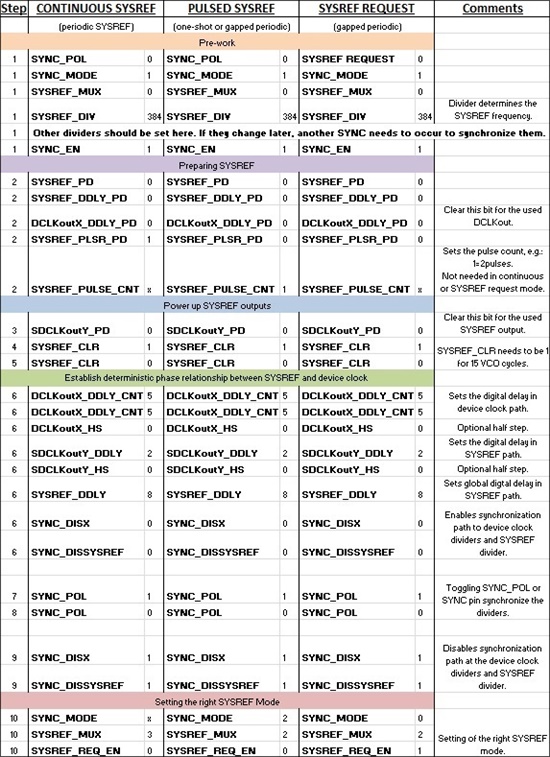

在LMK04821器件中,內部SYSREF分配路徑與輸出分頻器同步路徑共享。因此,它需要一個特定的寄存器寫入序列,以支持同步輸出和無干擾SYSREF脈沖的產生。在表1中,筆者描述的方法都與它們的寄存器寫入序列一起列出。表1還展示了內容為十進制值的內部寄存器字段名。具有相同編號的步驟可以互換。

表1:能啟用不同SYSREF模式的寄存器寫入序列

JESD204B標準是減少布局工作量,同時在信號轉換器和邏輯器件之間采用串行化數據傳輸。通過充分利用JESD204B致能時鐘器件的SYSREF模式,您可在整個系統中輕松創建確定性的相位關系。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

8624瀏覽量

146861 -

寄存器

+關注

關注

31文章

5317瀏覽量

120002 -

脈沖發生器

+關注

關注

5文章

175瀏覽量

34137

發布評論請先 登錄

相關推薦

如何實現JESD204B時鐘方案最大性能

JESD204B的系統級優勢

串行LVDS和JESD204B的對比

JESD204B串行接口時鐘的優勢

jesd204b ip核支持的線速率

如何采用系統參考模式設計JESD204B時鐘

采用系統參考模式設計JESD204B時鐘

JESD204B在時鐘方面的設計及其驗證實現

采用系統參考模式設計JESD 204B時鐘

JESD204B時鐘網絡原理概述

AD9694S: 14-Bit, 500 MSPS, JESD 204B, 二次對數字轉換器數據表 ADI

從JESD204B升級到JESD204C時的系統設計注意事項

采用系統參考模式設計JESD 204B時鐘

采用系統參考模式設計JESD 204B時鐘

評論