雖然只有12年的歷史,但finFET已經(jīng)走到了盡頭。從3nm開始,它們將被環(huán)柵 (GAA)取代,預(yù)計這將對芯片的設(shè)計方式產(chǎn)生重大影響。

如今,GAA主要有兩種類型——納米片和納米線。關(guān)于納米片以及納米片和納米線之間的區(qū)別存在很多混淆。業(yè)界對這些設(shè)備仍然知之甚少,或者某些問題的長期影響有多大。與任何新設(shè)備一樣,第一代是一種學(xué)習(xí)工具,隨著時間的推移會不斷改進(jìn)。

我們?yōu)槭裁匆M(jìn)行此更改?imec 研發(fā)副總裁 Julien Ryckaert 表示:“如果 finFET 間距可以繼續(xù)縮小,人們就會繼續(xù)使用 finFET。” “問題是 finFET 不能簡單地擴(kuò)展,因為你需要在兩個鰭之間插入柵極、功函數(shù)堆棧。根據(jù)這些設(shè)備構(gòu)造的性質(zhì),您不得不將兩個鰭片分開 15 到 20 納米。所以你有這個懸崖。由于這種量化,如果你繼續(xù)將標(biāo)準(zhǔn)單元縮放 1 納米,你的活動區(qū)域就會減少 1 納米,這會導(dǎo)致整個Fin消失。

那一刻人們說,我們需要找到解決方案。

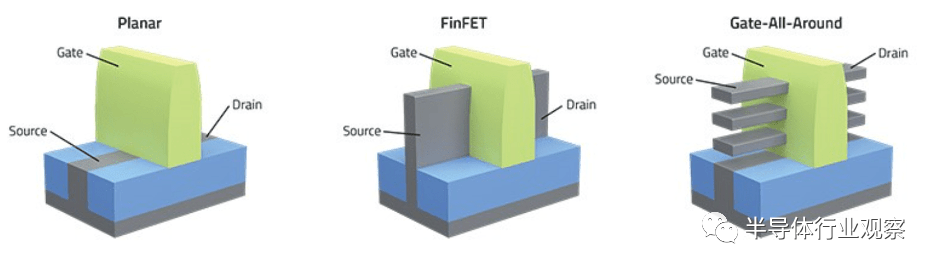

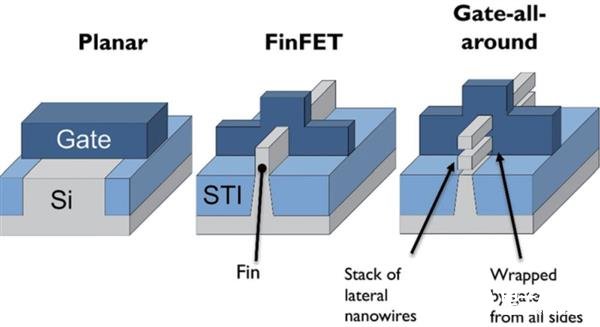

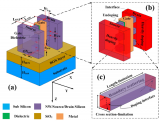

圖1:平面晶體管與 finFET與gate-all-around

環(huán)柵 (GAA) 類似于 finFET。“FinFET 將平面晶體管翻轉(zhuǎn)過來(見圖 1),這樣鰭片(Fin)高度就變成了等效平面晶體管的寬度,”Atomera 的首席技術(shù)官 Robert Mears 說。“由于加工限制固定了鰭片高度,晶體管寬度只能通過使用額外的鰭片以離散量變化。GAA 返回到平面幾何形狀,但現(xiàn)在具有垂直堆疊的平面納米片。因此,原則上,寬度可以連續(xù)變化。”

那不太可能發(fā)生。“因為它是平面結(jié)構(gòu),所以在調(diào)整有效寬度方面會有更大的靈活性,理論上你可以連續(xù)改變板材( sheet)寬度,”imec 的 Ryckaert 說。“但是,代工廠很可能會限制設(shè)計人員使用任意納米片寬度的能力,并且他們會強(qiáng)制限制。”

這很可能是因為創(chuàng)建模型需要時間和難度。“每個設(shè)備尺寸都必須單獨(dú)表征、鑒定和建模,這增加了開發(fā) PDK 的成本,”Atomera 的 Mears 說。“在庫級別,我們可以期待更好地優(yōu)化邏輯和 SRAM,使用寬度作為附加變量來優(yōu)化功率性能權(quán)衡。”

可變性推動GAA

但轉(zhuǎn)向GAA的最大問題是可變性,這是產(chǎn)量和性能的關(guān)鍵因素。

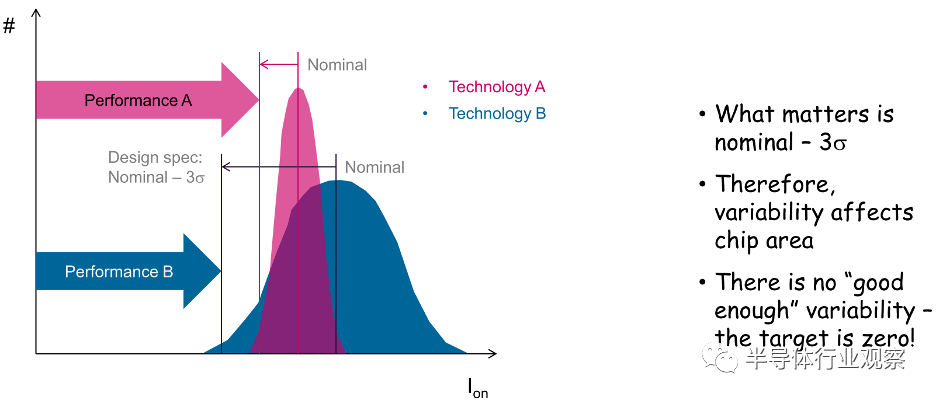

Synopsys TCAD 產(chǎn)品組研究員 Victor Moroz 說:“假設(shè)你有技術(shù) A(見圖 2),其中晶體管強(qiáng)度有一定分布,這是通過晶體管的驅(qū)動電流來衡量的”. “有一些名義上的行為和一些分布。芯片上的十億個晶體管不可能是一樣的。有些略有偏差。通常,它類似于高斯分布。對電路設(shè)計人員來說重要的不是標(biāo)稱行為,而是工藝角,類似于標(biāo)稱減去三西格瑪。假設(shè)您有另一種技術(shù) B,它具有更好的標(biāo)稱性能,但具有更大的可變性。如果它相當(dāng)寬,可能是設(shè)計人員被迫設(shè)計到這個工藝角落,然后再好的標(biāo)稱性能也沒用。GAA 技術(shù)是一種控制甚至可能減少可變性的方法。”

圖2:可變性的影響

隨著finFET變小,可變性增加。Ryckaert說:“當(dāng)finFET進(jìn)入一個鰭時,可變性會變得非常成問題。”“有很好的跡象表明,導(dǎo)致變異的機(jī)制可能在納米片中得到更好的控制。finFET的一大問題是鰭片輪廓,它會在鰭片底部引起相當(dāng)大的可變性。對于納米片,因為您是從具有外延生長的預(yù)定義超晶格開始的,所以這些堆疊由原子控制。納米片的厚度被控制到原子,因此你的片材厚度,這是一個非常重要的變化來源,將有更好的控制。”

Nanosheet 與 nanowire

這些術(shù)語幾乎可以互換使用,但它們不是一回事。“納米線是一種通過讓柵極環(huán)繞圓形硅通道來完全控制溝道的想法,”Ryckaert 說。“那是你可以獲得最佳靜電和最佳溝道控制的地方。”

但這是一個權(quán)衡。“雖然納米線確實改善了短溝道控制,但由于其幾何尺寸小,通常為 5nm x 5nm 的數(shù)量級,它會降低驅(qū)動電流,”Mears 說。“納米片結(jié)構(gòu)介于 finFET 和納米線之間。片材的高度同樣約為 5 納米,但寬度要大得多并且可以連續(xù)變化。柵極靜電控制比 finFET 好,但比納米線差,因為雖然納米片的柵極確實包圍了所有四個邊(因此稱為“環(huán)繞柵極”一詞),但其較大的寬度導(dǎo)致邊緣上的柵極控制較少。另一方面,與兩者相比,納米片的驅(qū)動電流有了很大改善。目前的 GAA 結(jié)構(gòu)應(yīng)該被描述為納米片而不是納米線。”

SRAM 推動妥協(xié)。“納米片厚度約為 5 納米,寬度約為 20 或 30 納米,”Synopsys 的 Moroz 說。“這對于邏輯來說是典型的。但對于 SRAM 來說,沒有足夠的空間來設(shè)置寬通道,因此對于 SRAM 來說,通道寬度將是 10 毫米或更小,這幾乎是納米線。”

現(xiàn)在你必須處理后果。“納米線更適合靜電學(xué),但那個圓的周長非常小,”Ryckaert 說。“你需要構(gòu)建整個柵極,以及它周圍的這個大源漏極,這將引入與平板中一樣多的寄生效應(yīng),但驅(qū)動器非常差。對于非常小的電流,您只會產(chǎn)生很多寄生效應(yīng)。僅僅因為幾何形狀,納米片對于 SRAM 來說是一個非常糟糕的主意。鰭的足跡是五納米。納米片強(qiáng)制寬度為 15 納米或 20 納米,所以這只是你消耗的空間,這意味著你的 SRAM 無法與納米片一起縮放。”

SRAM 的可變性也會導(dǎo)致問題。“對于邏輯,電路有一定的深度,”Moroz說。“想象一下你的晶體管沿著那條路徑隨機(jī)變化,但因為你可能有 15 個階段,所以會進(jìn)行一些自我平均。對于 SRAM,您所擁有的只是兩個并排的反相器。總共有兩個 NMOS 和兩個 PMOS 晶體管,如果它們不匹配,那就是問題所在。”

還有其他問題。“摻雜劑的可變性會導(dǎo)致閾值電壓發(fā)生顯著變化,”Mears 補(bǔ)充道。“隨機(jī)摻雜波動 (RDF) 的可變性會導(dǎo)致器件之間的顯著差異——甚至是匹配的器件——這會導(dǎo)致 SRAM 性能和產(chǎn)量降低,并在邏輯器件的時序模型中增加額外的最壞情況保護(hù)帶。”

有多少個sheet?

GAA 制造中的另一個變量是納米片的數(shù)量。“PPAC(功率、性能、面積/成本)限制將推動更多層,特別是隨著納米片繼續(xù)擴(kuò)展,”Mears 說。“例如,假設(shè)其他一切都保持不變,從 3 個納米片層到 4 個納米片層可將性能提高近 33%,但芯片尺寸應(yīng)保持不變,晶圓加工成本應(yīng)該只會小幅增長。GAA 經(jīng)濟(jì)學(xué)依賴于堆疊多個 GAA 片材(sheet)以獲得有效密度,因此增加層數(shù)的壓力肯定會增加。”

但這并不是完全可變的。“很難相信它會被限制在兩個,而且超過五個也將非常困難,”Ryckaert 說。“這歸結(jié)為簡單的數(shù)學(xué)。僅通過計算電容和溝道寬度即可得出 90% 的答案。您還需要計算在特定硅區(qū)域周圍需要封裝的源極-漏極和柵極之間的表面面積。周長對最大化驅(qū)動和最小化電容至關(guān)重要。最大化驅(qū)動和最小化電容只是表面與周長的比率。如果您比較三鰭 finFET 器件,則沒有納米片結(jié)構(gòu)可以擊敗它。但由于 finFET 的量子化特性,單元高度損失一納米意味著一個鰭消失了。納米片為您提供邏輯縮放所需的納米縮放。然后與 finFET 相比,納米片將開始發(fā)光。這種情況發(fā)生在大約三到四張紙上。僅僅因為源極-漏極的電阻和結(jié)構(gòu)的電阻,五張紙就無法工作。您意識到第五層剛好足以驅(qū)動您為使結(jié)構(gòu)更高而添加的寄生效應(yīng)。你只是在自己的結(jié)構(gòu)中消耗電流。”

在芯片內(nèi)改變它也沒有什么意義。“改變同一芯片上的層數(shù)并不容易,”Moroz說。“一旦你決定了某個數(shù)字,它可能會適用于整個芯片。對于高性能計算,最好使用四層。對于移動設(shè)備,最好使用三個。”

性能

對于每個節(jié)點,都希望降低電壓和功率。“壓力始終存在以降低電壓供應(yīng),從而降低功率,但 Vt 受到限制,”Mears 說。“它不能進(jìn)一步降低,因為它是由 Ioff 規(guī)范和有限亞閾值斜率 (SS) 設(shè)定的,由于熱力學(xué) (kT/q),它不能低于每十年 60mV。目前正在研究可進(jìn)一步降低 SS 的新型電路元件,例如來自鐵電柵極電介質(zhì)的“負(fù)電容”,但這些元件不會很快投入量產(chǎn)。另一個對 Vdd 的限制是 SRAM Vmin,它為給定的錯誤率設(shè)置最低可能的電源電壓。由于嵌入式 SRAM 通常是電壓降低時最先出現(xiàn)故障的塊,因此 Vmin 通常設(shè)置最小電源電壓。”

功耗會有一定的提升。Moroz 說:“過去十年以及未來的每一項后續(xù)技術(shù)都會讓您在相同性能的情況下降低 20% 左右的開關(guān)功耗。” “泄漏受可變性的影響,因為對于泄漏而言,更重要的是晶體管泄漏的快速角。因此,具有更嚴(yán)格的可變性有助于實現(xiàn)這一目標(biāo)。”

但是關(guān)于功耗還有未知的方面。“一種熱源是自熱或焦耳熱,” Ansys產(chǎn)品營銷總監(jiān) Marc Swinnen 說。“使用 GAA,這些門中有多個納米片,它們被絕緣體包圍,絕緣體不太好。設(shè)備自熱會有所不同,但我們還沒有足夠的信息來了解它的影響有多大。我們最終將從鑄造廠獲得這些數(shù)字。局部熱源會導(dǎo)致熱尖峰,這會影響對溫度呈指數(shù)級敏感的電遷移。如果局部有幾個晶體管趨于變熱,那么與芯片平均值相比,周圍金屬中的電遷移分布會有所不同。你不能只使用平均值。”

接下來是什么?

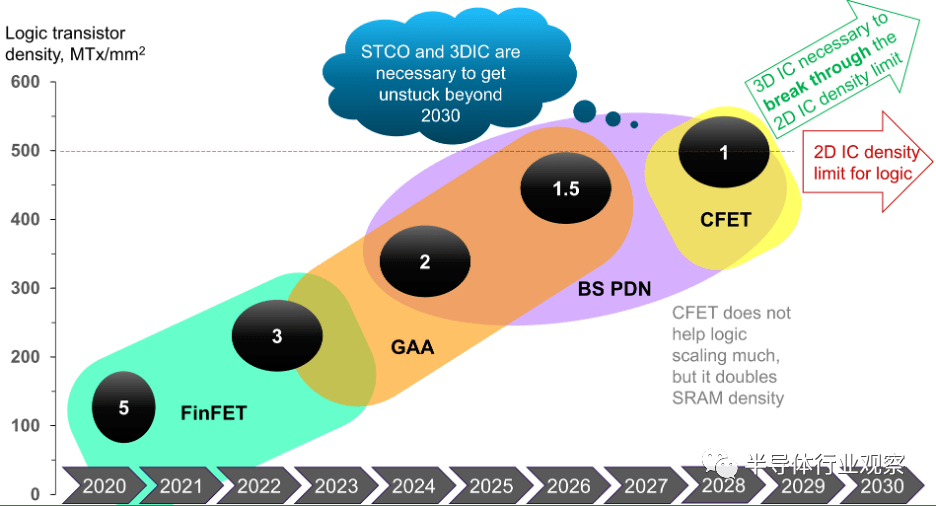

很明顯,隨著設(shè)備的縮小,變化將成為常態(tài)。“我們希望看到納米片至少用于兩個節(jié)點,但在那之后縮放納米片結(jié)構(gòu)將變得非常棘手,”Ryckaert 說。“我們提出了 forksheet,它是對 nanosheet 概念的改編。它具有縮放屬性,可以啟用另外兩個節(jié)點。然后是 CFET(互補(bǔ) FET 堆疊),它的靈感來自納米片,但采用堆疊配置(見圖 3)。”

GAA 的壽命可能與 finFET 相似。“它很可能會存在 10 年,”Moroz說。“但到 2030 年左右,我預(yù)計該行業(yè)將轉(zhuǎn)向堆疊晶體管,其中兩個 GAA 晶體管堆疊在一起。有些人稱之為 CFET、互補(bǔ) FET 或堆疊晶體管。”

圖3.邏輯技術(shù)路線圖

那就是它變得有點困難的時候。“在 CFET 之后,我們完成了二維集成電路,”Moroz補(bǔ)充道。“對于邏輯,我們預(yù)計晶體管密度將停止在每平方毫米約 500 萬個晶體管的密度,而對于 SRAM,這將是每平方毫米 10 億個晶體管。然后我們就卡住了,因為雖然你可以隨心所欲地擠壓晶體管,但一切都會受到連接晶體管的電線的限制。唯一的出路是堆疊小芯片。”

審核編輯:湯梓紅

-

芯片

+關(guān)注

關(guān)注

454文章

50460瀏覽量

421967 -

晶體管

+關(guān)注

關(guān)注

77文章

9641瀏覽量

137876 -

納米

+關(guān)注

關(guān)注

2文章

693瀏覽量

36955 -

FinFET

+關(guān)注

關(guān)注

12文章

247瀏覽量

90155 -

GAA

+關(guān)注

關(guān)注

2文章

36瀏覽量

7437

原文標(biāo)題:芯片工程師,是時候了解GAA晶體管了

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

資深工程師談晶體管使用心得:用晶體管來實現(xiàn)功率負(fù)載的控制

招聘功率器件工程師、應(yīng)用開發(fā)工程師

為什么晶體管使用越久,功耗越低?

芯片里面100多億晶體管是如何實現(xiàn)的

什么是鰭式場效應(yīng)晶體管?鰭式場效應(yīng)晶體管有哪些優(yōu)缺點?

全面了解全棧工程師

Intel放棄FinFET晶體管轉(zhuǎn)向GAA晶體管 GAA工藝性能提升或更明顯

西安交大在GAA晶體管自熱效應(yīng)研究模型取得新成果

芯片工程師,是時候了解GAA晶體管了

芯片工程師,是時候了解GAA晶體管了

評論