原文來自微信公眾號:工程師看海

大家好,我是工程師看海,原創文章歡迎點贊分享!

PCB layout需要豐富的經驗和扎實的理論基礎支持,還要多踩幾個坑,多做幾個仿真加深對走線的理解,才能形成閉環的走線設計,今天介紹一個和GND走線相關的案例,在手機領域會影響相機畫質、在醫療領域會影響生物電信號采集信噪比,如果不理解背后的原理,只會復制原理圖或PCB的話,往往達不到電路的最佳性能。

地線在PCB走線中,通常有三種作用:

回流

控制阻抗

屏蔽

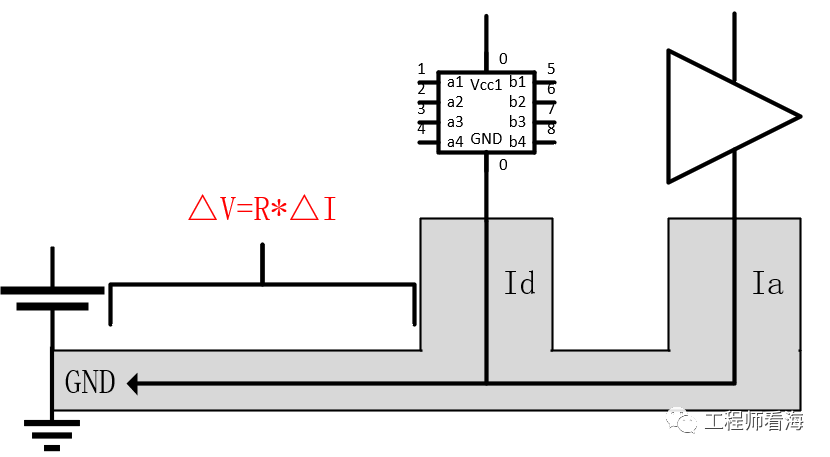

今天介紹的案例是和回流相關(本次討論以低頻為主),地線上的電壓波動會影響到對噪聲敏感的模擬電路。上圖是一種地線走線示意圖,數字電路和模擬電路的GND最終都要匯聚一起和電池的地連接,也就是說數字電流Id和模擬電流Ia最終都要匯集在一起,那么這兩路電流Id和Ia就用公用地線部分,如上圖括號內所示,一般而言數字電流Id的波動是比較大的,而模擬電流Ia的波動略小。數字電Id的波動在共用地線部分會引起電壓波動,這個波動就會被模擬電路感應到,進而引起信號質量下降,比如共用地部分的電阻是20 mΩ,而數字電流Id波動是1A,那么引起的電壓波動△V就是0.02*1=0.02V,這個20mV被模擬電路的放大器感應到將會以噪聲形式出現,這就是地線阻抗大的后果。

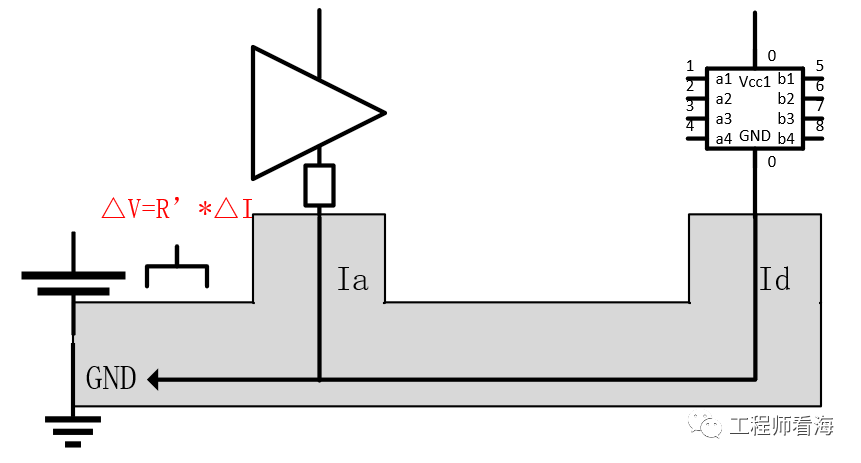

緩解的方法如下:減小地線的電阻,縮短模擬電路和數字電路共用地線,把模擬電路和數字電路通過磁珠隔離進一步壓制干擾,假如數字電路電流波動不變,依然是1A,共用的地的電阻降低到2 mΩ,此時數字電路在共地部分引起的電壓波動只有0.002*1=0.002V,比上面的20mV小了很多,同時,有磁珠的存在還會進一步壓制這個噪聲,提高模擬電路的信噪比或者是共模抑制比。直觀點說就是:不管你數字電路的地/電源怎么跳動,都影響不到我模擬電路的地/電源。

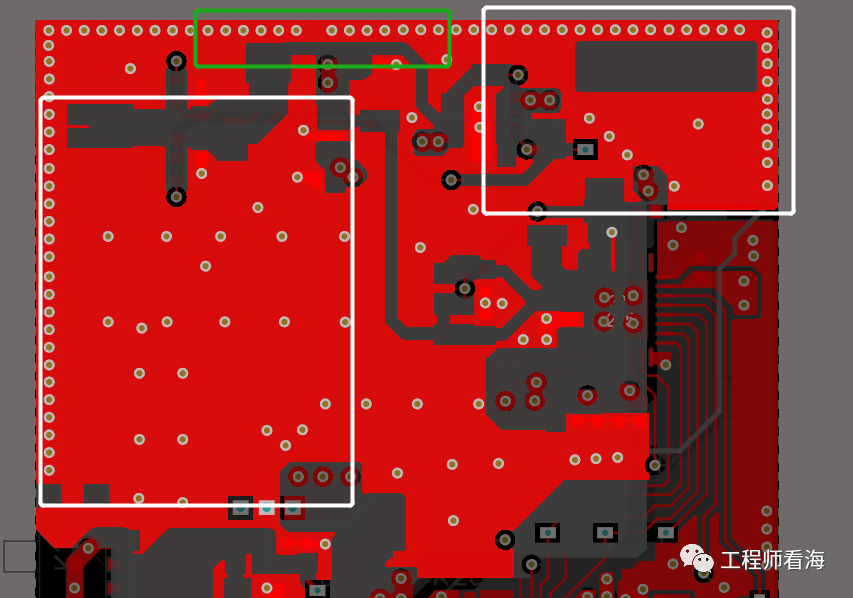

正是基于上面的介紹,所以一般電路板都會進行大面積的鋪銅(大面積鋪地平面,減小阻抗,增加回流能力),減少地的電阻。上面介紹的是地線的處理,對于模擬電路和數字電路共用電源的處理也是類似的方法(不過通常而言,不建議模擬電路和數字電路共用電源)。

所以呢,有的人就不建議在地平面上打大量的其他電氣屬性的孔,或者是走線,這就是通常所說的支離破碎的地,這樣容易增加地線的電阻(或阻抗),甚至是有隱藏的電阻瓶頸存在被工程師忽略而引起嚴重的問題。比如下圖高亮的紅色銅皮,兩塊白色方框內的銅皮看起來很大,其實他們的連接僅僅只有綠色部分窄窄的一條,這里就是阻抗瓶頸。

上面提到的僅僅只是直流電壓波動,對于高頻數字電路而言,電流的波動更復雜,含有非常豐富的電壓或電流諧波,此時就要考慮頻率這個參數了,圍繞頻率這個參數,就要考慮地線的寄生電容或寄生電感等參數,這在高端CPU中就格外重要,PCB走線要求更嚴格,這就是電源的PDN設計,在后面的DCR仿真和PDN仿真會有更詳細的介紹。

如果看到這里,請點贊、收藏、分享三連!

原文來自微信公眾號:工程師看海

限時免費掃碼進群,交流更多行業技術

推薦閱讀▼

電池、電源

硬件文章精選

-

信噪比

+關注

關注

3文章

253瀏覽量

28592 -

地線

+關注

關注

10文章

218瀏覽量

26755 -

數字地

+關注

關注

2文章

49瀏覽量

10713 -

模擬地

+關注

關注

0文章

53瀏覽量

11013 -

PCB

+關注

關注

1文章

1777瀏覽量

13204

發布評論請先 登錄

相關推薦

PCB布線之模擬和數字布線異同

PCB布線設計經驗談-模擬和數字布線的異同

PCB布線設計經驗談-模擬和數字布線的異同

模擬電路和數字電路PCB設計的區別詳解

模擬電路和數字電路PCB設計的區別詳解

PCB模擬和數字布線的異同

模擬電路和數字電路PCB設計的區別

模擬電路VS數字電路,PCB設計有何不同?

數字地、模擬地、信號地、交流地、直流地、屏蔽地、浮地基本概念及PCB地線分割的方法

同樣都是地,數字地與模擬地有什么不同?

模擬地、數字地、主地,你的PCB地線走的對嗎?竟然、、

模擬地、數字地、主地,你的PCB地線走的對嗎?竟然、、

評論