原文來自微信公眾號:工程師看海

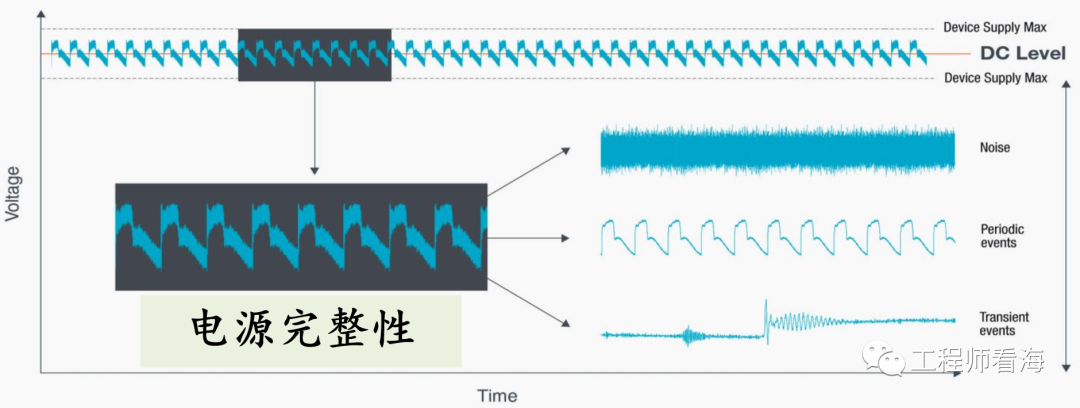

SI(信號完整性)研究的是信號的波形質量,而PI(電源完整性)研究的是電源波形質量, PI研究的對象是PDN(Power Distribution Network,電源分配網絡),它是從更加系統的角度來研究電源問題,消除或緩解電源噪聲,滿足負載對不同頻率電流的需求,為負載提供干凈、穩定、可靠的電源,和SI一樣,PI也是PCB工程師的基本要求之一,拉線拉的好不好,PDN是重要考核方向之一。

前文有詳細介紹信號完整性,本節是介紹電源完整性,二者有什么差異呢?SI的分析基礎是傳輸線,而PI的分析基礎是傳輸平面,SI的常見整改方法有修改走線寬度、長度、參考層,而PI的整改方法有修改電源平面/地平面的走線、優化匹配電容器值、電容數量或安裝方式等。

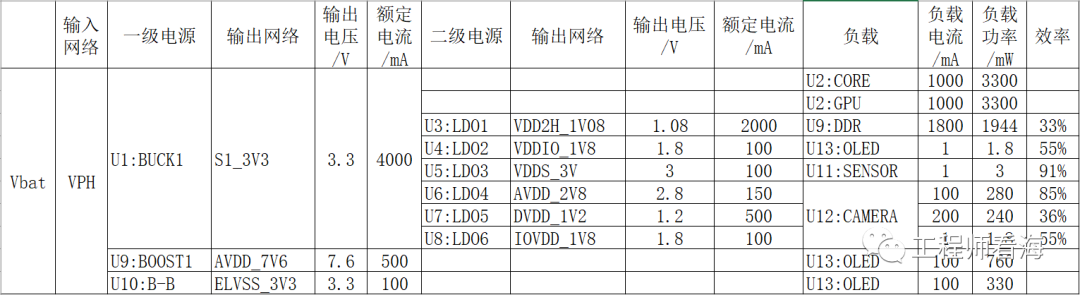

在手機基帶硬件設計中,或者其他電路系統中,PDN應該是最復雜的互聯結構,我也建議新手從電源開始,這里的電源包含兩個方面,第一個方面是電源結構基礎,包括BUCK、LDO等電源架構,以前的文章已經有詳細介紹,通過電源樹(power tree)可以基本了解手機上各模塊的電源需求,以書籍《從器件認知到手機基帶電路設計》的5.3 power path章節中的電源結構為例,整理得到下圖的power tree。

注意:圖中的數據只是示例,具體還是要以實際電路為準,從上面的電源樹中,就可以挖掘出很多信息,比如對功耗敏感的LDO,只有U5和U6效率可以,其他LDO效率都很低,這就需要再優化電源結構,提供電源利用率,還有其他信息可以挖掘,前文已經有介紹,這里不再贅述。

第二個方面便是PDN,PDN可以保證整個系統工作的有效性,避免負載在復雜工作條件下,電壓波動超標,導致系統異常,由此方能完成從電源源端到互聯鏈路最終到負載的完整設計,深刻了解電源后會讓你對手機整體設計有個總的印象,會對整個硬件系統有更加深刻的認識,往后做充電、音頻、屏幕相機、傳感器,要從容的多。

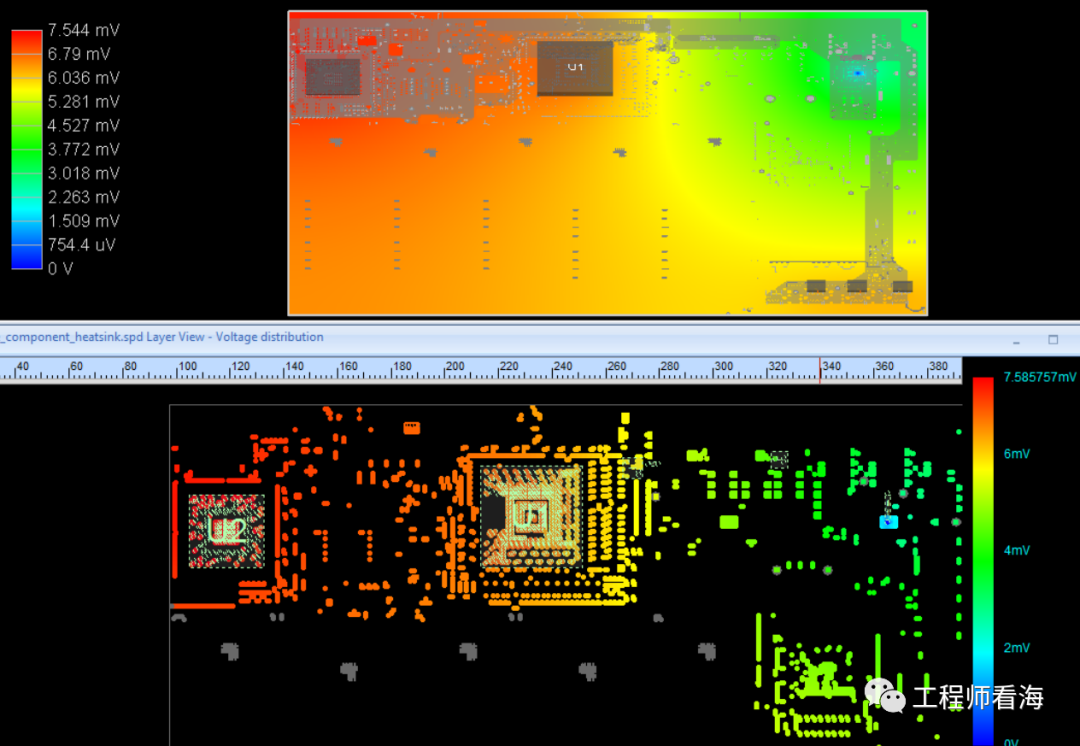

上述兩個方面,前者是電源工程師的重點,后者是電源完整性工程師的重點,相比于電源工程師,PDN更關注電源路徑及終端,PDN鏈路起始于電源模塊VRM(voltage regulator model)包括路上的PCB走線、電容、過孔, package和Die電容等,鏈路紛繁復雜,需要以系統性角度來分析PDN問題,并優化PDN,最終達到為芯片提供穩定干凈的電源的目的。

我們在設計PDN時,關注直流和交流兩部分。

直流部分即△V=△I*R,從VRM到IC是有串聯電阻存在的,通過直流電時就會產生壓降,比如1A的電流通從VRM到達負載,線路電阻是10mΩ的的話,就會產生1*0.01=0.01V的壓降,這個壓降就是常說的IR drop,負載電流不是一個固定值,是不斷在變化的,因此IR drop也是一個變化值,比如當負載在2A工作時,那么2*0.01=0.02V,就會產生0.02V的壓降,這和前文中介紹LDO的走線情況很像。

但是負載不會穩定的工作在一個電流值,比如玩游戲時,CPU會進行各種復雜的運算,GPU會進行復雜的渲染,這些芯片內部的開關都在高速工作,使得其從電源抽取的電流變的很復雜,分析這復雜的時變電流,就不能用電阻了,就需要引入和時間和頻率相關的參數,即阻抗Z(阻抗=電阻+容抗+感抗),電壓的波動是由電流的波動引起的。

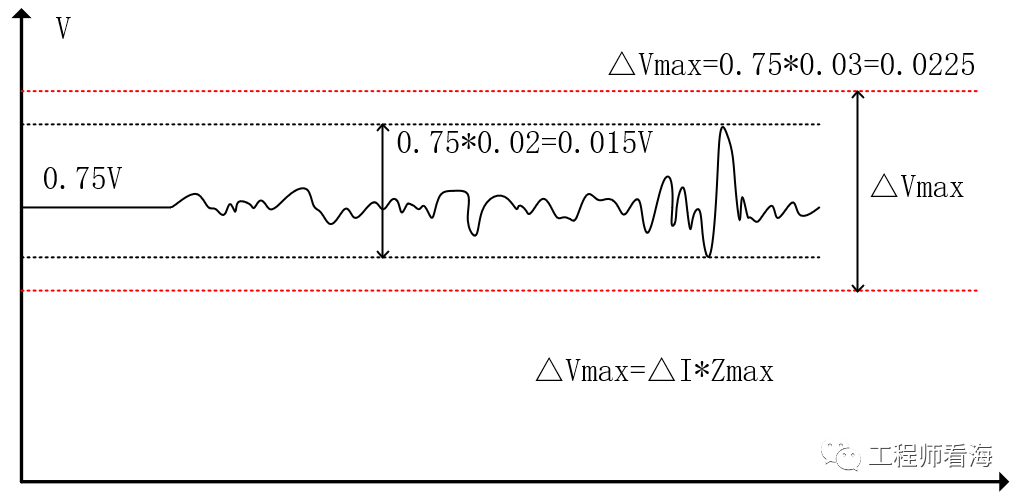

我們再回到經典的計算公式△V=△I*R,現在稍微改變一下,那么就變成了△V=△I*Z,R是常數與頻率無關,而Z就與頻率有關了,△V是電流改變時引起的電壓變化量,如果△V太大了,超出了負載允許的電壓波動,那就是危險的事情了,通常負載能容忍的電壓波動是典型值的5%或3%(具體以實際負載的手冊為準),因此電壓波動就避免超過這5%或3%。比如下圖中,負載需要0.75V的電壓,假設負載最大能容忍3%的電壓波動,即最大能接受0.75*0.03=0.0225V的電壓波動,而實際電壓波動僅有0.015V,這就滿足負載的需求。

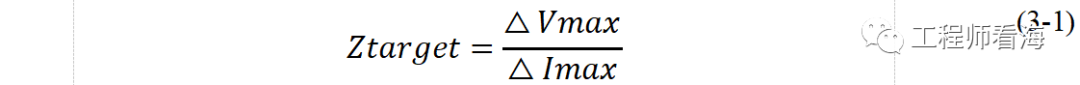

我們再來看公式△V=△I*Z,簡單變形得到下面公式

那么只要我們實際電路的PDN阻抗Z足夠小,Z小到一定程度后,電流波動引起的電壓波動(△I*Z)就會小于△Vmax,那么此時的阻抗就是目標阻抗Ztarget,所以我們設計PDN的原理就是通過優化鏈路上的阻抗Z,使它低于目標阻抗Ztarget,這樣就保證電壓可以滿足負載的需求了,簡言之,就是通過約束阻抗來約束電源波動,我需要知道目標阻抗,并且要知道線路電容上那些電容的具體型號,而且還需要精準的仿真,才能得到可靠的設計。

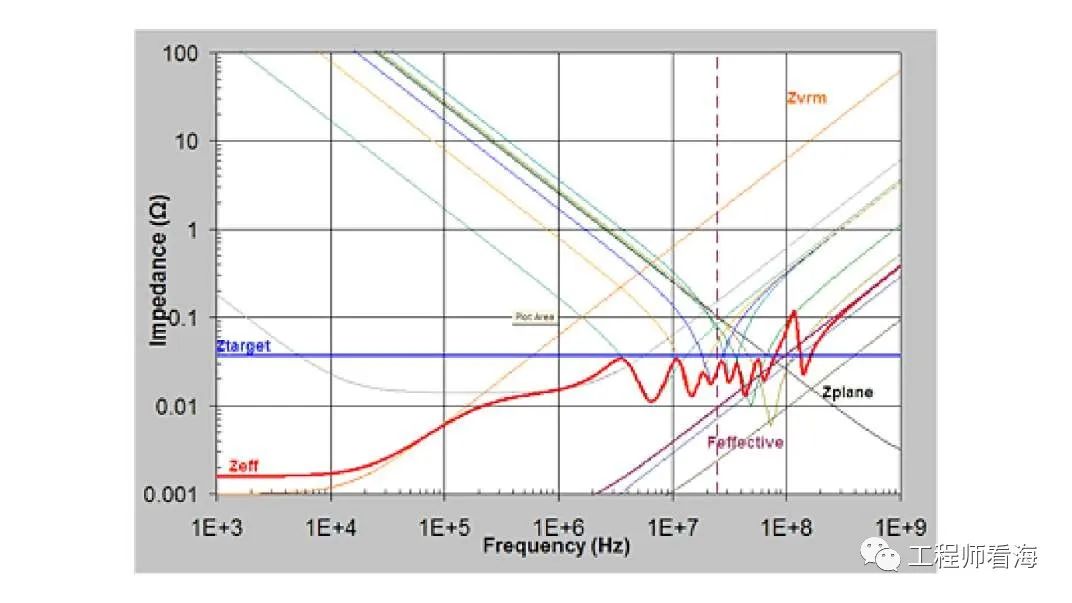

比如上圖就是阻抗頻率曲線,如果負載工作頻率單一,只以一個固定的頻率工作,假設工作電流是一個單一頻率的正弦電流,那么阻抗優化就變的簡單了,只要這個頻率的阻抗低于目標阻抗就行,但是實際情況很復雜,我們不知道復雜的具體工作頻率,所以為了保險起見,我們控制的是一定頻段內的阻抗,而不是直流或單一頻率的阻抗,這看起來是一種過設計,但是確實非常安全的設計。藍色曲線就是我們的目標阻抗,我們要做的就是優化這一頻段內PDN阻抗(Feffective頻率內),使得實際紅色阻抗在負載要求的頻帶內低于目標藍色阻抗。

PDN的基本概念和原理就先介紹到這里,下一節介紹相關PDN優化策略,用于指導實際PCB布局布線和電容器件的選型優化。

如果看到這里,請點贊、收藏、分享三連!

原文來自微信公眾號:工程師看海

限時免費掃碼進群,交流更多行業技術

推薦閱讀▼

電池、電源

硬件文章精選

-

信號

+關注

關注

11文章

2780瀏覽量

76629 -

走線

+關注

關注

3文章

113瀏覽量

23860 -

電源完整性

+關注

關注

8文章

209瀏覽量

20708 -

PDN

+關注

關注

0文章

83瀏覽量

22685 -

PCB

+關注

關注

1文章

1777瀏覽量

13204

發布評論請先 登錄

相關推薦

信號完整性 & 電源完整性 誰更重要呢?

【送書福利】不懂PDN談何電源完整性?請收下這本PDN設計指導硬核書

什么是電源和信號完整性?

介紹一種電源完整性的分析方法

如何使用您的PCB走線寬度來改善信號完整性

PCB PDN design guidelines (PCB電源完整性設計指導) ------PCB疊放準則

PCB PDN design guidelines (PCB電源完整性設計指導) ------PCB布局指南

2000字原創總結,PCB走線基礎(一):電源完整性與PDN設計

PCB走線的電源完整性和PDN設計

PCB走線基礎(一):電源完整性與PDN設計

PCB走線基礎(一):電源完整性與PDN設計

評論