在研究生階段曾流過很多次片,感覺后端設計中最關(guān)鍵的就是后端Flow了,尤其是PR階段,與PR相比,綜合階段的腳本就簡單太多了。

為了實現(xiàn)流片,當時從零開始搭了從RTL一直到GDS還有signoff、DFT...的完整flow,中間曾發(fā)現(xiàn)過一些非常Critical的Flow bug或者工藝上一些非常值得注意的點,感覺非常嚇人,因為這些很可能導致芯片變成磚頭,幾十萬的流片費很可能就打水漂了。

個人覺得沒有Bug的Flow是不可能存在的,無非是它的影響大小的問題,所幸的是當時的流片都成功了。雖然基于當時開發(fā)的Flow設計出的芯片流片測試得到的結(jié)果是成功的,可是隨著認知的深入,發(fā)現(xiàn)其實之前研究生階段開發(fā)的Flow還是有一些問題的,也有很多可以優(yōu)化的空間,比如可以進一步提高Flow的可重用性以及靈活性。再比如Signoff的時候都應該Check哪些東西(非常關(guān)鍵),這些內(nèi)容在來了Nvidia之后,發(fā)現(xiàn)需要Check的東西蠻多的,當時研究生的時候signoff的內(nèi)容不夠完整。

尤其是signoff的時候一些input file的準確性如何去保證,這個非常關(guān)鍵,因為如果input file本身就存在一些問題的話,那么你signoff的結(jié)果即使是PASS的,那么也是沒有意義的。之前公司里面也發(fā)現(xiàn)了一個會影響RC / Timing signoff的Bug,它并沒有被其他任何的signoff Check所抓出來,因此感覺問題非常恐怖,深感后端需要注意的東西非常多,一定要小心,多持懷疑態(tài)度!!。

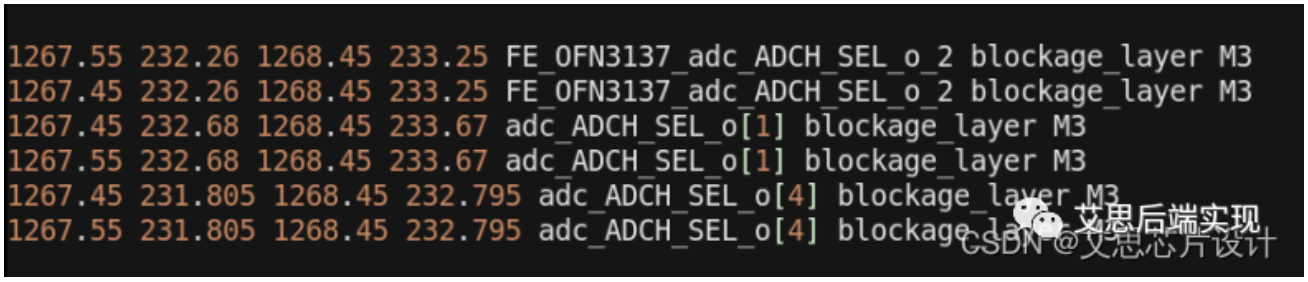

另外,在研究生的時候,也有發(fā)現(xiàn)Foundary提供的某些輸入文件之間不是特別的Match(其實可以寫一些腳本來自動check),這里分享一個StarRC跑LEF DEF flow的時候遇到的一個例子以及Debug的步驟與經(jīng)驗。

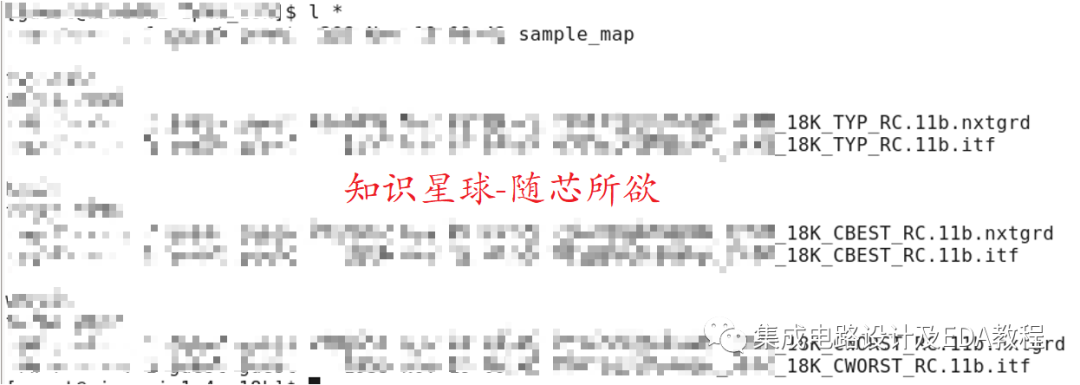

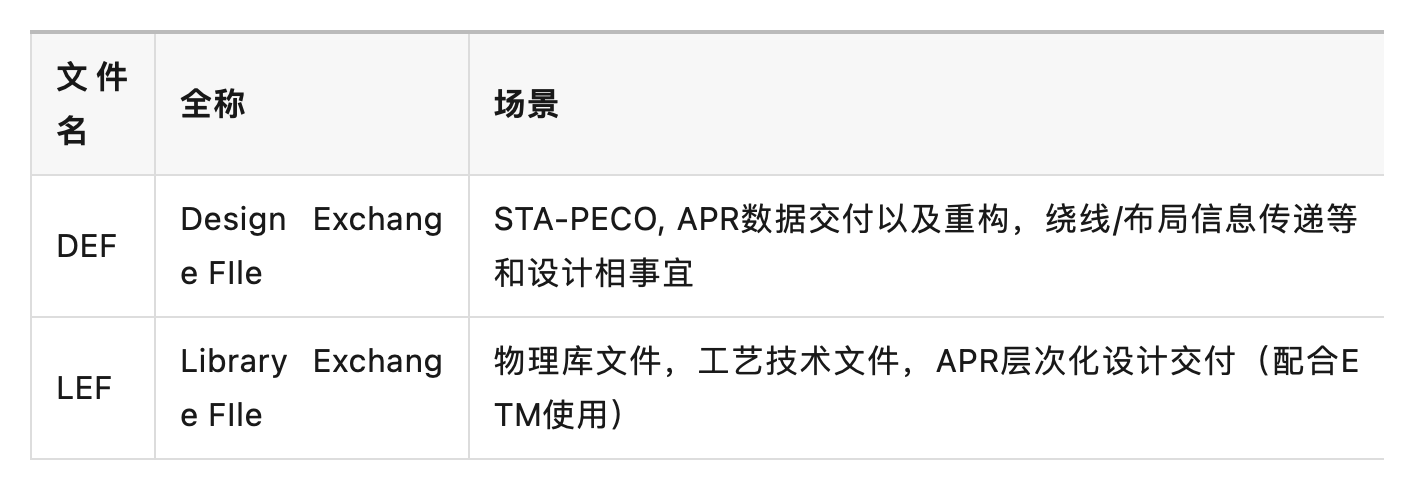

Foundary提供的RC提取文件有以下幾個:

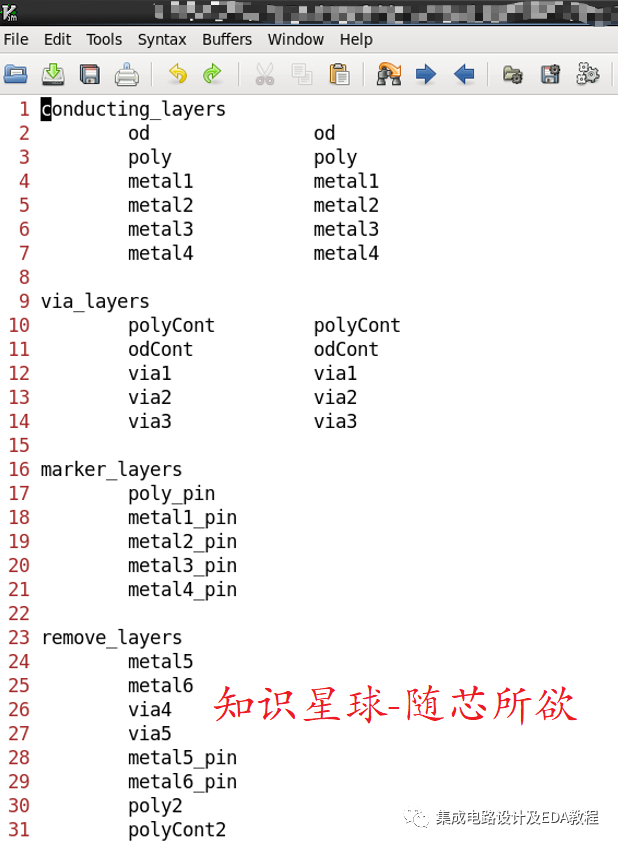

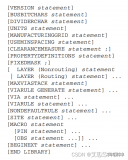

Sample_map文件內(nèi)容如下:

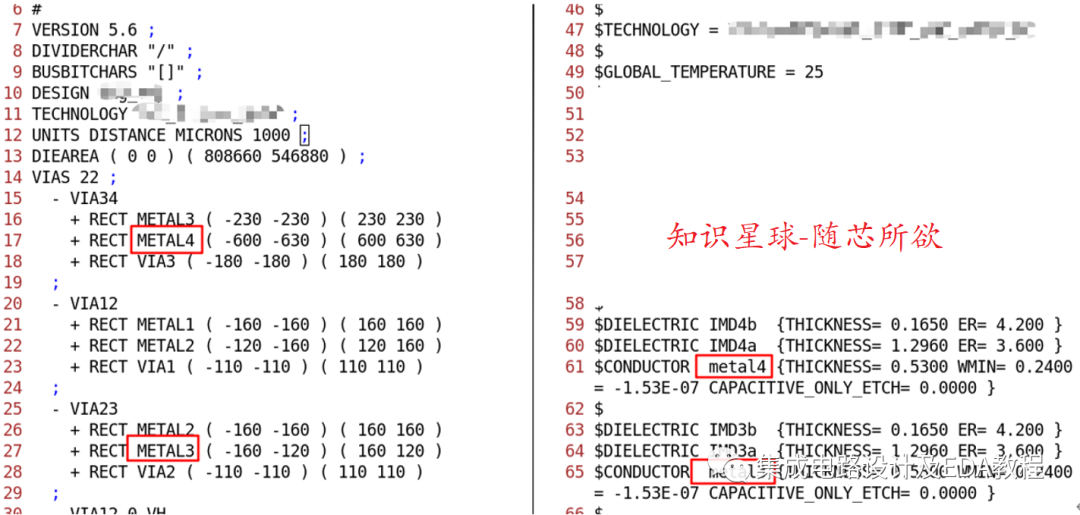

DEF文件和nxtgrd文件如下:

顯然是不能用上面的那個Mapping file的。

而上面那個Mapping file是給itf2tluplus轉(zhuǎn)換用的!!!

那么StarRC的這個Mapping file應該怎么寫呢?

審核編輯:劉清

-

DEF

+關(guān)注

關(guān)注

0文章

13瀏覽量

6235 -

StarRC

+關(guān)注

關(guān)注

0文章

7瀏覽量

3453

原文標題:StarRC LEF DEF flow錯誤Debug經(jīng)驗分享

文章出處:【微信號:集成電路設計及EDA教程,微信公眾號:集成電路設計及EDA教程】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

debug時候發(fā)生錯誤怎么解決?

支持MC33662LEF的通信收發(fā)器

請教一下大神StarRC怎么去設置多線程啊?

STM32CAN 驅(qū)動

STM32 Debug無法添加斷點的解決方法

從大設計到更大的設計,StarRC“大”有可為

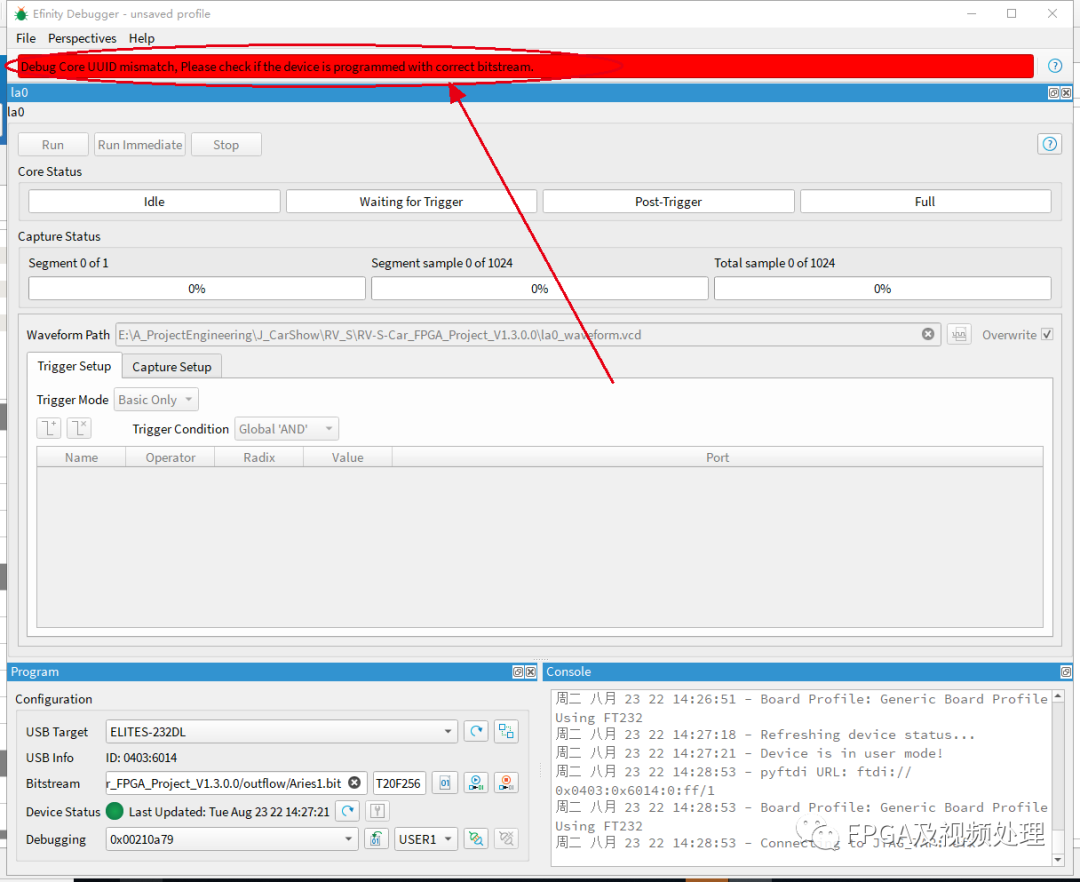

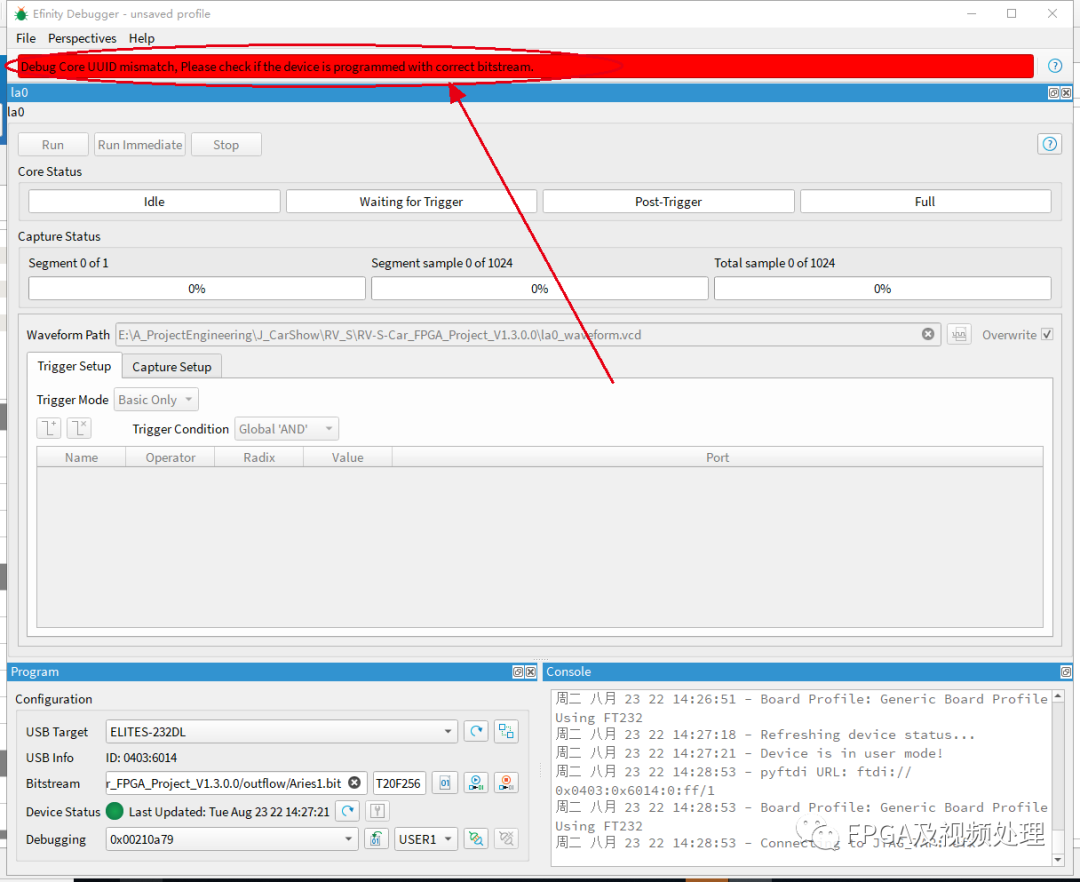

Debug Core UUID mismatch案例總結(jié)

Efinity在Debug時會出現(xiàn)UUID mismatch錯誤案例分享

芯片設計中的LEF文件淺析

淺析芯片設計中的LEF文件

配置PR的FF flow出現(xiàn)的錯誤分析

StarRC LEF DEF flow錯誤Debug經(jīng)驗分享

StarRC LEF DEF flow錯誤Debug經(jīng)驗分享

評論