在硬件開發過程中,涉及高速時鐘或者數據接口時,均會遇到LVDS(Low voltage differential signaling)這種技術接口。引用“百度百科”文獻:

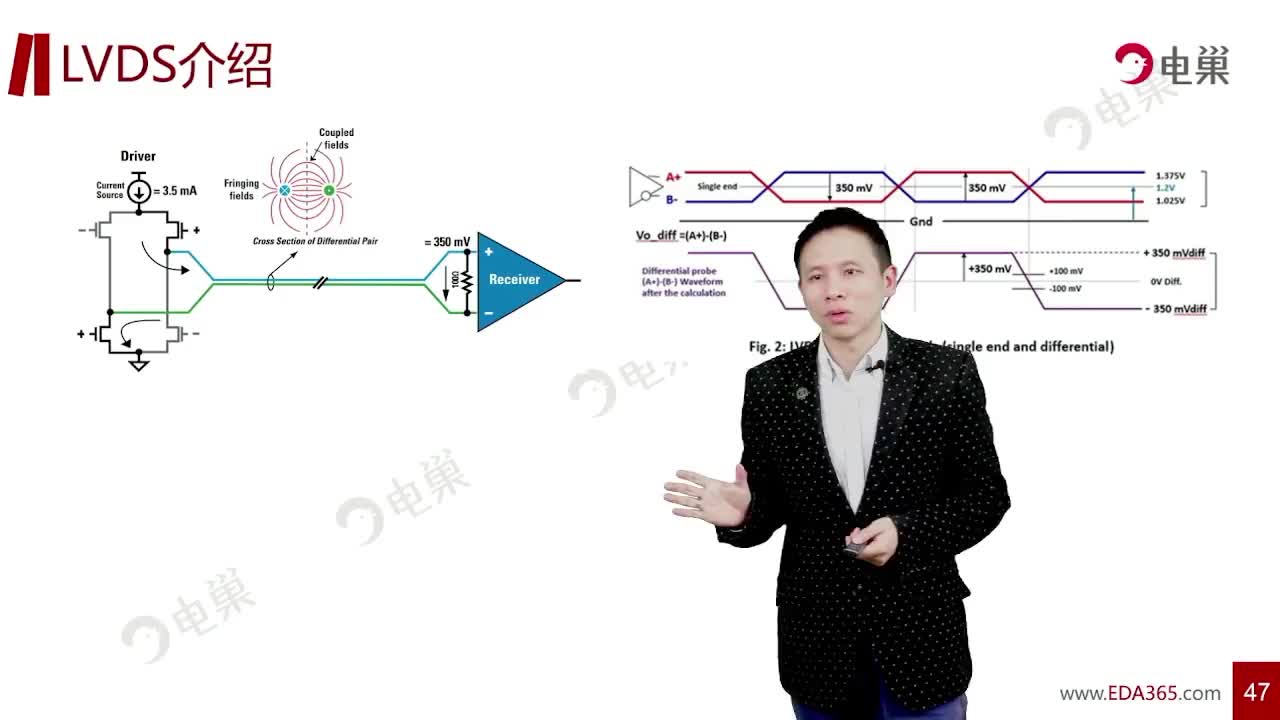

LVDS(Low Voltage Differential Signaling)是一種低振幅差分信號技術。它使用幅度非常低的信號(約350mV)通過一對差分PCB走線或平衡電纜傳輸數據。它能以高達數千Mbps的速度傳送串行數據。由于電壓信號幅度較低,而且采用恒流源模式驅動,故只產生極低的噪聲,消耗非常小的功率,甚至不論頻率高低功耗都幾乎不變。此外,由于LVDS以差分方式傳送數據,所以不易受共模噪音影響。

1.硬件功能拓撲介紹

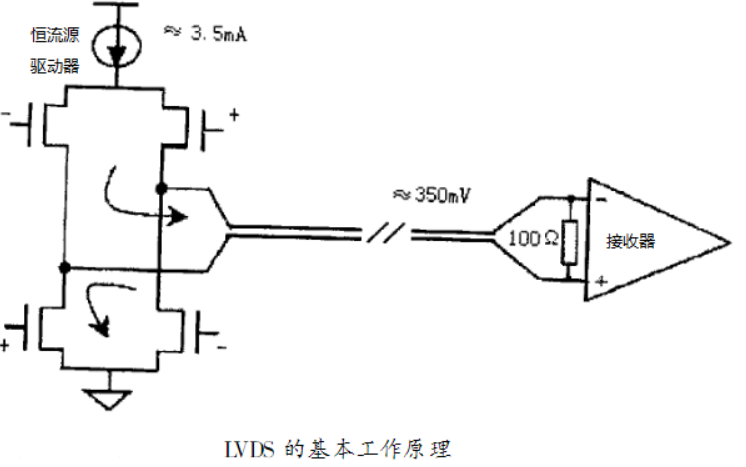

通過發送端驅動3.5mA的穩定電流電源,在100Ω終端時以350mV低振幅的差動信號來高速傳送數據。各半導體廠商獨有處理后,可以完成3Gbit/秒左右的高速傳輸速度。但是工程上認為1G已經是它的極限了。

2.信號傳輸波形曲線

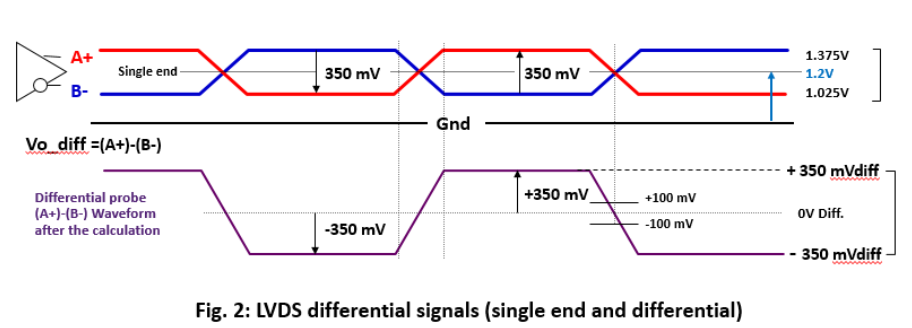

如下,A+、B-為單端輸出信號,Vo_diff差分信號。共模偏置電壓為1.2V,單端信號輸出為以1.2V共模偏置電壓為中心點上下350mv擺動,表現在差分信號時為以0電平為中心點,上下700mv擺動。

LVDS信號波形

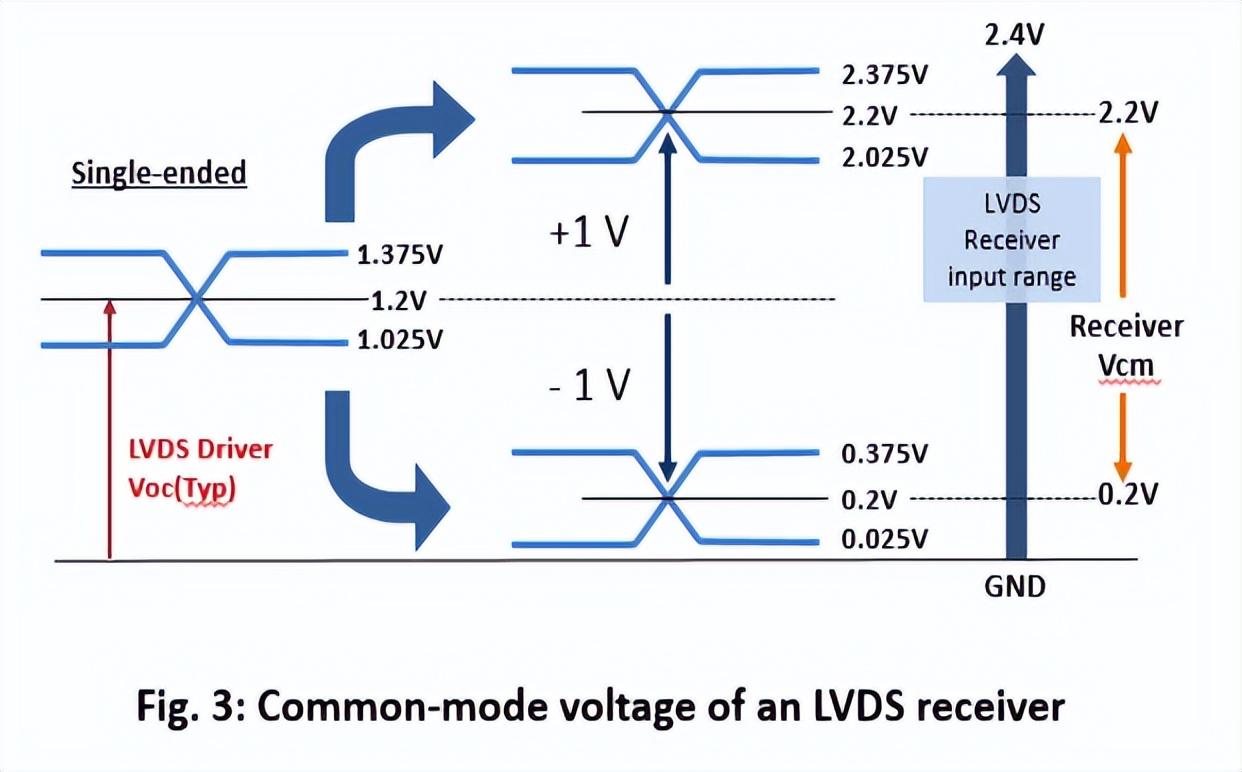

其中接收端共模偏置電壓范圍交寬泛如下:0.2-2.2V,當然根據接收端芯片不同,這個地方再特殊分析。

共模偏置電壓

3.LVDS耦合方式介紹

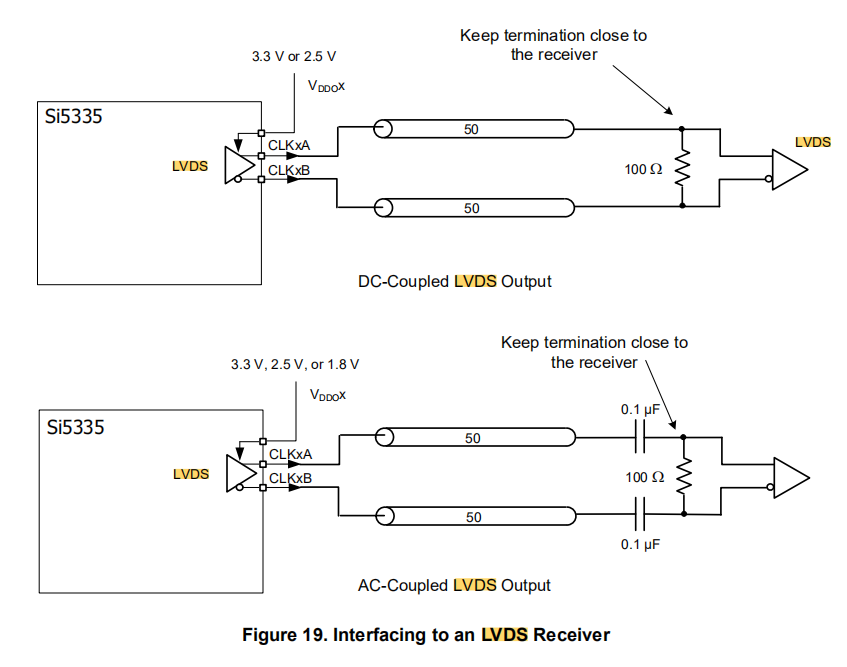

以SI5335為例,介紹LVDS耦合方式,DC與AC耦合如下,直流耦合時,在接收端端接100Ω電阻,傳輸路徑50Ω特性阻抗。

交流耦合時,通過0.1uf電容耦合后在接收端端接100Ω電阻,傳輸路徑50Ω特性阻抗。

LVDS 耦合方式

-

pcb

+關注

關注

4317文章

23004瀏覽量

396253 -

接口

+關注

關注

33文章

8497瀏覽量

150834 -

lvds

+關注

關注

2文章

1036瀏覽量

65703 -

差分信號

+關注

關注

3文章

367瀏覽量

27649 -

耦合方式

+關注

關注

0文章

10瀏覽量

7911

發布評論請先 登錄

相關推薦

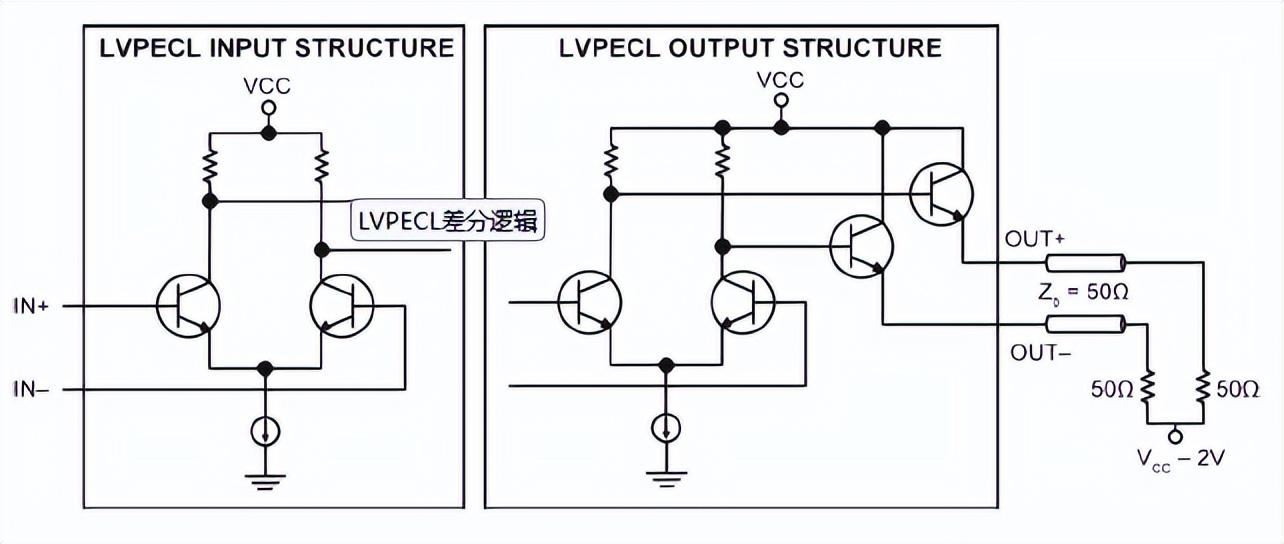

淺談LVDS、CML、LVPECL三種差分邏輯電平之間的互連

LMK00725是否支持LVDS或者LVPECL的差分交流耦合輸入呢?

用MLF1608C150MT000電容實現LVDS連接交流耦合的設計分析

用NRA335M16R8電容實現LVDS連接交流耦合的設計分析

交流耦合的優點

耦合電容的原理及耦合方式

多級放大電路耦合方式的特點是什么

多級放大電路常見的耦合方式有哪些

LMK時鐘family LVDS輸出交流耦合設計注意事項

LVDS耦合方式介紹

LVDS耦合方式介紹

評論